Processador

Fluxo de Dados e Controle

1998 Morgan Kaufmann Publishers

1

O processador: Fluxo de Dados & Controle

•

•

Estamos prontos para realizarmos uma implementação do MIPS

Simplificada para conter somente:

– Instruções de referência à memória: lw, sw

– Instruções aritméticas e lógicas: add, sub, and, or, slt

– Instruções de fluxo de controle: beq, j

•

Implementação genérica:

– usar o contador de programa (PC) para fornecer o endereço da

instrução

– Ler a instrução da memória

– ler registradores

– Usar a instrução para decidir exatamente o que fazer

•

Todas as instruções usam a ALU após a leitura dos registradores

Por que? Referência a memória?Aritmética? Fluxo de

controle?

1998 Morgan Kaufmann Publishers

2

Mais detalhes sobre a Implementação

•

Resumo / Vista Simplificada:

Data

Register #

PC

Address

Instruction

memory

Instruction

Registers

ALU

Address

Register #

Data

memory

Register #

Data

Dois tipos de unidades funcionais:

– Elementos que operam sobre dados (combinacional)

– Elementos que contêm estado (sequencial)

1998 Morgan Kaufmann Publishers

3

Elementos de Estado

•

•

Sem clock vs. com clock

Clocks são usados em lógica síncrona

– como um elemento que contem estado pode ser atualizado?

Borda de descida

Tempo de ciclo

Borda de subida

1998 Morgan Kaufmann Publishers

4

preliminares

Número ímpar de inversores em anel

Número par de inversores em anel

1998 Morgan Kaufmann Publishers

5

Um elemento de estado sem clock

•

O retentor (latch) set-reset

– A saída depende das entradas atuais e também das entradas

passadas

R

Q

S

R

Q

S

Q

S

Q

R

Q

1998 Morgan Kaufmann Publishers

6

Latch D e Flip-flop D

•

A saída é igual ao valor armazenado no elemento

(não é necessário pedir permissão para ver o valor)

•

A mudança de estado (valor) é baseada no clock

•

Latch D: sempre que as entradas mudam, e o clock é acionado

•

Flip-flop D: o estado muda somente na borda do clock

(edge-triggered)

1998 Morgan Kaufmann Publishers

7

Latch D

•

Duas entradas:

– O valor do dado a ser armazenado (D)

– O sinal de clock (C) indicando quando ler & escrever D

Duas saídas:

– O valor do estado interno (Q) e o seu complemento

•

C

Q

D

_

Q

C

D

Q

D

Q

C

Q

1998 Morgan Kaufmann Publishers

8

flip-flop D

•

A saída somente muda na borda do clock

D

D

C

D

latch

Q

D

Q

D

latch _

C

Q

Q

D

_

Q

C

C

Q

D

Q

C

Q

1998 Morgan Kaufmann Publishers

9

Nossa Implementação

•

•

Uma metodologia usando borda para o disparo ( “trigger”)

Execução típica:

– Ler conteúdo de certos elementos de estado,

– Enviar valores através de alguma lógica combinacional

– Escrever resultados a um ou mais elementos de estado

State

element

1

Combinational logic

State

element

2

Clock cycle

1998 Morgan Kaufmann Publishers

10

Banco de Registradores (Register file)

•

Construido usando D flip-flops

Read register

number 1

Read register

number 1

Register 0

Register 1

Register n – 1

M

u

x

Read data 1

Read

data 1

Read register

number 2

Register file

Write

register

Register n

Read register

number 2

Write

data

M

u

x

Read

data 2

Write

Read data 2

1998 Morgan Kaufmann Publishers

11

Banco de Registradores

•

Nota: ainda usamos o clock real para determinar quando escrever

Write

0

Register number

C

Register 0

1

D

n-to-1

decoder

C

n– 1

Register 1

D

n

C

Register n – 1

D

C

Register n

Register data

D

1998 Morgan Kaufmann Publishers

12

Implementação simples

•

Inclui as unidades funcionais que necessitamos para as instruções

Instruction

address

PC

Instruction

Add Sum

MemWrite

Instruction

memory

Address

a. Instruction memory

5

Register

numbers

5

5

Data

b. Program counter

Write

data

3

Read

register 1

Read

register 2

Registers

Write

register

Write

data

c. Adder

ALU control

Read

data 1

Read

data

Data

memory

Sign

extend

32

MemRead

a. Data memory unit

Data

16

b. Sign-extension unit

Zero

ALU ALU

result

Read

data 2

RegWrite

a. Registers

b. ALU

1998 Morgan Kaufmann Publishers

13

multiplexador

•

Seleciona uma das entradas para a saída, baseado numa entrada de

controle

S

A

0

B

1

mux de 2-entradas A e B

e controle S

C

S

S

2

A

B

C

D

2

0

1

2

3

C

A

B

C

D

01

10

10

C

mux de 4 entradas

11

1998 Morgan Kaufmann Publishers

14

ALU

Operando A

Flag de resultado zero

resultado

Operando B

1998 Morgan Kaufmann Publishers

15

ALU de 32 bits

Bnegate

Operation

Seleção

a0

b0

CarryIn

ALU0

Less

CarryOut

Result0

a1

b1

0

CarryIn

ALU1

Less

CarryOut

Result1

a2

b2

0

CarryIn

ALU2

Less

CarryOut

Result2

a31

b31

0

CarryIn

ALU31

Less

a

ALU

32

result

32

b

Zero

32

Linhas de controle:

000

001

010

110

111

=

=

=

=

=

and

or

add

subtract

slt

Result31

Set

Overflow

1998 Morgan Kaufmann Publishers

16

Convertendo um número de n bits em números de mais de n bits

Um dado imediato de 16 bits do MIPS é

convertido para 32 bits em aritmética

Copiar o bit mais significativo (o bit de

sinal) para outros bits

0010 -> 0000 0010

1010 -> 1111 1010

"sign extension"

1998 Morgan Kaufmann Publishers

17

Memória de instruções

endereço

de 32 bits

pelo PC

instrução

de 32 bits

1998 Morgan Kaufmann Publishers

18

Memória de dados

Para leitura: deve fornecer

o endereço (Address) e acionar o

controle de leitura (MemRead=1)

Para escrita deve fornecer o

endereço (Address), o dado

a ser escrito no (Writedata) e

acionar o controle de escrita

(MemWrite=1)

1998 Morgan Kaufmann Publishers

19

Contador de programa

endereço da

próxima

de instrução

endereço da instrução

corrente

Quando é sequencial é o endereço da instrução corrente

adicionado de 4 (memória de instruções constituída

de bytes)

1998 Morgan Kaufmann Publishers

20

Construindo o Fluxo de Dados

•

Usar os multiplexadores para juntar os elementos

PCSrc

M

u

x

Add

Add ALU

result

4

Shift

left 2

PC

Read

address

Instruction

Instruction

memory

Registers

Read

register 1

Read

Read

data 1

register 2

Write

register

Write

data

RegWrite

16

ALUSrc

Read

data 2

Sign

extend

M

u

x

3

ALU operation

Zero

ALU ALU

result

MemWrite

MemtoReg

Address

Read

data

Data

memory

Write

data

M

u

x

32

MemRead

1998 Morgan Kaufmann Publishers

21

Controle

•

Selecionar as operações para executar (ALU, leitura/escrita, etc.)

•

Controlar o fluxo de dados (entradas para o multiplexador)

•

A informação vem de 32 bits da instrução

•

Exemplo:

add $8, $17, $18

•

Formato de Instrução:

000000

10001

10010

01000

op

rs

rt

rd

00000 100000

shamt

funct

Operação da ALU baseada no tipo de instrução e código da função

1998 Morgan Kaufmann Publishers

22

Controle

•

•

•

P.ex., o que a ALU faz para essa instrução

Example: lw $1, 100($2)

35

2

1

op

rs

rt

16 bit offset

Entrada de controle da ALU

000

001

010

110

111

•

100

AND

OR

add

subtract

set-on-less-than

Por que o código da subtração é 110 e não 011?

1998 Morgan Kaufmann Publishers

23

Controle

•

Deve descrever o hardware para computar a entrada de controle da

ALU de 3-bit

– Dado o tipo de instrução

00 = lw, sw

ALUOp

01 = beq,

Computado do tipo de instrução

10 = aritmética

– Código de função para aritmética

•

Descreve usando uma tabela verdade (que pode ser convertido em

ALUOp

Funct field

Operation

portas):

ALUOp1 ALUOp0 F5 F4

0

0

X X

0

1

X X

1

0

X X

1

0

X X

1

0

X X

1

0

X X

1

0

X X

F3

X

X

0

0

0

0

1

F2

X

X

0

0

1

1

0

F1

X

X

0

1

0

0

1

F0

X

X

0

0

0

1

0

010

110

010

110

000

001

111

1998 Morgan Kaufmann Publishers

24

Controle

0

M

u

x

Add

Add

4

Instruction [31– 26]

Control

Instruction [25– 21]

PC

Read

address

Instruction

memory

Instruction [15– 11]

1

Shift

left 2

RegDst

Branch

MemRead

MemtoReg

ALUOp

MemWrite

ALUSrc

RegWrite

Read

register 1

Instruction [20– 16]

Instruction

[31– 0]

ALU

result

0

M

u

x

1

Read

data 1

Read

register 2

Registers Read

Write

data 2

register

0

M

u

x

1

Write

data

Zero

ALU ALU

result

Address

Write

data

Instruction [15– 0]

16

Sign

extend

Read

data

Data

memory

1

M

u

x

0

32

ALU

control

Instruction [5– 0]

Memto- Reg Mem Mem

Instruction RegDst ALUSrc

Reg

Write Read Write Branch ALUOp1 ALUp0

R-format

1

0

0

1

0

0

0

1

0

lw

0

1

1

1

1

0

0

0

0

sw

X

1

X

0

0

1

0

0

0

beq

X

0

X

0

0

0

1

0

1

1998 Morgan Kaufmann Publishers

25

Controle

•

Lógica combinacional simples (tabela verdade)

Inputs

Op5

Op4

Op3

Op2

ALUOp

Op1

ALU control block

Op0

ALUOp0

ALUOp1

Outputs

F3

F2

F (5– 0)

Operation2

Operation1

Operation

Iw

sw

beq

RegDst

ALUSrc

MemtoReg

F1

Operation0

F0

R-format

RegWrite

MemRead

MemWrite

Branch

ALUOp1

ALUOpO

1998 Morgan Kaufmann Publishers

26

Nossa estrutura de controle simples

•

Todas as lógicas são combinacionais

•

Esperamos estabilizar tudo, e a operação certa a ser realizada

– ALU não produz resposta certa imediatamente

– Usamos os sinais de escrita sincronizados ao clock para

determinar quando escrever

•

O tempo de ciclo é determinado pelo circuito mais moroso

State

element

1

Combinational logic

State

element

2

Clock cycle

1998 Morgan Kaufmann Publishers

27

Implementação em um ciclo

•

Calcular o tempo de ciclo assumindo atrasos desprezíveis exceto:

– Memória (2ns), ALU e somadores (2ns), acesso aos registradores

(1ns)

PCSrc

Add

ALU

Add result

4

RegWrite

Instruction [25– 21]

PC

Read

address

Instruction

[31– 0]

Instruction

memory

Instruction [20– 16]

1

M

u

Instruction [15– 11] x

0

RegDst

Instruction [15– 0]

Read

register 1

Read

register 2

Read

data 1

Read

Write

data 2

register

Write

Registers

data

16

Sign 32

extend

1

M

u

x

0

Shift

left 2

MemWrite

ALUSrc

1

M

u

x

0

ALU

control

Zero

ALU ALU

result

MemtoReg

Address

Read

data

Data

Write

memory

data

1

M

u

x

0

MemRead

Instruction [5– 0]

ALUOp

1998 Morgan Kaufmann Publishers

28

Implementação de MIPS em um único ciclo

0

M

u

x

Add

Add

4

Instruction [31– 26]

Control

Instruction [25– 21]

PC

Read

address

Instruction

memory

Instruction [15– 11]

1

Shift

left 2

RegDst

Branch

MemRead

MemtoReg

ALUOp

MemWrite

ALUSrc

RegWrite

Read

register 1

Instruction [20– 16]

Instruction

[31– 0]

ALU

result

0

M

u

x

1

Read

data 1

Read

register 2

Registers Read

Write

data 2

register

0

M

u

x

1

Write

data

Zero

ALU ALU

result

Address

Write

data

Instruction [15– 0]

16

Sign

extend

Read

data

Data

memory

1

M

u

x

0

32

ALU

control

Instruction [5– 0]

Instruction

R-format

lw

sw

beq

RegDst

1

0

X

X

ALUSrc

0

1

1

0

Memto- Reg Mem Mem

Reg

Write Read Write

0

1

0

0

1

1

1

0

X

0

0

1

X

0

0

0

Branch

0

0

0

1

ALUOp1 ALUp0

1

0

0

0

01998 Morgan0Kaufmann Publishers

0

1

29

Onde estamos?

•

•

Problemas de ciclo simples:

– E se tivéssemos instruções mais complexas como pontoflutuante?

– Devastação de área

Uma Solução:

– usar um tempo de ciclo “menor”

– Ter diferentes instruções levando diferentes números de ciclos

– Um fluxo de dados de “multiplos ciclos”:

Instruction

register

PC

Address

Data

A

Memory

Data

Register #

Instruction

or data

Memory

data

register

ALU

Registers

Register #

ALUOut

B

Register #

1998 Morgan Kaufmann Publishers

30

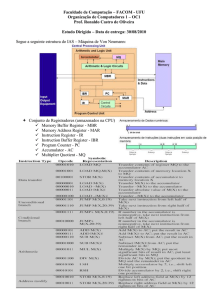

Técnica Multiciclo

•

•

•

Estaremos usando as mesmas unidades funcionais

– ALU é usada para computar o endereço e para incrementar PC

– A memória é usada para instruções e dados

Nossos sinais de controle não são determinados somente pelas

instruções

– P.ex., o que a ALU faria para uma instrução de “subtração” ?

Usamos uma máquina de estado finito para o controle

1998 Morgan Kaufmann Publishers

31

Revisão: máquinas de estado finito

•

Máquinas de estado finito:

– Um conjunto de estados e

– Função próximo estado (determinado pelo estado atual e

entrada)

– Função de saída (determinada pelo estado atual e possivelmente

entrada)

Current state

Next-state

function

Next

state

Clock

Inputs

Output

function

Outputs

– Usaremos uma máquina Moore (saída baseada somente no

estado atual)

1998 Morgan Kaufmann Publishers

32

Revisão: máquinas de estado finito

•

Exemplo:

B. 21 Um amigo gostaria de construir um olho “eletrônico” para uso em dispositivo de

segurança. O dispositivo consiste de 3 luzes alinhados, controladas por saídas Esquerda,

Central, e Direita, que, se acionadas, indicam que uma luz estaria acesa. Somente uma

luz é acionada por vez, e a luz “move” da esquerda para a direita e, então, da direita para

a esquerda, para assustar os ladrões que acreditam que os dispositivos estejam

monitorando as suas atividades. Traçar a representação gráfica para a máquina de estado

finito usada para especificar o olho eletrônico. Notar que a taxa de movimentação do

olho será controlado pela velocidade do clock (que não deveria ser excessivamente

grande) e que não existem essencialmente entradas.

1998 Morgan Kaufmann Publishers

33

Técnica multiciclo

•

•

Quebrar as instruções em passos, cada passo leva um ciclo

– Balancear a quantidade de trabalhos a realizar

– Restringir cada ciclo para usar somente uma unidade funcional

No fim de um ciclo

– Armazenar valores para serem usados nos ciclos posteriores

– introduzir registradores internos adicionais

PC

0

M

u

x

1

Instruction

[25– 21]

Address

Memory

MemData

Write

data

Read

Read

register 2 data 1

Registers

Write

Read

register data 2

Instruction

[20– 16]

Instruction

[15– 0]

Instruction

register

Instruction

[15– 0]

Memory

data

register

0

M

u

x

1

Read

register 1

0

M

Instruction u

x

[15– 11]

1

A

B

0

M

u

x

1

16

Sign

extend

32

ALUOut

0

4

Write

data

Zero

ALU ALU

result

1 M

u

2 x

3

Shift

left 2

1998 Morgan Kaufmann Publishers

34

Cinco passos de Execução

•

Busca da instrução (Instruction Fetch)

•

Decodificação da instrução e busca do registrador

•

Execução, Computação do endereço de memória, ou conclusão de

uma instrução de branch

•

Acesso à memória ou conclusão de uma instrução R-type

•

Passo de Write-back

INSTRUÇÕES LEVEM DE 3 - 5 CICLOS!

1998 Morgan Kaufmann Publishers

35

Passo 1: Busca da instrução (Instruction Fetch)

•

•

•

Usar o PC para a leitura da instrução e carga da mesma no registrador

de instrução (Instruction Register).

Incrementar o valor do PC por 4 e carregar o resultado no PC.

Pode ser descrito sucintamente usando RTL "Register-Transfer

Language"

IR = Memory[PC];

PC = PC + 4;

Podemos obter os valores dos sinais de controle?

Quais as vantagens de atualizar o PC neste passo?

1998 Morgan Kaufmann Publishers

36

Passo 2: Decod. da Instrução e Busca de Registradores

•

•

•

Leitura dos registradores rs e rt

Computar o endereço de branch no caso da instrução de branch

RTL:

A = Reg[IR[25-21]];

B = Reg[IR[20-16]];

ALUOut = PC + (sign-extend(IR[15-0]) << 2);

•

Estamos acionando as linhas de controle baseadas no tipo de

instrução

(a instrução está sendo "decodificada" na lógica de controle)

1998 Morgan Kaufmann Publishers

37

Passo 3 (dependente da instrução)

•

ALU está realizando uma das três funções, baseadas no tipo de

instrução

•

Referência à memória:

ALUOut = A + sign-extend(IR[15-0]);

•

R-type:

ALUOut = A op B;

•

Branch:

if (A==B) PC = ALUOut;

1998 Morgan Kaufmann Publishers

38

Passo 4 (R-type ou acesso à memória)

•

Acesso à memória através de loads e stores

MDR = Memory[ALUOut];

or

Memory[ALUOut] = B;

•

Fim das instruções R-type

Reg[IR[15-11]] = ALUOut;

A escrita é realizada no fim do ciclo, na borda

1998 Morgan Kaufmann Publishers

39

Passo Write-back

• Reg[IR[20-16]]= MDR;

E as outras instruções?

1998 Morgan Kaufmann Publishers

40

Resumo:

Step name

Instruction fetch

Action for R-type

instructions

Instruction

decode/register fetch

Action for memory-reference

Action for

instructions

branches

IR = Memory[PC]

PC = PC + 4

A = Reg [IR[25-21]]

B = Reg [IR[20-16]]

ALUOut = PC + (sign-extend (IR[15-0]) << 2)

Execution, address

computation, branch/

jump completion

ALUOut = A op B

ALUOut = A + sign-extend

(IR[15-0])

Memory access or R-type

completion

Reg [IR[15-11]] =

ALUOut

Load: MDR = Memory[ALUOut]

or

Store: Memory [ALUOut] = B

Memory read completion

if (A ==B) then

PC = ALUOut

Action for

jumps

PC = PC [31-28] II

(IR[25-0]<<2)

Load: Reg[IR[20-16]] = MDR

1998 Morgan Kaufmann Publishers

41

Questões simples

•

Quantos ciclos são necessários para o código?

Label:

•

•

lw $t2, 0($t3)

lw $t3, 4($t3)

beq $t2, $t3, Label

add $t5, $t2, $t3

sw $t5, 8($t3)

...

#assume not

O que acontece durante o oitavo ciclo de execução?

Em que ciclo a soma de $t2 e $t3 é realizada?

1998 Morgan Kaufmann Publishers

42

Implementando o Controle

•

Os sinais de controle são dependentes de:

– Que instrução está sendo executada

– Que passo está sendo realizada

•

Usar as informações acumuladas para especificar uma máquina de

estado finito

– Especificar uma máquina de estado finito graficamente, ou

– usar microprogramação

1998 Morgan Kaufmann Publishers

43

Especificação da FSM

Instruction decode/

register fetch

Instruction fetch

(Op

2

or

W')

= 'L

(Op

W

= 'S

Branch

completion

=

')

W

'S

MemRead

IorD = 1

R-type completion

7

5

3

MemWrite

IorD = 1

Write-back step

4

RegDst = 0

RegWrite

MemtoReg = 1

Quantos bits de estado são necessários?

'B

EQ

ALUSrcA = 1

ALUSrcB = 00

ALUOp = 01

PCWriteCond

PCSource = 01

p

Memory

access

RegDst = 1

RegWrite

MemtoReg = 0

Jump

completion

9

8

6

ALUSrcA =1

ALUSrcB = 00

ALUOp = 10

Memory

access

')

e)

-t yp

R

=

(O

(Op = 'LW')

(Op

')

Execution

ALUSrcA = 1

ALUSrcB = 10

ALUOp = 00

•

ALUSrcA = 0

ALUSrcB = 11

ALUOp = 00

(Op = 'J')

Memory address

computation

1

=

Start

MemRead

ALUSrcA = 0

IorD = 0

IRWrite

ALUSrcB = 01

ALUOp = 00

PCWrite

PCSource = 00

(O

p

0

PCWrite

PCSource = 10

Máquina de estado finito para controle

Implementação:

PCWrite

PCWriteCond

IorD

MemRead

MemWrite

IRWrite

Control logic

MemtoReg

PCSource

ALUOp

Outputs

ALUSrcB

ALUSrcA

RegWrite

RegDst

NS3

NS2

NS1

NS0

Instruction register

opcode field

S0

S1

S2

S3

Op0

Op1

Op2

Op3

Op4

Inputs

Op5

•

State register

1998 Morgan Kaufmann Publishers

45

Implementação em PLA

Op5

Op4

Op3

Op2

Op1

Op0

S3

S2

S1

S0

PCWrite

PCWriteCond

IorD

MemRead

MemWrite

IRWrite

MemtoReg

PCSource1

PCSource0

ALUOp1

ALUOp0

ALUSrcB1

ALUSrcB0

ALUSrcA

RegWrite

RegDst

NS3

NS2

NS1

NS0

1998 Morgan Kaufmann Publishers

46

Implementação em ROM

•

•

ROM = "Read Only Memory"

– Os valores das palavras de memória são fixas ao longo do tempo

Uma ROM pode ser usada para implementar uma tabela verdade

– Se o endereço é de m-bits, podemos endereçar 2m entradas na

ROM.

– Nossas saídas são os bits de dados onde o endereço aponta.

m

n

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

1

1

0

0

0

0

0

1

1

0

0

0

1

1

1

0

0

0

0

0

1

1

1

0

0

0

0

1

0

1

m é a “altura", e n é a “largura"

1998 Morgan Kaufmann Publishers

47

Implementação em ROM

•

•

•

Quantas entradas existem?

6 bits para opcode, 4 bits para estado = 10 linhas de endereço

(i.e., 210 = 1024 endereços diferentes)

Quantas saídas existem?

16 saídas de controle do fluxo de dados, 4 bits de estado = 20

saídas

ROM é 210 x 20 = 20K bits

(um tamanho não usual)

1998 Morgan Kaufmann Publishers

48

ROM vs PLA

•

Quebrar a tabela em duas partes

— 4 bits de estado fornecem as 16 saídas, 24 x 16 bits of ROM

— 10 bits fornecem o endereço para os 4 bits de estado

seguinte, 210 x 4 bits of ROM

— Total: 4.3K bits de ROM

•

PLA é menor

— pode compartilhar termos produtos

— são necessárias somente entradas que produzem saída ativa

— pode levar em conta os irrelevantes

•

O tamanho é (#entradas #termos-produto) + (#saídas #termosproduto)

Para esse exemplo = (10x17)+(20x17) = 460 células PLA

•

Células PLA são de tamanho aproximado de uma célula de ROM

(levemente maior)

1998 Morgan Kaufmann Publishers

49

Um outro estilo de Implementação

Instruções complexas: o “estado seguinte" é quase sempre o estado

atual + 1

Control unit

PLA or ROM

Outputs

Input

PCWrite

PCWriteCond

IorD

MemRead

MemWrite

IRWrite

BWrite

MemtoReg

PCSource

ALUOp

ALUSrcB

ALUSrcA

RegWrite

RegDst

AddrCtl

1

State

Adder

Address select logic

Op[5– 0]

•

Instruction register

opcode field

1998 Morgan Kaufmann Publishers

50

Detalhes

Op

000000

000010

000100

100011

101011

Dispatch ROM 1

Opcode name

R-format

jmp

beq

lw

sw

Value

0110

1001

1000

0010

0010

Dispatch ROM 2

Opcode name

lw

sw

Op

100011

101011

Value

0011

0101

PLA or ROM

1

State

Adder

3

Mux

2 1

AddrCtl

0

0

Dispatch ROM 2

Dispatch ROM 1

Op

Address select logic

Instruction register

opcode field

State number

0

1

2

3

4

5

6

7

8

9

Address-control action

Use incremented state

Use dispatch ROM 1

Use dispatch ROM 2

Use incremented state

Replace state number by 0

Replace state number by 0

Use incremented state

Replace state number by 0

Replace state number by 0

Replace state number by 0

Value of AddrCtl

3

1

2

3

0

0

3

0

0

0

1998 Morgan Kaufmann Publishers

51

Microprogramação

Control unit

Microcode memory

Outputs

Input

PCWrite

PCWriteCond

IorD

MemRead

MemWrite

IRWrite

BWrite

MemtoReg

PCSource

ALUOp

ALUSrcB

ALUSrcA

RegWrite

RegDst

AddrCtl

Datapath

1

Microprogram counter

Adder

Op[5– 0]

Address select logic

Instruction register

opcode field

•

O que são “microinstruções” ?

1998 Morgan Kaufmann Publishers

52

Microprogramação

•

Uma metodologia de especificação

– Apropriado se centenas de opcodes, modos, ciclos, etc.

– sinais especificados simbolicamente usando microinstruções

Label

Fetch

Mem1

LW2

ALU

control

Add

Add

Add

SRC1

PC

PC

A

Register

control

SRC2

4

Extshft Read

Extend

PCWrite

Memory

control

Read PC ALU

Read ALU

Write MDR

SW2

Rformat1 Func code A

Write ALU

B

Write ALU

BEQ1

JUMP1

•

•

Subt

A

B

ALUOut-cond

Jump address

Sequencing

Seq

Dispatch 1

Dispatch 2

Seq

Fetch

Fetch

Seq

Fetch

Fetch

Fetch

Duas implementações da mesma arquitetura tem o mesmo microcódigo?

O que faria um microassembler?

1998 Morgan Kaufmann Publishers

53

Formato de Microinstrução

Field name

ALU control

SRC1

SRC2

Value

Add

Subt

Func code

PC

A

B

4

Extend

Extshft

Read

ALUOp = 10

ALUSrcA = 0

ALUSrcA = 1

ALUSrcB = 00

ALUSrcB = 01

ALUSrcB = 10

ALUSrcB = 11

Write ALU

RegWrite,

RegDst = 1,

MemtoReg = 0

RegWrite,

RegDst = 0,

MemtoReg = 1

MemRead,

lorD = 0

MemRead,

lorD = 1

MemWrite,

lorD = 1

PCSource = 00

PCWrite

PCSource = 01,

PCWriteCond

PCSource = 10,

PCWrite

AddrCtl = 11

AddrCtl = 00

AddrCtl = 01

AddrCtl = 10

Register

control

Write MDR

Read PC

Memory

Read ALU

Write ALU

ALU

PC write control

ALUOut-cond

jump address

Sequencing

Signals active

ALUOp = 00

ALUOp = 01

Seq

Fetch

Dispatch 1

Dispatch 2

Comment

Cause the ALU to add.

Cause the ALU to subtract; this implements the compare for

branches.

Use the instruction's function code to determine ALU control.

Use the PC as the first ALU input.

Register A is the first ALU input.

Register B is the second ALU input.

Use 4 as the second ALU input.

Use output of the sign extension unit as the second ALU input.

Use the output of the shift-by-two unit as the second ALU input.

Read two registers using the rs and rt fields of the IR as the register

numbers and putting the data into registers A and B.

Write a register using the rd field of the IR as the register number and

the contents of the ALUOut as the data.

Write a register using the rt field of the IR as the register number and

the contents of the MDR as the data.

Read memory using the PC as address; write result into IR (and

the MDR).

Read memory using the ALUOut as address; write result into MDR.

Write memory using the ALUOut as address, contents of B as the

data.

Write the output of the ALU into the PC.

If the Zero output of the ALU is active, write the PC with the contents

of the register ALUOut.

Write the PC with the jump address from the instruction.

Choose the next microinstruction sequentially.

Go to the first microinstruction to begin a new instruction.

Dispatch using the ROM 1.

Dispatch using the ROM 2.

Codificação Maximal vs. Minimal

•

Sem codificação:

– 1 bit para cada operação do fluxo de dados

– rápido, requer mais memória (lógica)

– Usada para Vax 780 — 400K de memória!

•

Muita codificação:

– Enviar as microinstruções através de lógicas para a obtenção

dos sinais de controle

– Usa menos memória, lenta

•

Contexto histórico do CISC:

– Muita lógica a ser colocada num único chip

– Usar uma ROM (ou mesmo RAM) para manter o microcódigo

– Fácil para adicionar novas instruções

1998 Morgan Kaufmann Publishers

55

Microcódigo: compromisso (Trade-offs)

•

Vantagens da especificação:

– Fácil de projetar e escrever

– Projetar a arquitetura e o microcódigo simultaneamente

•

Vantagens da Implementação (off-chip ROM)

– Fácil de mudar se os valores estão em memória

– Pode emular outras arquiteturas

– Pode fazer uso de registradores internos

•

Desvantagens da Implementação, MAIS LENTO que:

– O controle seja implementado no mesmo chip como o

processador

– ROM não é mais rápido que RAM

– Quando não existe necessidade para fazer mudanças

1998 Morgan Kaufmann Publishers

56

Exceções e Interrupções

Exceções e interrupções – são eventos diferentes de branches

e jumps que mudam o fluxo normal de execução de instruções.

Exceção – evento inesperado que causa uma mudança no fluxo

de controle, que tem origem dentro do processador

(por ex. overflow aritmético)

Interrupção –evento inesperado que causa uma mudança inesperada

no fluxo de controle, que tem origem fora do processador.

(por ex. digitação de um caracter no teclado)

Observação: arquitetura 80x86 (ou IA-32, Intel) usa o termo

Interrupção para todos esses eventos.

1998 Morgan Kaufmann Publishers

57

Exceções e interrupções

Exemplos:

TIPO DE EVENTO

ORIGEM

TERMINOLOGIA

MIPS

Solicitação de

dispositivo de E/S

externa

interrupção

Chamada do SO pelo

programa de usuário

interna

exceção

Overflow aritmético

interna

exceção

Uso de uma

instrução indefinida

interna

exceção

Mal funcionamento

do hardware

ambas

exceção ou

interrupção

1998 Morgan Kaufmann Publishers

58

Como manipular exceções e interrupções

•

Ações básicas a serem tomadas pela máquina quando ocorre uma

exceção :

1) salvar o endereço da instrução ofendida (instrução atual) num

registrador especial EPC (Exception Program Counter).

2) transferir o controle (atualizar o conteúdo de PC) para um

endereço específico, que possibilite ao computador executar a rotina

de tratamento de exceção.

•

ROTINA DE TRATAMENTO DE EXCEÇÃO: depende do tipo de

exceção, por exemplo, reportar ao usuário que ocorreu um erro de

overflow.

•

Ações a serem tomadas após a execução do tratamento de exceção:

- Depende do tipo de exceção: por ex. pode encerrar, ou continuar

executanto, o programa que estava executando antes da

exceção.

- O EPC é usado para determinar o endereço de reinício da

execução.

1998 Morgan Kaufmann Publishers

59

Como saber a causa da exceção

• Para o computador manipular uma exceção, ele deve

conhecer a razão da exceção.

• A razão pode ser obtida de duas formas:

1) usar o registrador de status (cause register) que indica a

razão

2) usar interrupção vetorizada, caso em que o endereço de

desvio para executar a exceção é determinado pela causa

da exceção

1998 Morgan Kaufmann Publishers

60

Implementação de exceção no MIPS

• Implementação de duas exceções:

1) overflow aritmético

2) instrução indefinida

A causa é determinada pelo valor do registrador CAUSE de 32 bits:

CAUSE = 00 00 00 00 (em hexa), overflow aritmético

CAUSE = 00 00 00 01 (em hexa), instrução indefinida

O endereço da instrução ofendida é guardada em EPC

O endereço de desvio para o início da execução da rotina de

tratamento de exceção é dado por C0 00 00 00 (em hexa).

1998 Morgan Kaufmann Publishers

61

Alterações no fluxo de dados

PCSource

EPCWrite

ALU

PC+4

ALUOut

ALUOut

EPC

JumpAddr

C0 00 00 00

IntCause

0

0

1

2

PC

3

CauseWrite

Registradores adicionais:

EPC, Cause

0

Cause

1

1

Sinais de controle adicionais:

EPCWrite, CauseWrite,

IntCause

62

1998 Morgan Kaufmann Publishers

Alteração na máquina de estado

1

lw o

u sw

tipo

-R

beq

ou

jmp

s

tro

op

co

de

6

s

10

11

7

overflow

IntCause = 1

CauseWrite

ALUSrcA = 0

ALUSrcB = 01

ALUOp = 01

EPCWrite

PCWrite

PCSource = 11

IntCause=0

CauseWrite

ALUSrcA = 0

ALUSrcB = 01

ALUOp = 01

EPCWrite

PCWrite

PCSource = 11

Estado 0

Estado 0

Estado 0

1998 Morgan Kaufmann Publishers

63