Parte 5

OBS: Essas anotações são adaptações do material suplementar

(apresentações PPT) ao Livro do Hennessy e Patterson, 2ª e 3ª

Ed. e do Livro do 5ª. Ed. A parte final do material corresponde

às aulas do Prof. José Luís Güntzel, UFSC, disponível em

http://www.inf.ufsc.br/~guntzel/ine641400/ine641400.html

1

Relembrando desempenho

• Depende de 3 fatores chave:

– Número de instruções

– Tempo de ciclo de clock

– Número de clocks por instrução (CPI)

• Nesta parte do curso: princípios e técnica usados

para implementar um processador

• Apenas um subconjunto das instruções será

considerado inicialmente.

2

Estrutura interna da CPU

• Uma CPU deve:

–

–

–

–

–

Buscar instruções

Decodificar instruções

Buscar operandos/dados

Executar a instrução (processar dados/operandos)

Escrever o resultado

• Esses passos básicos fazem parte do ciclo de

busca e execução da arquitetura (aulas iniciais…)

– Outros passos podem ser incluídos neste ciclo para

cálculos de endereços de operandos, seja na fase de

busca, seja na fase de escrita.

3

Ciclo de Busca-Execução

PC

1000

1004

INSTR1

INSTR2

1000

IR

MEM

Unidade de

controle

CPU

Buscar instrução no

endereço 1000

4

Ciclo de Busca-Execução

PC

1000

1004

INSTR1

INSTR2

1000

INSTR1

IR

MEM

Armazenar

instrução

Enviar

instrução

para ser

no registradornadeUn.Controle

instrução

decodificada

Unidade de

controle

CPU

5

Ciclo de Busca-Execução

PC

1000

1004

INSTR1

INSTR2

1000

1004

INSTR1

INSTR1

IR

MEM

Unidade de

controle

CPU

Incrementar PC

6

Ciclo de Busca-Execução

PC

1000

1004

INSTR1

INSTR2

1004

INSTR2

IR

MEM

Unidade de

controle

CPU

Tudo outra vez...

7

Ciclo de Busca & Execução (Patterson & Hennessy)

instrução

Fetch

Obtém uma instrução do programa armazenado

instrução

Decode

Determine as ações e o tamanho da instruções

Operand

Fetch

Localiza e obtém os dados (operandos)

Execute

Result

Store

Next

instrução

Calcula um valor do resultado ou status

Armazena resultados na memória para uso futuro

Determina a próxima instrução

8

Na arquitetura MIPS

• Dois passos iniciais iguais para todas as instruções:

1. Enviar o PC para o endereço de memória que contém a

próxima instrução e trazê-la da memória

2. Usar os campos da instrução para identificar qual (is)

registrador(es) – 1 ou 2, dependendo da instrução

•

Próximos passos dependem da classe de instrução

a ser executada!

–

No caso do MIPS, a vantagem é que as execuções são

bastante parecidas, o que agiliza a execução

9

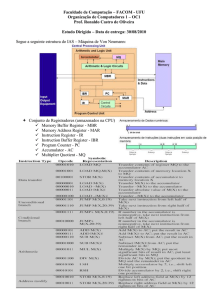

CPU – Estrutura Interna (Stallings, Cap.12)

Registers

10

CPU e Barramentos (Stallings, Cap.12)

Registers

Comunicação com outras parte via

barramentos: dados, controle, endereços

11

Arquitetura de (Hayes,1988)

Unidade Lógica e aritmética

Quociente Mult.

Acumulador

Dispositivos

de Entrada e

Saída (E/S)

Hardware LÓGICO E

ARITMÉTICO

MBR

Instruções e

dados

IBR

PC

Memória

MAR

IR

Hardware

de CONTROLE

Sinais de

controle

Principal

Endereços

Unidade de Controle

12

Visão da Arquitetura MIPS

13

Registradores

• Além da ULA e do controle, vários registradores

ocupam boa parte da estrutura da CPU

– Fornecem “espaço físico temporário” para executar instruções

• Quantidade e funções variam entre processadores

– Isto é uma das mais importantes decisões de projeto!

– Arquiteturas RISC priorizam um grande número deles.

• Estão no topo da hierarquia do sistema de memória:

são os componentes de memória “mais rápidos” e

mais “escassos” do computador

• Em termos de organização, 2 tipos:

1. Visíveis ao usuário e

2. Controle/status

14

Registradores visíveis ao usuário

• Registradores de Propósito Geral

– Variedade de funções pelo programador

– Qualquer opcode pode conter um operando armazenado

nesses registradores

– Também usados em cálculos de endereços

• Registradores de Dados

– Armazenar dados (tipos definidos no ISA)

• Registradores de Endereços

– Ex: Ponteiros de segmento, pilha, índice

• Registradores de Códigos Condicionais

– Test & set (slt), test & branch (bne, beq) e outras

instruções de desvio condicional.

15

Registradores de Uso Geral (1)

• Podem não ser “exatamente de uso geral”

– Ex: dedicados a ponto-flutuante / operações de pilha

• Seu uso pode ser restrito/especializado

• Podem ser usados por dados ou endereços

– Dados: Acumulador é um registrador “especializado” em

algumas situações

– Endereços: O endereço calculado com o valor armazenado;

acesso a segmentos de código (família x86)

• Uso-geral x especialização dos registradores

– Compromisso entre flexibilidade, tamanho das intruções,

complexidade de decodificação, etc.

– Influência sobre o ISA

16

Quantos registradores de uso geral uso?

• Algo entre 8 – 32 nas arquiteturas atuais

– Máquinas RISC, load-store podem ter centenas de

registradores

• Menos = mais referências à memória

• Mais ≠ garantia de redução de referências à memória

17

Comparação de alguns processadores (Stallings, Cap. 13)

18

Qual o tamanho de um registrador?

• Reg.endereços: Grande o suficiente para armazenar

um endereço completo

• Reg.de dados: Grande o suficiente para armazenar

uma palavra completa

• Em algumas situações é possível combinar 2

registradores de dados

– Ex. programa C:

double int a;

long int a;

• MIPS: registradores 32 bits, que combinados por

trabalhar com até 64 bits

– Multiplicação, operações ponto-flutuante, etc.

19

Registradores de Controle & Status

•

•

•

•

•

•

Arquitetura de (Hayes, 1988):

Contador de Programa (PC)

Registrador de Instrução (IR)

Registrador de Endereço de Memória (MAR)

Registrador de Buffer de Memória (MBR)

Registrador de Buffer de Instrução (IBR)

• Cada um tem uma função específica na arquitetura

proposta:

– Ex: MAR armazena o endereço da palavra de memória a

ser acessada.

20

Arquitetura de (Hayes,1988)

Unidade Lógica e aritmética

Quociente Mult.

Acumulador

Dispositivos

de Entrada e

Saída (E/S)

Hardware LÓGICO E

ARITMÉTICO

MBR

Instruções e

dados

IBR

PC

Memória

MAR

IR

Hardware

de CONTROLE

Principal

Sinais de

controle

Unidade de Controle

Endereços

21

Algumas Organizações de Registradores (Stallings, Cap.12)

22

O “Processador”: Via de dados & Controle

• Foco na implementação do MIPS

• Projeto simplificado para dar suporte às instruções:

– Referência à memória: lw, sw

– Lógicas e aritméticas: add, sub, and, or, slt

– Fluxo de controle: beq, j

• Implementação Genérica:

– Usa o contador de programa (PC) para fornecer o endereço da

instrução

– Pega a instrução na memória

– Lê e escreve registradores

– Usa campos da instrução para decidir exatamente o que fazer

• Todas as instruções usam a ALU após ler os registradores

??? referência à memória? Aritméticas? Fluxo de controle?

23

Detalhes da implementação

•

Visão Geral:

Data

PC

Address

Instruction

memory

Instruction

Register #

Registers

Register #

ALU

Address

Data

memory

Register #

Data

•

Dois tipos de unidades funcionais:

– Elementos que processam valores de dados (log. combinacional)

– Elementos que armazenam estado (log. Sequencial - memória)

24

Simplificação da Implementação

• Unidades funcionais básicas usadas na construção da CPU

Instruction

address

PC

Instruction

Add Sum

MemWrite

Instruction

memory

Address

a. Instruction memory

b. Program counter

c. Adder

Write

data

5

Register

numbers

5

5

Data

3

Read

register 1

Read

register 2

Registers

Write

register

Write

data

ALU control

Read

data 1

Read

data

Data

memory

Sign

extend

32

MemRead

a. Data memory unit

Data

16

b. Sign-extension unit

Zero

ALU ALU

result

Read

data 2

RegWrite

a. Registers

b. ALU

25

Fluxo no caminho de dados

•

Multiplexadores para selecionar as vias (entradas e saídas)

PCSrc

M

u

x

Add

Add ALU

result

4

Shift

left 2

Registers

PC

Read

address

Instruction

Instruction

memory

Read

register 1

Read

Read

data 1

register 2

Write

register

Write

data

RegWrite

16

ALUSrc

Read

data 2

Sign

extend

M

u

x

3

ALU operation

Zero

ALU ALU

result

MemWrite

MemtoReg

Address

Read

data

Data

memory

Write

data

M

u

x

32

MemRead

26

Controle

•

Seleção de operações a serem realizadas (ALU, read/write, etc.)

•

Controle do fluxo de dados (entradas dos multiplexadores)

•

Informações codificadas com os 32 bits da instrução

•

Exemplo:

add $8, $17, $18

•

000000

10001

10010

01000

op

rs

rt

rd

00000 100000

shamt

funct

Operação da ULA é baseada no tipo de instrução (campo op) e no

código da função (campo funct)

27

Controle – Execução de Instrução na ULA

• O que a ULA deveria fazer com a instrução abaixo?

lw $1, 100($2)

•

35

2

1

op

rs

rt

16 bit offset

Controle de entrada da ULA (define a operação aritmética)

000

010

111

•

100

AND

001

add

110

set-on-less-than

OR

subtract

Outros bits: tipo de instrução:

00:lw, sw

01:beq

11:aritmética

28

Solução para HW de Controle da ULA

0

M

u

x

Add

Add

4

Instruction [31– 26]

Control

Instruction [25– 21]

PC

Read

address

Instruction

memory

Instruction [15– 11]

1

Shift

left 2

RegDst

Branch

MemRead

MemtoReg

ALUOp

MemWrite

ALUSrc

RegWrite

Read

register 1

Instruction [20– 16]

Instruction

[31– 0]

ALU

result

0

M

u

x

1

Read

data 1

Read

register 2

Registers Read

Write

data 2

register

0

M

u

x

1

Write

data

Zero

ALU ALU

result

Address

Write

data

Instruction [15– 0]

16

Sign

extend

Read

data

Data

memory

1

M

u

x

0

32

ALU

control

Instruction [5– 0]

Memto- Reg Mem Mem

Instruction RegDst ALUSrc

Reg

Write Read Write Branch ALUOp1 ALUp0

R-format

1

0

0

1

0

0

0

1

0

lw

0

1

1

1

1

0

0

0

0

sw

X

1

X

0

0

1

0

0

0

X

0

X

0

0

0

1

0

1

beq

29

0

M

u

x

Add ALU

result

Add

4

Instruction [31– 26]

Read

address

Instruction

memory

Read

register 1

Instruction [20– 16]

Instruction

[31– 0]

Instruction [15– 11]

Shift

left 2

RegDst

Branch

MemRead

MemtoReg

Control ALUOp

MemWrite

ALUSrc

RegWrite

Instruction [25– 21]

PC

1

0

M

u

x

1

Read

data 1

Read

register 2

Registers Read

Write

data 2

register

0

M

u

x

1

Write

data

Zero

ALU ALU

result

Address

Write

data

Instruction [15– 0]

16

Sign

extend

Read

data

Data

memory

1

M

u

x

0

32

ALU

control

Instruction [5– 0]

30

GOTO...

•

Material Prof. José Luís Güntzel (UFSC) disponível em:

http://www.inf.ufsc.br/~guntzel/ine641400/ine641400.html

•

Parte 1: MIPS monociclo: instruções a serem implementadas, regime

de clock, construção do bloco operativo:

http://www.inf.ufsc.br/~guntzel/ine641400/AOC2_aula2.pdf

•

Parte 2: MIPS monociclo: controle da ULA, execução das instruções,

bloco de controle principal, desempenho de máquinas monociclo:

http://www.inf.ufsc.br/~guntzel/ine641400/AOC2_aula3.pdf

31