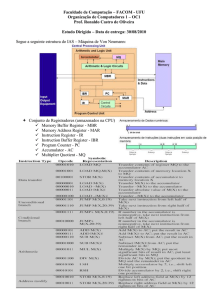

Desenho do Processador

Luı́s Nogueira

[email protected]

Departamento Engenharia Informática

Instituto Superior de Engenharia do Porto

Desenho do processador – p. 1

Introdução

• Definindo o seguinte subconjunto da ISA MIPS

◦ Aritméticas e lógicas: add, sub, and, or, slt

◦ Acesso à memória: lw, sw

◦ Salto condicional e incondicional: beq, bne, j

• Desenhar um processador

◦ Que componentes precisamos?

◦ Como ligamos os componentes?

◦ Como controlamos o fluxo de execução?

• Análise

◦ ISA influencia a implementação

◦ Estratégias seguidas influenciam ciclo de relógio

Desenho do processador – p. 2

Componentes necessários

• Memória de instruções - contém programa a executar

• PC - endereço da próxima instrução

• Incrementador - avançar PC para próxima instrução

Instruction

address

Instruction

PC

Add Sum

Instruction

memory

a. Instruction memory

b. Program counter

c. Adder

Desenho do processador – p. 3

Componentes necessários

• Registos - armazenar operandos e resultados

• ALU - cálculo aritmético e lógico

5

Register

numbers

5

5

Data

Read

register 1

4

Read

data 1

Read

register 2

Write

register

ALU operation

Zero

Data

Registers

ALU ALU

result

Read

data 2

Write

Data

RegWrite

a. Registers

b. ALU

Desenho do processador – p. 4

Componentes necessários

• Memória de dados - armazenar valores

• Conversor 16/32 bits - manipulação de endereços

MemWrite

Address

Read

data

16

Write

data

Data

memory

Sign

extend

32

MemRead

a. Data memory unit

b. Sign-extension unit

Desenho do processador – p. 5

Classificação dos componentes

• Elementos funcionais (lógica combinacional)

◦ Dado o mesmo input produzem sempre o mesmo output

◦ Não guardam informação internamente

◦ ALU, incrementador, conversor

• Elementos com estado

◦ Armazenam dados, instruções e resultados temporários

◦ Contêm informação necessária à re-inicialização

◦ Registos, memórias, PC

Desenho do processador – p. 6

Sinal de relógio

• Sinal eléctrico com uma dada frequência (MHz)

• Decide momento de actualização dos elementos com

estado

• Dois estados: (1) sinal activo, (0) sinal inactivo

• Sinal rectangular: mudança de estado nos lados verticais

State

element

1

Combinational logic

State

element

2

Clock cycle

Desenho do processador – p. 7

Ciclo de execução de uma instrução

1. Obter instrução da memória apontada por PC

2. Obter os operandos (endereço ou registos)

3. ALU executa operação ou calcula endereço

4. Instruções lw/sw acedem à memória

5. Resultado é armazenado

(a) Dados da memória são escritos em registos

(b) Resultado da ALU escrito em registo

(c) Novo endereço escrito no PC

• Como interligar os componentes?

Desenho do processador – p. 8

Obter instrução apontada por PC

• Aceder à memória de instruções

• Preparar a execução da instrução seguinte

◦ Incrementar PC

Add

4

PC

Read

address

Instruction

Instruction

memory

Desenho do processador – p. 9

Instruções formato R e lw/sw

• Instruções aritméticas e de acesso à memória são similares

◦ ALU calcula operação sobre registos ou endereços

◦ Resultado armazenado em registo ou memória

Read

register 1

Instruction

4

Read

data 1

Read

register 2

Registers Read

Write

data 2

register

MemWrite

ALUSrc

0

M

u

x

1

Write

data

MemtoReg

Zero

ALU ALU

result

Address

Write

data

RegWrite

16

ALU operation

Sign

extend

32

Read

data

1

M

u

x

0

Data

memory

MemRead

Desenho do processador – p. 10

Instruções de salto condicional

• Comparar valor dos registos

• Calcular endereço destino

PC+4 from instruction datapath

Add Sum

Branch

target

Shift

left 2

Instruction

Read

register 1

Read

data 1

Read

register 2

Write

register

4

ALU operation

ALU Zero

Registers

To branch

control logic

Read

data 2

Write

data

RegWrite

16

Sign

extend

32

Desenho do processador – p. 11

Arquitectura do processador

PCSrc

M

u

x

Add

Add

4

ALU

result

Shift

left 2

PC

Read

address

Instruction

Instruction

memory

Read

register 1

ALUSrc

Read

data 1

ALU operation

MemWrite

Read

register 2

Registers Read

Write

data 2

register

MemtoReg

Zero

M

u

x

Write

data

ALU ALU

result

Address

Write

data

RegWrite

16

4

Sign

extend

32

Read

data

M

u

x

Data

memory

MemRead

Desenho do processador – p. 12

Controlo do fluxo de informação

• Necessário garantir que. . .

◦ próxima instrução só começa quando actual termina

◦ ALU executa operação correcta

◦ durante escrita de registos não há leituras de registo

◦ durante escrita na memória não há leituras da memória

◦ PC avança para próxima instrução ou “salta”

◦ numa instrução lw/sw ALU gera endereço de memória

◦ após instrução aritmética o resultado é escrito num

registo

Desenho do processador – p. 13

Controlo do fluxo de informação

• Relógio

◦ Sinal de controlo global que afecta todos os

componentes

◦ Determina ritmo a que a informação circula

◦ Exemplo: 1 GHz equivale a um ciclo de 1 nano-segundo

• Sinais de controlo

◦ Activam apenas uma parte do circuito

◦ Dependem do tipo de instrução e da fase em que a

instrução se encontra

◦ São despoletados pelo opcode da instrução

Desenho do processador – p. 14

Sinais de controlo

Formato R

Formato I

opcode

rs

rt

rd

shamt

funct

31:26

25:21

20:16

15:11

10:6

5:0

opcode

rs

rt

addr

31:26

25:21

20:16

15:0

• Registo destino

◦ rt em lw nos bits 20:16

◦ rd em instruções formato R nos bits 15:11

• Adicionar multiplexador para seleccionar campo da

instrução

Desenho do processador – p. 15

Sinais de controlo

• ALUOp tipo de operação na ALU

• RegDest registo de destino

• ALUSrc distingue instruções formato R e I

• PCSrc/Branch determina se PC avança 4 bytes ou “salta”

• MemRead controla leitura da memória

• MemWrite controla escrita na memória

• MemtoReg selecciona resultado da ALU ou da memória

• RegWrite controla escrita nos registos

Desenho do processador – p. 16

Sinais de controlo

Instrução

Formato R

lw

sw

beq/bne

RegDest

1

0

X

X

ALUSrc

0

1

1

0

Instrução

Formato R

lw

sw

beq/bne

MemRead

0

1

0

0

MemWrite

0

0

1

0

MemtoReg

0

1

X

X

Branch

0

0

0

1

RegWrite

1

1

0

0

ALUOp

10

00

00

01

Desenho do processador – p. 17

Sinais de controlo

0

M

u

x

Add

Add

4

Control

Instruction [25–21]

PC

Read

address

Instruction [20–16]

Instruction

[31–0]

Instruction

memory

0

M

u

Instruction [15–11] x

1

Read

register 1

Read

register 2

Write

register

Write

data

Instruction [15–0]

16

1

Shift

left 2

RegDst

Branch

MemRead

MemtoReg

ALUOp

MemWrite

ALUSrc

RegWrite

Instruction [31–26]

ALU

result

Read

data 1

Zero

Read

data 2

Registers

Sign

extend

0

M

u

x

1

ALU ALU

result

Address

Read

data

1

M

u

x

0

Data

Write memory

data

32

ALU

control

Instruction [5–0]

Desenho do processador – p. 18

Controlo de fluxo lw $1,offset($2)

1. Instrução é obtida da memória de instruções e PC é

incrementado

2. Instrução descodificada. Valor do registo $2 é lido dos

registos

• Branch=0

3. ALU calcula soma do valor do registo e deslocamento

convertido

• ALUSrc=1, ALUop=00

4. Resultado da ALU usado como endereço na memória de

dados

• MemRead=1, MemWrite=0

5. Valor em endereço escrito no registo destino

• RegDest=0, RegWrite=1, MemtoReg=1

Desenho do processador – p. 19

Saltos absolutos

Formato J

opcode

addr

31:26

25:0

• Endereço final

◦ Conversor 26 para 28 bits

◦ Últimos 4 bits são dependentes do PC

• Acrescentar ao processador

◦ Sinal de controlo Jump

◦ Multiplexador (salto condicional ou absoluto)

Desenho do processador – p. 20

Saltos absolutos

Instruction [25–0]

26

Shift

left 2

Jump address [31–0]

28

PC + 4 [31–28]

Add

Add

4

Control

Instruction [25–21]

PC

Read

address

Instruction [20–16]

Instruction

[31–0]

Instruction

memory

0

M

u

Instruction [15–11] x

1

Read

register 1

Read

register 2

Write

register

Write

data

Instruction [15–0]

16

1

M

u

x

M

u

x

1

0

Shift

left 2

RegDst

Jump

Branch

MemRead

MemtoReg

ALUOp

MemWrite

ALUSrc

RegWrite

Instruction [31–26]

ALU

result

0

Read

data 1

Zero

Read

data 2

Registers

Sign

extend

0

M

u

x

1

ALU ALU

result

Address

Read

data

1

M

u

x

0

Data

Write memory

data

32

ALU

control

Instruction [5–0]

Desenho do processador – p. 21

Implementação do controlo

• Hardwired

◦ Directamente nos circuitos

◦ Possível se ISA tem poucas e simples instruções

◦ Mais rápido

• Microcódigo

◦ Em ROMs/PLAs com pequenos programas

◦ Programas activam sinais de controlo em função do

opcode

◦ Exemplo: Intel IA-32

Desenho do processador – p. 22

Controlador de microcódigo

Microcode

storage

Datapath

control

outputs

Outputs

Input

1

Microprogram counter

Sequencing

control

Adder

Address select logic

Inputs from instruction

register opcode field

Desenho do processador – p. 23

Intel IA-32

• Instruções complexas que demoram vários ciclos de relógio

• Maior no e complexidade de modos de endereçamento

• Adaptar fluxo de dados

◦ Instruções variam no no de ciclos de relógio

◦ Reutilização de componentes numa instrução

• A partir do 80486 combinação de controlo hardwired e

microcódigo

◦ Hardwired para instruções simples

◦ Microcódigo para instruções complexas

Desenho do processador – p. 24

Intel IA-32

• Tradução de instruções complexas em micro-instruções

◦ Semelhantes a instruções MIPS

• Controlo hardwired das micro-instruções

• Pentium II, Pentium III e Pentium Pro

◦ Lê 3 instruções IA-32 simultaneamente

◦ Usa PLAs para gerar até 6 micro-instruções

• Menor ciclo de relógio do Pentium 4 exigiu alterações

◦ Se tradução origina até 3 micro-instruções→trace cache

◦ Maior no de micro-instruções→ ROM de

micro-instruções (8000 instruções)

Desenho do processador – p. 25