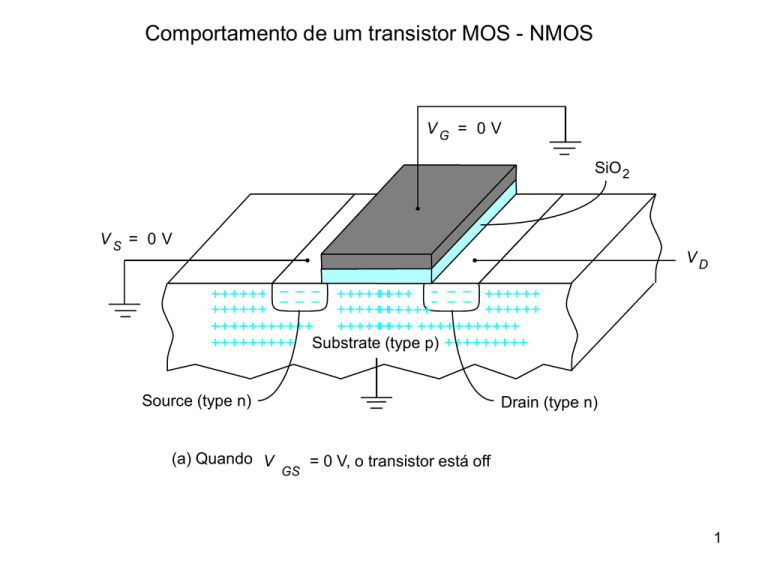

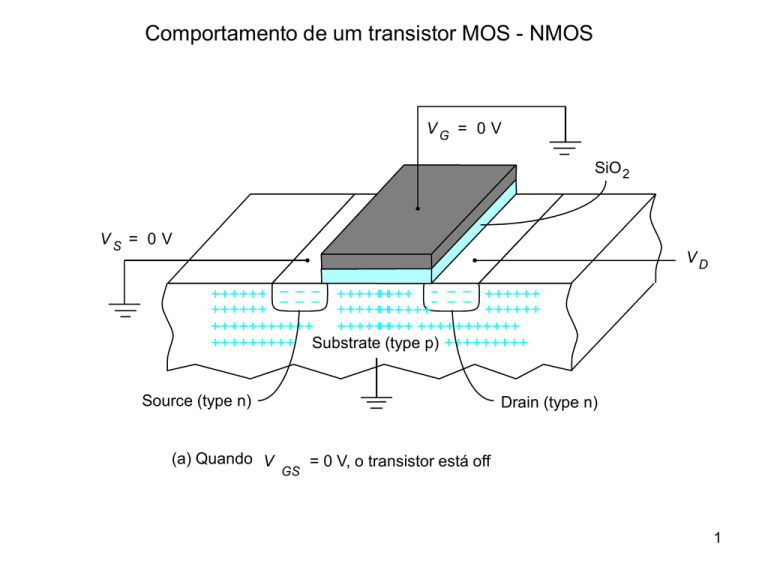

Comportamento de um transistor MOS - NMOS

VG = 0 V

SiO 2

VS = 0 V

VD

++++++ ++++ ++++++

++++++

++++ +++

++++++

++++++

++++++

++++++

++++ +++++++++++

+++++++++++ ++++++

+++++++++ Substrate (type p) +++++++++

Source (type n)

(a) Quando V

Drain (type n)

GS

= 0 V, o transistor está off

1

Comportamento de um transistor MOS - NMOS

VDD

VG = 5 V

SiO2

VS = 0 V

VD = 0 V

++++++ ++++

+++ ++++++

++++++

++++++

+++++++++++ +++++++++++++++++

+++++++++ ++ +++++++ ++++++++++

Channel (type n)

(b) Quando V = 5 V, o transistor está on

V

GS

GS

> V T há a formação do canal

2

Comportamento de um transistor MOS – NMOS

Comprimento e Largura de Canal

ID = k’nW / L [ ( VGS – VT ) VDS – ½ V2DS ]; (gráfico no próximo slide)

onde k’n é a transcondutância (parâmetro de processo – unidade A / V2

quando VDS = VGS – VT , a corrente atinge a máximo (saturação) e

ID = k’nW / L [ ( VGS – VT )2] independe de VDS

OBS – A análise para o PMOS é semelhante, só que teremos VS com a

maior tensão e VT negativo e K’p ~ 0,4 K’n

Exercício: Assumir k’n = 60 u A/V2, W/L = 2,0 mm / 0,5 mm, VS = 0. Se VD = 2,5,

qual a corrente ID na região de triodo e na região de saturação.

ON – Resistence em um MOSFET

RDS = VDS / ID RDS = 1/[k’n W/L (VGS – VT)]

Exercício: Assumir k’n = 60 u A/V2, W/L = 2,0 mm / 0,5 mm, VGS = 5V.

Calcular RDS.

3

Relação tensão-corrente em um transistor NMOS

I

ID

Triode

0

Saturação

VGS – VT

VDS

+

W1

+

W2

L

L

(a) Small transistor

(b) Larger transistor

4

Níveis de tensão em um inversor NMOS inverter

DD

DD

V

V

R

Vf

I stat

Vx

(a) NMOS NOT gate

V f = VOL

RDS

(b) V x = 5 V

OBS: Nos inversores

NMOS, geralmente o

resistor é um transistor

PMOS pseudo

PMOS compatível

com CMOS

VX = 0 NMOS aberto, sem fluxo de corrente Vf = 5V

VX = VDD Vf = VDD (RDS /(RDS + R))

Exercício: R = 25 KW e RDS -= 1KW. Calcular Isat e Vf

5

Curva de transferência de um inversor CMOS

VX = 0 NMOS off

Vf

Sem

fluxo de

VOH= VDD

VX = VDD PMOS off

Slope = -1

corrente

Na realidade existe uma pequena

corrente leakage current VOL =

0,1 mV

VOL, VIL, VOH e VIH quantifica a

robustez de uma família lógica

VOL = 0V

VT

VIH (V – V )VDD

VIL

VDD

DD

T

Vx

—

2

6

Margem de Ruído

N1

x

A

N2

f

Dois inversores em cascata

Ruído perturbações randômicas que podem alterar um sinal.

Por exemplo, a saída de N1 pode ser alterada por uma perturbação externa (ruído).

Se este ruído alterar VIL de N1, este nível deve se manter abaixo de VIL, para ser

interpretado corretamente por N2.

A capacidade para tolerar ruídos sem afetar a operação correta margem de ruído

NML = VIL – VOL

NMH = VOH – VIH

Exercício – Dada na figura do slide 6, temos que VOH = VDD e VOL = 0 V. Nos pontos

onde a inclinação da curva = -1, podemos tirar:

VIL =~ 1/8 (3VDD + 2VT) e VIH =~1/8 (5VDD - 2VT)

Para o valor típico de VT = 0,2VDD, temos NML = NMH = 0,425 x VDD

Calcule a margem de ruído para VDD = 5 V e VDD = 3.3 V.

7

Operações Dinâmicas de Portas Lógicas

VDD

VDD

N1

Vx

N2

VA

Vf

C - capacitor

parasita

Carga capacitiva no ponto A

Por causa da construção dos transistores, o inversor N2 recebe o efeito da

capacitância de carga (capacitância parasita) do ponto VA. A capacitância

parasita no ponto VA é devido ao Inversor N1 e ao inversor N2, mas o que

mais contribui é a capacitância que existe na entrada de N2 e o terra. O

valor do desta capacitância depende do tamanho do transistor. Cada

transistor contribui com a capacitância de porta Cg = W x L x Cox. O

parâmetro Cox(capacitância do óxido), é uma constante e depende da

tecnologia unidade fF/mm2.

8

Efeito da capacitância parasita na velocidade de um circuito lógico

A capacitância tem um efeito negativo na velocidade de um circuito lógico.

tr rise time (10% a 90% de VDD)

tf fall time (90% a 10% de VDD)

tp propagation time (medido a 50% de VDD, entre entrada e saída)

tp = C DV/ID = C(VDD/2) / ID 1,7 C / K’n (W/L) VDD

V DD

Vx

50%

50%

Gnd

Propagation delay

Propagation delay

V DD

90%

VA

90%

50%

Gnd

50%

10%

tr

10%

tf

Exercício – Para C = 70 fF, K’n = 60mA/V2, W/L = 2,0/0,5 e VDD = 5V.

Calcular tp.

9

Dissipação de Potência – tecnologia MOS

Quando um transistor está em saturação PS = Isat x VDD (inversor NMOS). Se Isat = 0,2

mA e VDD = 5 V , PS = 1,0 mW. Para um circuito com 10.000 inversores P = 10 W

crítico para circuitos alimentados por bateria.

Potência Estática x Potência Dinâmica NMOS dissipa ambas, CMOS apenas a

dinâmica

Inversor CMOS

Vx baixo NMOS off não existe corrente

Vx alto PMOS off não existe corrente

Quando há a transição, existe fluxo de corrente dissipação de potência.

Potência dissipada em um inversor CMOS PD = f x C x VDD2

Exercício – Se C = 70 fF, VDD = 5 V e f = 100 MHz, calcule PD de um inversor MOS. E para

10.000 inversores, supondo 20% chaveando ?

VDD

Fluxo de corrente na

mudança de 0 V

para 5 V

ID

Vf

Vx

Vx

Fluxo de corrente na mudança

de 0 V para 5 V

ID

Vf

10

V DD

Fan-in de uma porta NOR e uma porta NAND

NMOS

Vf

tp = (1,7 C / (K’n (W/L) VDD ) x n. de entradas

Vx

1

Vx

2

Vx

3

Vx

k

VDD

Vf

Vx1

Vx2

Vxk

11

Efeito do fan-out no atraso do tempo de propagação

N1

x

Vf

To inputs of

x

n other inverters

f

To inputs of

n other inverters

Cn

Circuito equivalente

Inversor que alimenta (drive) n inversores

V f for n =1

VDD

V f for n = 4

Gnd

0

Time

(c) Tempo de propagação para diferentes valores de n

12

Buffer não-inversor

V DD

Vx

Vf

(a) Implementation of a buffer

x

f

(b) Graphical symbol

13

Buffer Tri-state

e= 0

x

e

x

f

f

e= 1

x

(a) Buffer tri-state

(b) Circuito Equivalente

e x

f

e

0

0

1

1

Z

Z

0

1

x

0

1

0

1

(c) Tabela Verdade

f

f

(d) Implementação

14

Quatro tipo de buffers tri-state

e

e

f

x

f

x

(a)

(b)

e

e

f

x

(c)

f

x

(d)

15

Uma aplicaçao de buffers tri-state

x1

f

s

x2

Que circuito é este ??????????

16

Transmission gate

s

x

f

s

s

f

0

1

Z

x

(b) Tabela Verdade

(a) Circuito

s= 0

x

x

s= 1

x

s

f=Z

f=x

(c) Circuito equivalente

f

s

(d) Símbolo gráfico

17

Porta Exclusive-OR

x1 x2

0

0

1

1

0

1

0

1

f = x 1 x2

0

1

1

0

Tabela Verdade

x1

f = x1 x 2

x2

Símbolo Gráfico

x1

x2

f = x1 x2

Implementação em soma-de -produtos

18

CMOS Exclusive-OR gate

x1

x2

f = x1 x2

implementação CMOS

19

Um multiplexador 2-to-1 usando transmission gates

x

1

s

x

2

f

20

Um exemplo de um NOR-NOR PLA

x1 x2

x3

NOR plane

VDD

VDD

VDD

f1

f2

S1

VDD

S2

VDD

S3

NOR plane

21

Um Plano NOR Programável

x1

x2

xn

VDD

S1

VDD

S2

VDD

Sk

(a) Plano NOR Programável

Ve

=

Ve

(b) Uma chave programável

++++

+++++

++++++++++++++++

(c) transistor EEPROM

22

x1

x2

x3

x4

NOR plane

V DD

V DD

S1

S2

S3

S4

S5

S6

NOR plane

PLA Programável NOR-NOR

f1

f2

23

x1

x2

x3

x4

NOR plane

V DD

VDD

P1

P2

P3

P4

P5

P6

NOR plane

Uma PLA NOR-NOR PLA usada como SOP

f1

f2

24

x1

x2

x3

x4

VDD

P1

P2

f1

P3

P4

P5

f2

P6

NOR plane

PAL programada para implementar duas funções

25

Transistor de passagem em FPGAs

x1

x2

0

0

0

1

Vf

f1

1

VA

1

0

0

SRAM

SRAM

SRAM

(to other wires)

26