Circuitos Lógicos e Organização

de Computadores

Capítulo 3 – Tecnologia de Implementação

Ricardo Pannain

[email protected]

http://docentes.puc-campinas.edu.br/ceatec/pannain/

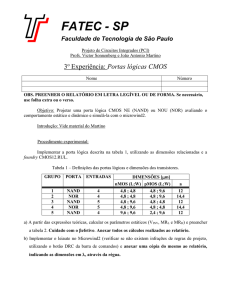

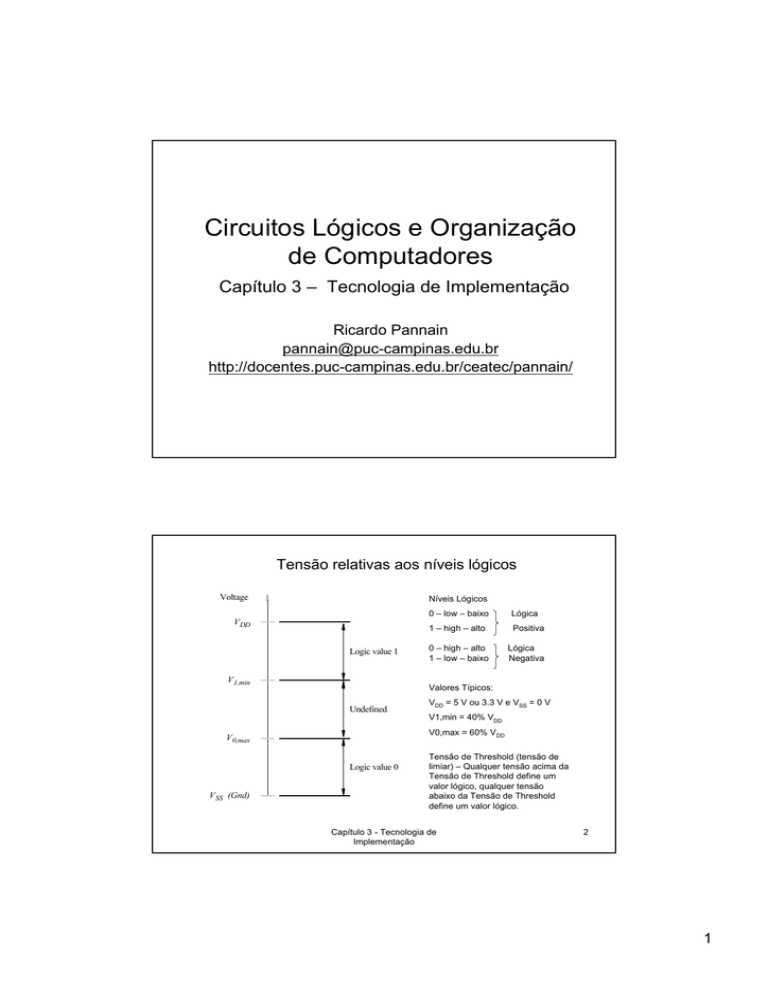

Tensão relativas aos níveis lógicos

Voltage

Níveis Lógicos

V DD

Logic value 1

V 1,min

0 – low – baixo

Lógica

1 – high – alto

Positiva

0 – high – alto

1 – low – baixo

Lógica

Negativa

Valores Típicos:

Undefined

VDD = 5 V ou 3.3 V e VSS = 0 V

V1,min = 40% VDD

V0,max = 60% VDD

V 0,max

Logic value 0

V SS (Gnd)

Tensão de Threshold (tensão de

limiar) – Qualquer tensão acima da

Tensão de Threshold define um

valor lógico, qualquer tensão

abaixo da Tensão de Threshold

define um valor lógico.

Capítulo 3 - Tecnologia de

Implementação

2

1

Transistor NMOS como uma chave

x = "low"

x = "high"

MOS – Metal Oxide Silicon

NMOS – MOS tipo N (canal

N – Substrato P)

(a) Uma chave controlada por uma entrada x

Gate - Porta

Gate

Source – Fonte

Drain - Dreno

Source

Drain

Substrate (Body)

Se VG é baixo, não há

formação de canal entre

fonte e dreno ? transistor

não conduz ? transistor

aberto (turned off)

(b) Transistor NMOS

VG

VS

Susbstrate (body) –

substrato

VD

(c) Símbolo simplificado de um transistor NMOS

Se VG é alto, há formação

de canal entre fonte e

dreno ? transistor conduz

? transistor fechado

(turned on)

Capítulo 3 - Tecnologia de

Implementação

3

Transistor PMOS como uma chave

x = "high"

(a)

x = "low"

PMOS – MOS tipo P (canal

P – Substrato N)

Uma chave com comportamento oposto ao do slide anterior

Gate

Gate - Porta

Source – Fonte

Drain - Dreno

Drain

Source

VDD

Substrate (Body)

(b) Transistor PMOS

Se VG é baixo, há formação

de canal entre fonte e

dreno ? transistor não

conduz ? transistor

fechado (turned on)

VG

VS

Susbstrate (body) –

substrato

VD

(c) Símbolo simplificado de um transistor PMOS

Capítulo 3 - Tecnologia de

Implementação

Se VG é alto, não há

formação de canal entre

fonte e dreno ? transistor

não conduz ? transistor

aberto (turned off)

4

2

Transistores NMOS e PMOS em circuitos lógicos

VD

VD = 0 V

VD

VG

VS = 0 V

Chave fechada

quando VG = V DD

Chave aberta

quando VG = 0 V

(a) Transistor NMOS

VS= VDD

VDD

VDD

VG

VD

VD

VD = VDD

Chave Aberta

quando VG = VDD

Chave fechada

quando VG = 0 V

(b) Transistor PMOS

Capítulo 3 - Tecnologia de

Implementação

5

Uma Porta Inversora – NOT - construída com tecnologia

NMOS

VDD

Vf = 0,2 V quando Vx = 5 V

R

5V

O resistor é um limitador de

corrente (na prática, outro

transistor)

R

+

Vf

-

Vf

Vx

Vx

(a) Diagrama do Circuito

x

f

(b) Diagrama simplificado

x

f

(c) Símbolos Gráficos

Capítulo 3 - Tecnologia de

Implementação

6

3

Porta NAND com tecnologia NMOS

VDD

x1 x2

f

0

1

0

1

1

1

1

0

Vf

0

0

1

1

Vx1

Vx2

(b) Tabela Verdade

(a) Circuito

x1

f

x2

x1

f

x2

(c) Símbolo Gráfico

Capítulo 3 - Tecnologia de

Implementação

7

Porta NOR com tecnologia NMOS

V DD

Vf

Vx

Vx

1

x2

f

0

0

1

1

1

0

0

0

2

0

1

0

1

(b) Truth table

(a) Circuit

x1

x1 x2

f

x1

x2

f

(c) Graphical symbols

Capítulo 3 - Tecnologia de

Implementação

8

4

Porta AND

com tecnologia

NMOS

V

V

DD

DD

Vf

x1 x2

0

1

0

1

0

0

1

1

A

Vx1

Vx2

f

0

0

0

1

(b) Tabela Verdade

(a) Circuito

x1

f

x2

x1

f

x2

(c) Símbolos Gráficos

Capítulo 3 - Tecnologia de

Implementação

9

Porta OR com tecnologia NMOS

VDD

VDD

Vf

Vx

Vx

1

2

(a) Circuit

x1

x2

f

x1 x 2

f

0

0

1

1

0

1

1

1

0

1

0

1

(b) Truth table

x1

x2

f

(c) Graphical symbols

Capítulo 3 - Tecnologia de

Implementação

10

5

Estrutura de uma Porta NMOS

VDD

Vf

Vx

Vx

1

Pull-down network

(PDN)

n

Capítulo 3 - Tecnologia de

Implementação

11

Estrutura de uma Porta CMOS

V DD

CMOS – Complementary MOS –

resistor referente à porta NOMS é

substituído por uma rede Pull-up

(PUN)

Pull-up network

(PUN)

PDN e PUN são duais, se o PDN

tiver transistores NMOS em série,

PUN terá transistores PMOS em

paralelo, e vice-versa.

Vf

Vx

Vx

1

Pull-down network

(PDN)

n

Capítulo 3 - Tecnologia de

Implementação

12

6

Estrutura de uma Porta NOT CMOS

VDD

T1

Vx

Vf

T2

(a) Circuito

x

T1 T2

f

0

1

on off

off on

1

0

(b) Tabela verdade e estados dos transistores

Capítulo 3 - Tecnologia de

Implementação

13

Estrutura de uma Porta NAND CMOS

V DD

T1

T2

Vf

Vx

Vx

T3

1

T4

2

(a) Circuit

x1 x2

T1 T2 T3 T4

f

0

1

0

1

on on off off

on off off on

off on on off

1

1

1

0

0

0

1

1

off off on on

(b) Truth table and transistor states

Para f = 1 ? f = x1x2 = x1 + x2 ? PUN = 2 transistores PMOS em paralelo

Para f = 0 ? f = x1x2 ? PDN = 2 transistores NMOS em paralelo

Capítulo 3 - Tecnologia de

Implementação

14

7

Estrutura de uma Porta NOR

V DD CMOS

Vx

1

T1

Vx

2

T2

Vf

T1 T2 T3 T4

f

0

1

0

1

on on off off

on off off on

off on on off

1

0

0

0

0

0

1

1

T4

T3

x1 x2

(a) Circuit

off off on on

(b) Truth table and transistor states

Para f = 1 ? f = x1 + x2 = x1 . x2 ? PUN = 2 transistores PMOS em série

Para f = 0 ? f = x1 + x2 ? PDN = 2 transistores NMOS em paralelo

Capítulo 3 - Tecnologia de

Implementação

15

Estrutura de uma Porta AND

CMOS

VDD

VDD

Vf

Vx

1

Vx

2

NAND

+

NOT

Capítulo 3 - Tecnologia de

Implementação

16

8

Estrutura de uma Porta CMOS

Exercício 1

Considere a função: f = x1 + x2 x3

Ache o circuito CMOS equivalente

Exercício 2

Considere a função: f = x1 + (x2 + x3) x4

Ache o circuito CMOS equivalente

Capítulo 3 - Tecnologia de

Implementação

17

Estrutura de uma Porta CMOS – Exercício 1

VDD

f = x1 + x2 x3 = x1 (x2 + x3)

Vf

Vx

1

Vx

2

Vx

3

Capítulo 3 - Tecnologia de

Implementação

18

9

Estrutura de uma Porta CMOS – Exercício 2

V DD

f = x1 ( x2 x3 + x4)

Vf

Vx

1

Vx

2

Vx

3

Vx

4

Capítulo 3 - Tecnologia de

Implementação

19

Níveis de Tensão em uma Porta Lógica

V DD

Vf

Vx

1

Vx

2

Vx Vx

1

L L

L H

H L

H H

(a) Circuit

2

Vf

H

H

H

L

(b) Voltage levels

Capítulo 3 - Tecnologia de

Implementação

20

10

Interpretação dos Níveis de Tensão – Lógica Positiva e Negativa

Vx Vx

1

2

Vf

L

H

L

H

L

L

H

H

H

H

H

L

(a) Níveis de Tensão

x1 x2

f

0

0

1

1

1

1

1

0

0

1

0

1

x1

f

x2

(b) Tabela Verdade – Lógica Positiva e Símbolo

x1 x2

f

1

1

0

0

0

0

0

1

1

0

1

0

x1

f

x2

(c) Tabela Verdade – Lógica Negativa e Símbolo

Capítulo 3 - Tecnologia de

Implementação

21

Interpretação dos Níveis de Tensão – Lógica Positiva e Negativa

Vx Vx

Vf

L

H

L

H

L

L

L

H

1

L

L

H

H

2

(a) Níveis de Tensão

x1 x2

f

0

0

1

1

0

0

0

1

0

1

0

1

x1

x2

f

(b) Lógica Positiva

x1 x2

f

1

1

0

0

1

1

1

0

1

0

1

0

x1

x2

f

(c) Lógica Negativa

Capítulo 3 - Tecnologia de

Implementação

22

11

Circuito Integrado Padrão – Série

7400

(a) Encapsulamento Dual-Line – DIP (Dual-Line Package)

VDD

Gnd

(b) Estrutura de um Circuito Integrado 7404

Capítulo 3 - Tecnologia de

Implementação

23

Implementação de f = x1x2 + x2x3

VDD

7404

7408

x1

x2

x3

7432

f

Capítulo 3 - Tecnologia de

Implementação

24

12

Pin 11

Pin 13

Pin 15

Pin 17

Pin 5

Pin 7

Pin 9

Pin 19

Pin 18

Pin 8

Pin 3

Pin 16

Pin 14

Pin 4

Pin 6

Pin 12

Pin 2

Pin 1

Circuito Integrado 74244 - 8 Buffers tri-states

Capítulo 3 - Tecnologia de

Implementação

25

Dispositivos Lógicos Programáveis como uma

Caixa Preta

Porta Lógicas

Entradas

(variáveis lógicas)

e

chaves

Saídas

(funções lógicas)

programáveis

Capítulo 3 - Tecnologia de

Implementação

26

13

Estrutura geral de uma PLA – Programmable Logic Array

x1 x2

xn

Baseado na idéia que as funções lógicas

podem ser representadas como uma

soma de produtos ? plano de ANDs e

plano de ORs

Input buffers

and

inverters

x1 x1

xn xn

P1

OR plane

AND plane

Pk

f1

fm

Capítulo 3 - Tecnologia de

Implementação

27

Diagrama, em nível de portas lógicas, de uma PLA

x1

x2

x3

Conexões

programáveis

P1

Plano OR

P2

P3

P4

Plano AND

f1

f2

Exercício – Dizer quais são as respectivas funções f1 e f2.

Capítulo 3 - Tecnologia de

Implementação

28

14

Desenho esquemático de uma PLA

x1

x2

x3

Plano OR

P1

P2

P3

P4

Plano AND

f1

f2

Capítulo 3 - Tecnologia de

Implementação

29

Exemplo de uma PAL – Programmable Array Logic

x1

x2

x3

PAL – O plano AND é

programável e o Plano OR é fixo

P1

P2

f1

P3

P4

f2

Plano AND

Capítulo 3 - Tecnologia de

Implementação

30

15

Circuito extra de saída de uma PAL

Select

Enable

f1

Flip-flop

D

Q

Clock

Para o plano AND

Capítulo 3 - Tecnologia de

Implementação

31

Unidade de Programação de um PLD

Capítulo 3 - Tecnologia de

Implementação

32

16

UM PLCC – Plastic-Leaded Chip Carrier com soquete

rd

boa

uit

c

r

i

dc

nte

Pri

Capítulo 3 - Tecnologia de

Implementação

33

PAL-like

block

PAL-like

block

I/O block

I/O block

Estrutura de CPLD – Complex Programmable Logic Device

PAL-like

block

PAL-like

block

Capítulo 3 - Tecnologia de

Implementação

I/O block

I/O block

Interconnection wires

34

17

Detalhe de um CPLD

PAL-like block (details not shown)

PAL-like block

D Q

D Q

D Q

Capítulo 3 - Tecnologia de

Implementação

35

Encapsulamento de um CPLD e sua programação

(a) CPLD in a Quad Flat Pack (QFP) package

To computer

Printed

circuit board

(b) JTAG programming

Capítulo 3 - Tecnologia de

Implementação

36

18

Estrutura de uma FPGA – Field Programmable Gate Array

Logic block

Interconnection switches

I/O block

I/O block

I/O block

I/O block

Capítulo 3 - Tecnologia de

Implementação

FPGA -

37

lookup table (LUT) de duas entradas

x1

0/1

0/1

f

0/1

0/1

x2

(a) Circuit for a two-input LUT

x1 x2

f1

0

0

1

1

1

0

0

1

0

1

0

1

LUT ? contém células que

armazenam, São usadas para

implementar uma função

lógica

(b) f 1 = x 1 x 2 + x 1 x 2

x1

1

0

f1

0

1

x2

(c) Storage cell contents in the LUT

Capítulo 3 - Tecnologia de

Implementação

38

19

FPGA -

lookup table (LUT) de três entradas

x1

x2

0/1

0/1

0/1

0/1

f

0/1

0/1

0/1

0/1

x3

Capítulo 3 - Tecnologia de

Implementação

FPGA -

39

lookup table (LUT) + Flip Flop

Select

Out

Flip-flop

In 1

In 2

D

LUT

Q

In 3

Clock

Capítulo 3 - Tecnologia de

Implementação

40

20

FPGA Programada

x3

f

x1

x2

x1 0

0

0

x2

1

f1

x2 0

1

0

x3

0

f2

f1 0

1

1

f2

1

f

Exercício: Dê as

funções f, f1 e f2

Capítulo 3 - Tecnologia de

Implementação

41

Duas linhas de um circuito com tecnologia standard-cell

chip

f2

x1

x2

x3

f1

Capítulo 3 - Tecnologia de

Implementação

42

21

Um gate array - sea-of-gates

Capítulo 3 - Tecnologia de

Implementação

43

Exemplo de uma função lógica em um gate array

f1

x1

x2

x3

Capítulo 3 - Tecnologia de

Implementação

44

22

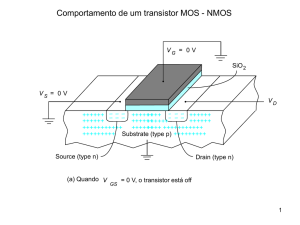

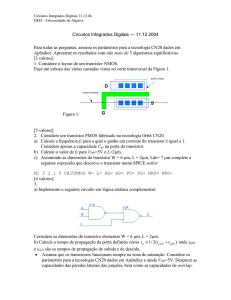

Comportamento de um transistor MOS - NMOS

VG = 0 V

SiO 2

VS = 0 V

VD

++++++

++++++ ++++ ++++++

++++ +++

++++++

++++++

++++++

++++++

++++ +++++++++++

+++++++++++ ++++++

+++++++++ Substrate (type p) +++++++++

Source (type n)

(a) Quando V

Drain (type n)

GS

= 0 V, o transistor está off

Capítulo 3 - Tecnologia de

Implementação

45

Comportamento de um transistor MOS - NMOS

VDD

VG = 5 V

SiO2

VS = 0 V

VD = 0 V

++++++ ++++

+++ ++++++

++++++

++++++

+++++++++++ +++++++++++++++++

+++++++++ ++ +++++++ ++++++++++

Channel (type n)

(b) Quando V = 5 V, o transistor está on

V

GS

GS

> V T ? há a formação do canal

Capítulo 3 - Tecnologia de

Implementação

46

23

Comportamento de um transistor MOS – NMOS

Comprimento e Largura de Canal

ID = k’nW / L [ ( VGS – VT ) VDS – ½ V2DS ]; (gráfico no próximo slide)

onde k’n é a transcondutância (parâmetro de processo – unidade A / V2

quando VDS = VGS – VT , a corrente atinge a máximo (saturação) e

ID = k’nW / L [ ( VGS – VT )2] ? independe de VDS

OBS – A análise para o PMOS é semelhante, só que teremos VS com a

maior tensão e VT negativo e K’p ~ 0,4 K’n

Exercício: Assumir k’n = 60 u A/V2, W/L = 2,0 um / 0,5 um, VS = 0. Se VD = 2,5,

qual a corrente ID na região de triodo e na região de saturação.

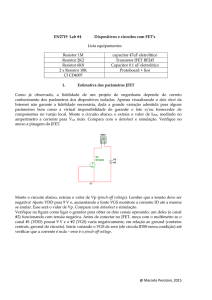

ON – Resistence em um MOSFET

RDS = VDS / ID ? RDS = 1/[k’n W/L (VGS – VT)]

Exercício: Assumir k’n = 60 u A/V2, W/L = 2,0 um / 0,5 um, VGS = 5V.

Calcular RDS.

Capítulo 3 - Tecnologia de

Implementação

47

Relação tensão-corrente em um transistor NMOS

I

ID

Triode

0

Saturação

VGS – VT

VDS

+

W1

+

W2

L

L

(a) Small transistor

(b) Larger transistor

Capítulo 3 - Tecnologia de

Implementação

48

24

Níveis de tensão em um inversor NMOS inverter

V

DD

V

DD

R

Vf

V f = VOL

I stat

Vx

RDS

(a) NMOS NOT gate

(b) V x = 5 V

OBS: Nos inversores

NMOS, geralmente o

resistor é um transistor

PMOS ? pseudo

PMOS ? compatível

com CMOS

VX = 0 ? NMOS aberto, sem fluxo de corrente ? Vf = 5V

VX = VDD ? Vf = VDD (RDS /(RDS + R))

Exercício: R = 25 KW e RDS -= 1KW. Calcular Isat e Vf

Capítulo 3 - Tecnologia de

Implementação

49

Curva de transferência de um inversor CMOS

VX = 0 ? NMOS off

Vf

Sem

fluxo de

VOH= VDD

Slope = -1

VX = VDD ? PMOS off

corrente

Na realidade existe uma pequena

corrente ? leakage current ? V0L =

0,1 mV

V0L, V1L, V0H e V1H ? quantifica a

robustez de uma família lógica

VOL = 0V

VT

VIL

VIH ??V – V ??VDD

DD

T

VDD

Vx

—

2

Capítulo 3 - Tecnologia de

Implementação

50

25

Margem de Ruído

N1

N2

A

x

f

Dois inversores em cascata

Ruído ? pertubações randômicas que podem alterar um sinal.

Por exemplo, a saída de N1 pode ser alterada por uma

pertubação externa (ruído).

Se este ruído alterar V1L de N1, este nível deve se manter

abaixo de V1L, para ser interpretado corretamente por N2.

A capacidade para tolerar ruídos sem afetar a operação

correta ? margem de ruído

NML = V1L – V0L

NMH = V0H – V1H

Capítulo 3 - Tecnologia de

Implementação

VDD

51

VDD

VA

Vx

Vf

C

Carga capacitiva no ponto A

Capítulo 3 - Tecnologia de

Implementação

52

26

Figure 3.48

Voltage waveforms for logic gates

V DD

Vx

50%

50%

Gnd

Propagation delay

Propagation delay

V DD

90%

VA

90%

50%

Gnd

50%

10%

10%

tr

tf

Capítulo 3 - Tecnologia de

Implementação

Figure 3.49

53

Transistor sizes

+

W1

+

W2

L

L

(a) Small transistor

(b) Larger transistor

Capítulo 3 - Tecnologia de

Implementação

54

27

Figure 3.50

Dynamic current flow in CMOS circuits

VDD

Vx

ID

ID

Vf

Vf

Vx

(a) Current flow when input Vx

changes from 0 V to 5 V

(b) Current flow when input Vx

changes from 5 V to 0 V

Capítulo 3 - Tecnologia de

Implementação

Figure 3.51

55

Poor use of NMOS and PMOS transistors

VDD

V DD

A

(a) NMOS transistor

B

(b) PMOS transistor

Capítulo 3 - Tecnologia de

Implementação

56

28

Figure 3.52

Poor implementation of a CMOS AND gate

Vf

Vx1

(a) An AND gate circuit

Voltage

Logic

value

x1 x2

Vf

f

1.5 V

1.5 V

1.5 V

3.5 V

0

0

0

1

0

0

1

1

VDD

Vx2

Logic

value

0

1

0

1

(b) Truth table and voltage levels

Capítulo 3 - Tecnologia de

Implementação

57

V DD

Figure 3.53

High fan-in NMOS NAND gate

Vf

Vx

1

Vx

2

Vx

3

Vx

k

Capítulo 3 - Tecnologia de

Implementação

58

29

Figure 3.54

High fan-in NMOS NOR gate

VDD

Vf

Vx1

Vx2

Vxk

Capítulo 3 - Tecnologia de

Implementação

Figure 3.55

The effect of fan-out on propagation delay

N1

x

f

59

Vf

To inputs of

x

n other inverters

To inputs of

n other inverters

Cn

(a) Inverter that drives n other inverters

(b) Equivalent circuit for timing purposes

V f for n =1

VDD

V f for n = 4

Gnd

0

Time

(c) Propagation times for different values of n

Capítulo 3 - Tecnologia de

Implementação

60

30

A noninverting buffer

Figure 3.56

VDD

Vx

Vf

(a) Implementation of a buffer

f

x

(b) Graphical symbol

Capítulo 3 - Tecnologia de

Implementação

Figure 3.57

Tri-state buffer

61

e= 0

x

e

x

f

f

e= 1

x

(a) A tri-state buffer

(b) Equivalent circuit

e x

f

e

0

0

1

1

Z

Z

0

1

x

0

1

0

1

f

(c) Truth table

Capítulo 3 - Tecnologia de

Implementação

f

(d) Implementation

62

31

Figure 3.58

Four types of tri-state buffers

e

e

f

x

f

x

(a)

(b)

e

e

f

x

f

x

(c)

(d)

Capítulo 3 - Tecnologia de

Implementação

Figure 3.59

63

An application of tri-state buffers

x1

f

s

x2

Capítulo 3 - Tecnologia de

Implementação

64

32

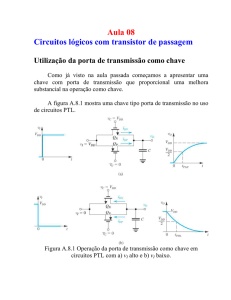

Figure 3.60

A transmission gate

s

x

s

f

0

1

Z

x

f

s

(b) Truth table

(a) Circuit

s = 0

x

s

f=Z

x

s = 1

x

f=x

f

s

(c) Equivalent circuit

(d) Graphical symbol

Capítulo 3 - Tecnologia de

Implementação

Figure 3.61 a

x1 x 2

0

0

1

1

0

1

0

1

65

Exclusive-OR gate

f = x1 ? ?x2

0

1

1

0

(a) Truth table

x1

f = x1 ? ?x2

x2

(b) Graphical symbol

x1

x2

f = x 1 ? ?x 2

(c) Sum-of-products implementation

Capítulo 3 - Tecnologia de

Implementação

66

33

Figure 3.61 b

CMOS Exclusive-OR gate

x1

x2

f = x1 ? ?x2

(d) CMOS implementation

Capítulo 3 - Tecnologia de

Implementação

Figure 3.62

67

A 2-to-1 multiplexer built using transmission gates

x1

s

x2

f

Capítulo 3 - Tecnologia de

Implementação

68

34

Figure 3.63

An example of a NOR-NOR PLA

x1 x2

x3

NOR plane

VDD

VDD

VDD

f1

f2

S1

VDD

S2

VDD

S3

NOR plane

Capítulo 3 - Tecnologia de

Implementação

69

Figure 3.64 A programmable NOR plane

x1

x2

xn

VDD

S1

VDD

S2

VDD

Sk

(a) Programmable NOR-plane

Ve

=

Ve

++++

+++++

+++++ +++++++++++

(b) A programmable switch (c) EEPROM transistor

Capítulo 3 - Tecnologia de

Implementação

70

35

Figure 3.65

x1

x2

x 3version

x 4 of a NOR-NOR PLA

A programmable

NOR plane

V DD

V DD

S1

S2

S3

S4

S5

S6

NOR plane

Figure 3.66

f2

f1

Capítulo 3 - Tecnologia de

Implementação

71

AxNOR-NOR

PLA

used

x2

x3

x 4 for sum-of-products

1

NOR plane

V DD

V DD

P1

P2

P3

P4

P5

P6

NOR plane

Capítulo 3 - Tecnologia de

Implementação

f1

f2

72

36

Figure 3.67

x1

PAL programmed to implement two functions

x2

x3

x4

VDD

P1

P2

f1

P3

P4

P5

f2

P6

NOR plane

Capítulo 3 - Tecnologia de

Implementação

Figure 3.68

x1 0

0

0

x2

1

73

Pass-transistor switches in FPGAs

Vf

f1

1

VA

1

0

0

SRAM

SRAM

SRAM

(to other wires)

Capítulo 3 - Tecnologia de

Implementação

74

37

Figure 3.69

Restoring a high voltage level

V DD

SRAM

1

VB

VA

To logic block

Capítulo 3 - Tecnologia de

Implementação

75

Plano NOR programável

x

x

1

x

2

n

VDD

S1

VDD

S2

VDD

Sk

(a) Plano Nor programável

Ve

=

Ve

(b) Chave programável

++++

+++++

+++++ +++++++++++

(c) Transistor EEPROM

Capítulo 3 - Tecnologia de

Implementação

76

38