FATEC - SP

Faculdade de Tecnologia de São Paulo

Projeto de Circuitos Integrados (PCI)

Profs. Victor Sonnenberg e João Antonio Martino

4o Experiência: Funções lógicas CMOS

Nome

Número

OBS. PREENHER O RELATÓRIO EM LETRA LEGÍVEL OU DE FORMA. Se necessário,

use folha extra ou o verso.

Objetivo: Projetar uma função lógica CMOS complexa utilizando portas lógicas ou a função

simplificada avaliando o comportamento estático e dinâmico e simulá-la com o microwind2.

Introdução:

ASSOCIAÇÃO “OR-NAND”:

Associação série/paralelo ou paralelo/série

Associação de transistores série / paralelo e paralelo / série é mais eficiente nas construções de níveis

lógicos com menor número de transistores.

Procedimento experimental:

Implementar a função lógica (F) descrita na tabela 1, utilizando as dimensões relacionadas e

a foundry CMOS12.RUL.

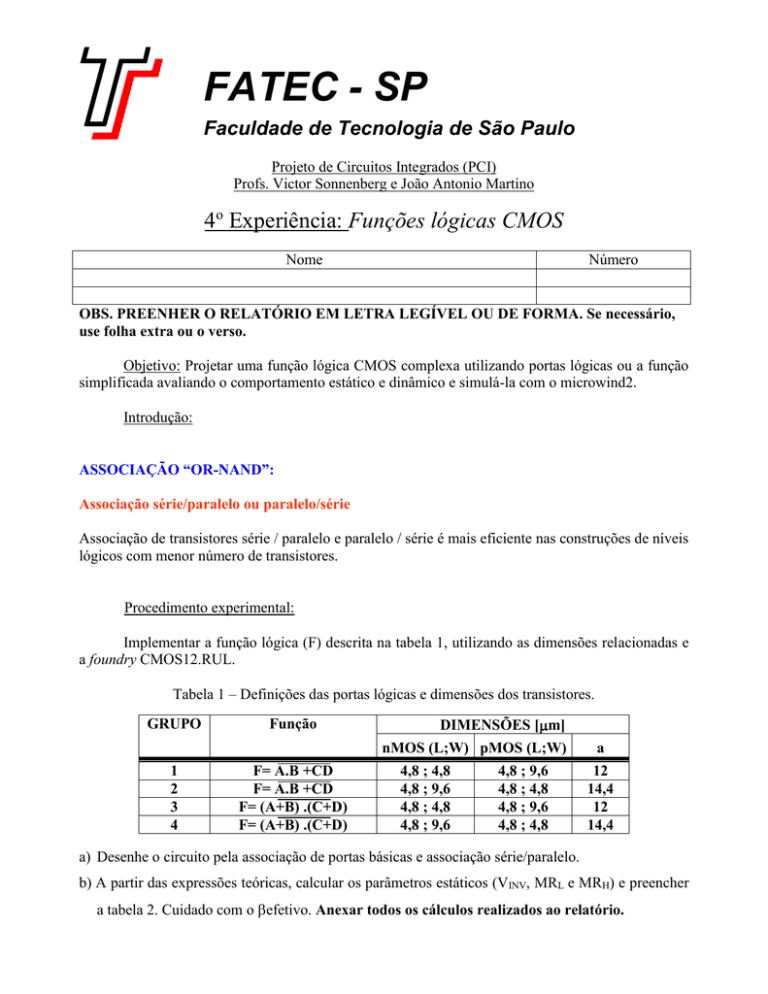

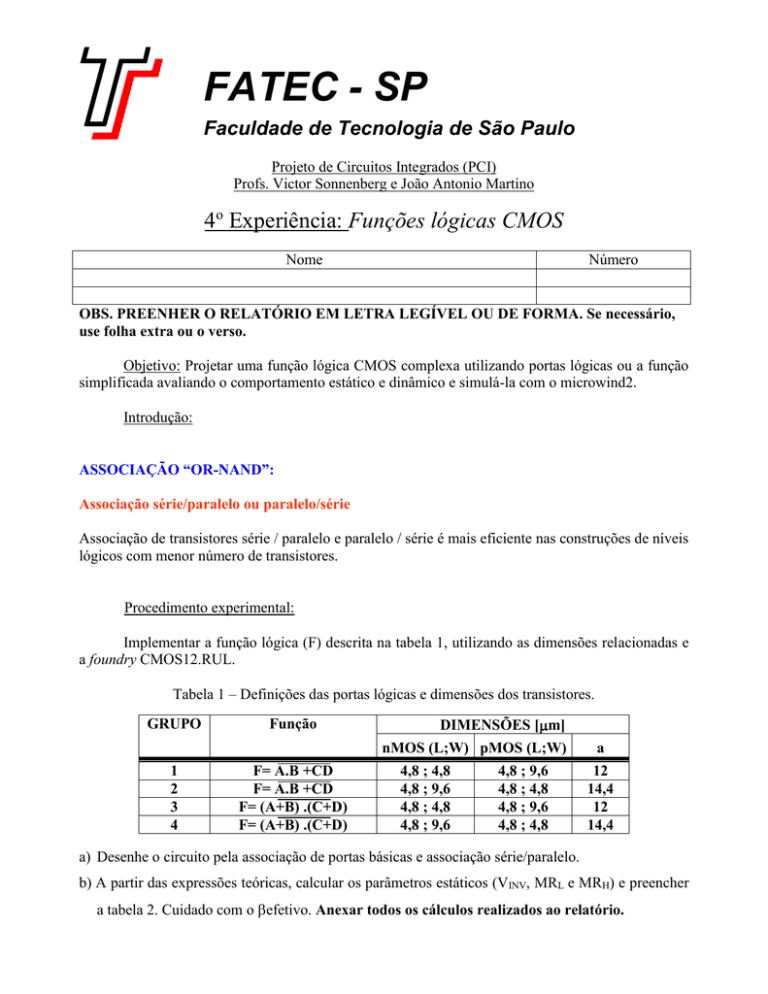

Tabela 1 – Definições das portas lógicas e dimensões dos transistores.

GRUPO

Função

DIMENSÕES [m]

nMOS (L;W) pMOS (L;W)

1

2

3

4

F= A.B +CD

F= A.B +CD

F= (A+B) .(C+D)

F= (A+B) .(C+D)

4,8 ; 4,8

4,8 ; 9,6

4,8 ; 4,8

4,8 ; 9,6

4,8 ; 9,6

4,8 ; 4,8

4,8 ; 9,6

4,8 ; 4,8

a

12

14,4

12

14,4

a) Desenhe o circuito pela associação de portas básicas e associação série/paralelo.

b) A partir das expressões teóricas, calcular os parâmetros estáticos (VINV, MRL e MRH) e preencher

a tabela 2. Cuidado com o efetivo. Anexar todos os cálculos realizados ao relatório.

FATEC - SP

Faculdade de Tecnologia de São Paulo

c) Implementar o leiaute (associação série/pararelo) no Microwind2 (verificar se não existem

infrações de regras de projeto, utilizando o botão DRC da barra de comandos) e anexar uma

cópia do mesmo ao relatório, indicando as dimensões em , através da régua.

d) Atribuir sinais de relógio, com tempos adequados (dobrando os valores), a cada uma das entradas

do circuito e realizar o teste da função lógica, através da curva Tensão x Tempo. Anexar uma

cópia da curva resultante ao relatório.

e) Curto-circuitar todas as entradas da porta lógica e realizar também a simulação das

características elétricas:

e1) observando o comportamento estático (sem capacitor), através da curva Tensão x Tensão,

e2) observando o comportamento dinâmico (com capacitor), através da curva Tensão x Tempo, da

porta lógica operando como um inversor. Para a realização da curva de transferência dinâmica

ligar uma capacitância de 1 pF ao nó de saída. Configurar o sinal de entrada de modo a permitir a

visualização das características dinâmicas do circuito. Para obter o valor da capacitância total

associada ao nó de saída (CL= _______ pF) deve-se pressionar duas vezes o botão do mouse na

linha de metal do nó de saída.

f) Com o valor de CL, calcular tr, tf e td para este circuito, completando a tabela 2.

Tabela 2 – Comparação entre os valores calculados e simulados.

Grandeza

Valores Calculados

Valores Simulados

VINV (V)

MRL (V)

MRH (V)

tr (ns)

tf (ns)

td (ns)

FATEC - SP

Faculdade de Tecnologia de São Paulo

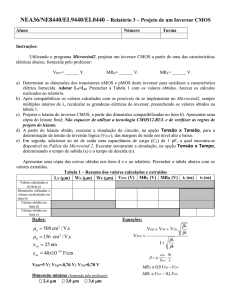

Si-poli

Diff P ou N

a

a

Figura 1 - Vista superior do transistor, indicando a variável a

Dados:

n=500 cm2/Vs ; p=156 cm2/Vs ; xox=25nm ;VDD=5 V; VTp=-0,76 V; VTn=0,70 V

Equações:

V

INV

N

V

V V

DD Tp Tn

1

N

P

.

OX W

.

XOX L

MRH 0,9.VDD VINV

MRL VINV 0,1.VDD

P

tr

4C L

P VDD

tf

4C L

N VDD

Conclusões:

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________

_________________________________________________________________________________