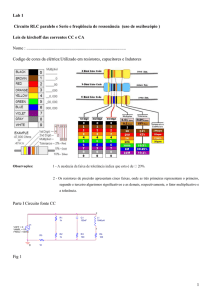

EN2719 Lab #4

Dispositivos e circuitos com FET’s

Lista equipamentos

Resistor 1M

Resistor 2K2

Resistor 6K8

2 x Resistor 10K

CI CD4007

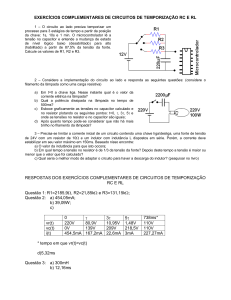

1.

capacitor 47uF eletrolítico

Transistor JFET BF245

Capacitor 0.1 uF eletrolítico

Protoboard + fios

Estimativa dos parâmetros JFET

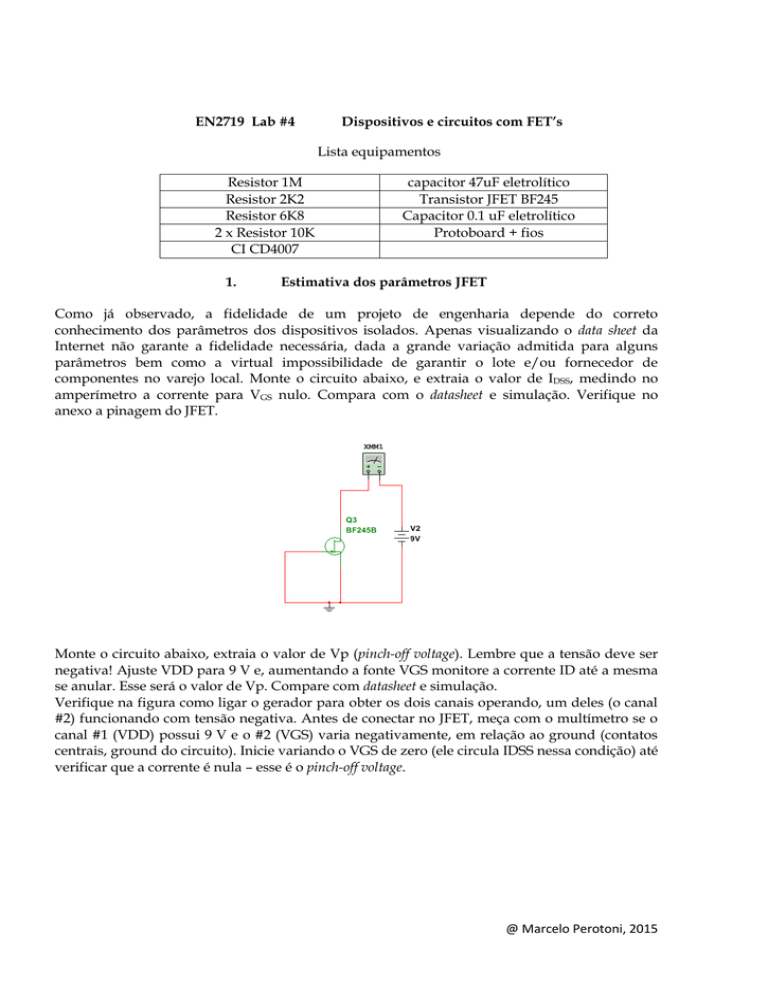

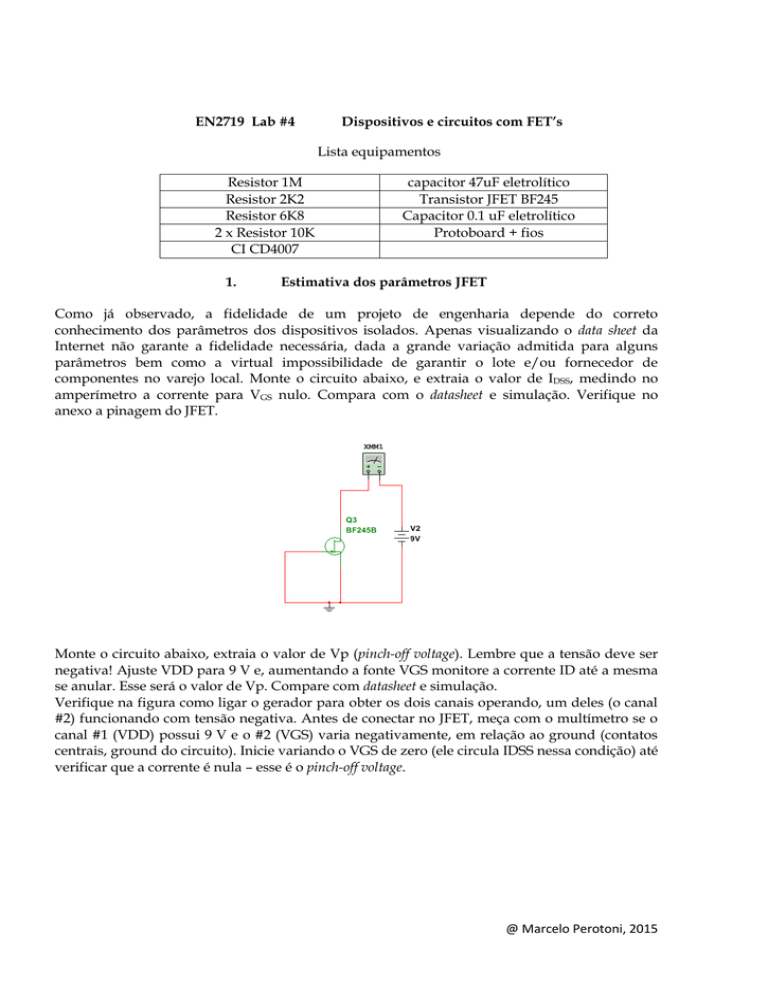

Como já observado, a fidelidade de um projeto de engenharia depende do correto

conhecimento dos parâmetros dos dispositivos isolados. Apenas visualizando o data sheet da

Internet não garante a fidelidade necessária, dada a grande variação admitida para alguns

parâmetros bem como a virtual impossibilidade de garantir o lote e/ou fornecedor de

componentes no varejo local. Monte o circuito abaixo, e extraia o valor de IDSS, medindo no

amperímetro a corrente para VGS nulo. Compara com o datasheet e simulação. Verifique no

anexo a pinagem do JFET.

Monte o circuito abaixo, extraia o valor de Vp (pinch-off voltage). Lembre que a tensão deve ser

negativa! Ajuste VDD para 9 V e, aumentando a fonte VGS monitore a corrente ID até a mesma

se anular. Esse será o valor de Vp. Compare com datasheet e simulação.

Verifique na figura como ligar o gerador para obter os dois canais operando, um deles (o canal

#2) funcionando com tensão negativa. Antes de conectar no JFET, meça com o multímetro se o

canal #1 (VDD) possui 9 V e o #2 (VGS) varia negativamente, em relação ao ground (contatos

centrais, ground do circuito). Inicie variando o VGS de zero (ele circula IDSS nessa condição) até

verificar que a corrente é nula – esse é o pinch-off voltage.

@ Marcelo Perotoni, 2015

2.

Amplificador JFET

Atenção: primeiro aplique o DC (fonte de tensão) e depois o AC (gerador de sinais). Do

contrário pode danificar o dispositivo.

Monte o amplificador abaixo. (a) Meça as tensões VS, VG, VDS e VD de polarização. (b) Ajuste o

gerador de sinais para um sinal de 1 kHz, com amplitude em torno de 100 mVpp e meça a saída

no dreno, COM e SEM o capacitor de 47 uF. Mostre numa tabela os valores do ganho para as

duas condições, bypassed e unbypassed. Compare com simulações e valores teóricos.

3.

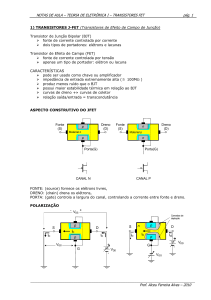

Estimativa dos parâmetros do MOSFET.

O Elvis infelizmente não traça a curva características de FETs/MOSFET’s. Para ter uma

estimativa dos parâmetros do MOSFET (NMOS) presente no chip CD4007 será montado o

circuito abaixo (maiores detalhes na referência [1]). Os números nas flechas correspondem aos

pinos do CI (veja anexo no fim do documento). Familiarize-se com o dispositivo antes de iniciar

ligando os fios. O chanfro corresponde ao pino 1 em cima, olhando de cima.

@ Marcelo Perotoni, 2015

Ajuste uma tensão de alimentação VDD DC que resulte em uma corrente de dreno de

aproximadamente 1 ou 2 mA. Vale a regra da equação da região de saturação (está saturado por

hardware dada a conexão Gate/Dreno):

(1)

Agora aumente a tensão VDD de maneira que a corrente medida no amperímetro seja quatro

vezes maior.

(2)

As duas expressões podem ser combinadas de maneira a:

(3)

Uma vez que Vt foi encontrada, Kn pode ser determinado retornando à expressão (1).

Realize o procedimento novamente, para uma corrente Id maior (em torno de 5 mA). Compare

os parâmetros Vt e Kn encontrados para as duas condições, apresentando-os numa tabela.

4.

Amplificador de tensão MOSFET NMOS

Atenção: primeiro aplique o DC (fonte de tensão) e depois o AC (gerador de sinais). Do

contrário pode danificar o dispositivo.

Monte o circuito abaixo. Os números nas flechas correspondem aos pinos do CI CD4007. Ajuste

a tensão V1 no gerador de maneira ter a tensão DC no ponto vo em 5 V, para obter máxima

excursão simétrica. Em seguida aplique um sinal senoidal de 400 mV pico a pico, com 5 kHz na

entrada, através do capacitor. Apresente o valor dos sinais de entrada e saída AC, e do ganho

de tensão.

Aumente a amplitude do sinal de entrada até perceber distorções no sinal. Usando os recursos

de FFT do osciloscópio mostre o espectro de potência COM e SEM distorção, explicando o

visualizado.

@ Marcelo Perotoni, 2015

Anexo

CD4007 pinout

Cuidado: Pinos 14 SEMPRE conectado

em VDD (tensão positiva) e 7 em VSS

(ground), independente dos demais

pinos ou transistores serem usados ou

não

@ Marcelo Perotoni, 2015

BF245 pinout

Bibliografia:

[1] http://www.ece.ucsb.edu/Faculty/rodwell/Classes/ece2c/labs/Lab_2_2C_2007.pdf

[2] http://www.seas.upenn.edu/~ese206/labs/MOSFET/MOSFETLab1.pdf

@ Marcelo Perotoni, 2015