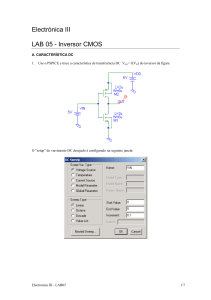

Aula 03

O inversor CMOS

Nesta seção, abordaremos aspectos relacionados ao uso do

transistor CMOS como chave, investigando seu desempenho e

explorando diversas potencialidades disponíveis em seu projeto.

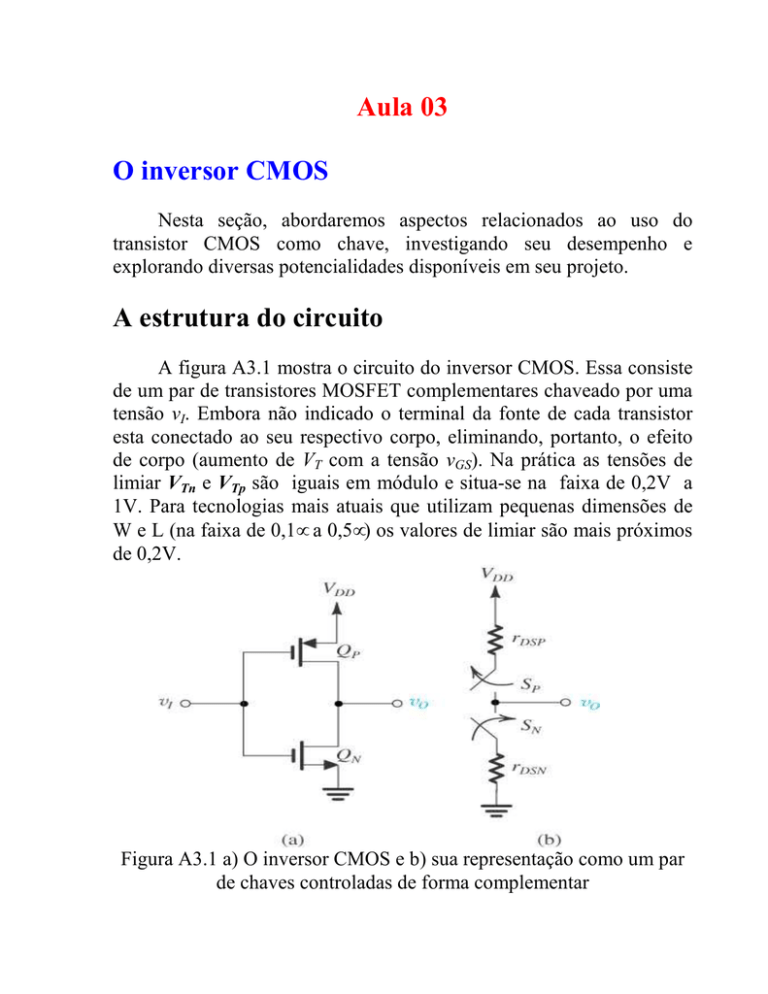

A estrutura do circuito

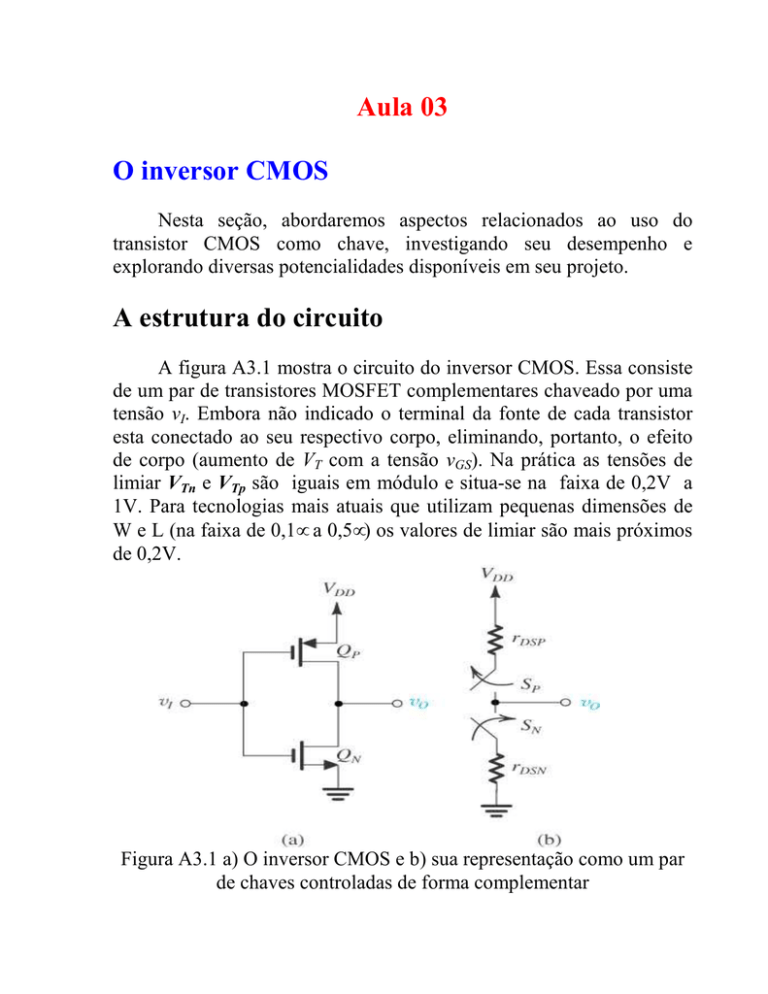

A figura A3.1 mostra o circuito do inversor CMOS. Essa consiste

de um par de transistores MOSFET complementares chaveado por uma

tensão vI. Embora não indicado o terminal da fonte de cada transistor

esta conectado ao seu respectivo corpo, eliminando, portanto, o efeito

de corpo (aumento de VT com a tensão vGS). Na prática as tensões de

limiar VTn e VTp são iguais em módulo e situa-se na faixa de 0,2V a

1V. Para tecnologias mais atuais que utilizam pequenas dimensões de

W e L (na faixa de 0,1µ a 0,5µ) os valores de limiar são mais próximos

de 0,2V.

Figura A3.1 a) O inversor CMOS e b) sua representação como um par

de chaves controladas de forma complementar

Como indicado cada chave é modelada por uma resistência finita,

que é a resistência entre o dreno e a fonte do respectivo transistor,

calculada próximo de | vDS| = 0:

W

rDSN = k , n (VDD − VT )

L n

A3.1

W

rDSP = k , p (V DD − VT )

L p

A3.2

Onde k`n = µn Cox e k`p = µp Cox são os parâmetros de transcondutância

do processo, sendo, µn e µp as mobilidades do portadores (dos elétrons

e buracos) no canal n e p respectivamente, e Cox é a capacitância por

unidade de áreas dos transistores.

Operação estática

Faremos agora uma análise estática do inversor. Para vI = 0, temos

vO = VOH = VDD, pois o nó de saída fica conectado a VDD por meio da

resistência rDSP do transistor Qp de carga. De forma análoga, com vI =

VDD, temos vO = VOL = 0, porque o nó de saída para a estar conectado

ao terra por meio do resistor rDSN do transistor de comando Qn.

Portanto, no estado estacionário, não nenhum caminho entre VDD e o

terra, e a corrente estática e a dissipação de potência estática são ambas

nulas.

A característica de transferência de tensão (CTT) do inversor é

mostrada na figura A3.2, na qual é fácil ver que os níveis de tensão são

0 V e VDD. E, portanto, a excursão de tensão de saída é justamente a

máxima possível.

Note que VOH e VOL são independentes as dimensões dos

transistores, o que torna a tecnologia CMOS bem diferente de outras

tecnologias.

Figura A3.2 A característica de transferência de tensão de um inversor

CMOS quando Qp e Qn são casados.

A transição de um estado lógico na saída do inversor CMOS pode

ser projetada de forma a ocorrer exatamente no meio da excursão lógica

entre 0 V e VDD, isto é, em VDD/2, se escolhermos de forma apropriada

as dimensões dos transistores. Especificamente, é fácil demonstrar que

a tensão de transição Vth (ou VM) é dada por

Vth =

VDD − Vtp +

1+

( )

,

Onde k n = k n W L

Kp’ = µp Cox

n

kn

kn

kp

Vtn

(A3.3)

kp

( L ) sendo k

k p = k p, W

e

p

’

n

= µn Cox e

Exercício A3.1

Para um caso típico em que VTn e VTp são iguais em módulo

mostre que Vth = VDD/2 para kn = kp , onde

( L ) = k (W L ) = k

k n = k n, W

,

n

p

p

p

Assim, o exercício anterior mostra quando os dispositivos são

projetados a ter os parâmetros de transcondutância idênticos

(casamentos dos transistores) a característica de transferência é

simétrica.

Desta forma uma característica de transferência simétrica pode ser

obtida quando os dispositivos forem projetados de forma a ter

parâmetros de transcondutância idênticos, que é uma condição que

costuma ser denominada de casamentos de transistores. Uma vez que

µn é duas a quatro vezes maior que µp, o casamento é obtido fazendo

(W/L)p de duas a quatro vezes (µn/ µp vezes) maior que (W/L)n,

µ W

W

= n

P p µ p L n

(A.3.4)

Normalmente, fazem-se os comprimentos de canal, L, dos

transistores do inversor idênticos e iguais a mínima dimensão permitida

pela tecnologia. Assim para garantir o casamentos escolhe-se a razão

das larguras W`s dos transistores de forma adequada. A largura mínima

é normalmente escolhida de uma vez a uma vez e meia maior que a

dimensão mínima.

Por exemplo, para um processo ou tecnologia CMOS com

dimensões mínimas de 0,25 µm, para o qual µn/ µp = 3, teremos L =

0,25 µm, (W/L)n = 0,375 µm/0,25µm e (W/L)p = 1,125 µm/0,25µm.

Se, entretanto, o inversor tiver que fornecer uma corrente para

uma carga relativamente grande, os transistores terão de ter uma largura

muito maior que a dimensão mínima.

Além de fazer com que a tensão de transição fique no centro da

excursão lógica, o casamento dos transistores implica num mesmo

parâmetro de transcondutância fazendo com que ambos os transistores

tenham a mesma capacidade de corrente tanto carregamento como no

descarregamento da capacitância de carga. Além disso, obviamente,

teremos rdsn = rdsp. Portanto, um inversor com transistores casados

apresenta atrasos na propagação iguais, tPLH e tPHL.

Exemplo A3.2

Mostre que se o limiar de transição do inversor está em VDD/2, as

margens de ruído MRH e MRL são iguais e seus valores são

maximizados e dado por

MRH = MRL = 3/8(VDD +2/3VT)

Solução:

Para resolver este exercício vamos reproduzir a CTT do inversor

identificando a regiões de operação dos transistores canal n e canal p na

curva de transferência do inversor como mostra a figura A3.3.

Figura A3.3 Curva de transferência de tensão do inversor

Devemos lembrar das aulas anteriores que, além dos VOL e VOH,

dois outros pontos da curva de transferência determinam as margens de

ruído do inversor. São eles o máximo nível lógico `0` permitido na

saída, VIL, e o mínimo nível lógico `1` na saída, VIH. Para uma região

de transição linear esses níveis eram o início e o fim da transição.

Agora estes são formalmente definidos como os dois pontos na curva

de transferência em que o ganho incremental de tensão é unitário (isto

é, inclinação = -1).

Para determinar VIL, devemos notar que Qn está na região de

triodo e, portanto, sua corrente é igual a corrente de Qp que está na

região de saturação, assim temos

1

1

2

(vI − VT )v0 − v02 = (VDD − vI − VT )

2

2

(A3.5)

Diferenciando ambos os membros em relação a vI resulta em:

(v

I

− VT )

dv0

dv

+ v0 − v0 0 = −(VDD − vI − VT )

dvI

dvI

(A3.6)

na qual podemos agora substituir vI = VIH e dv0/dvI = -1 para obter:

v0 = VIH −

VDD

2

(A3.7)

e substituindo vI = VIH e v0 da equação (A3.7) na equação (A.3.6),

resulta:

VIH =

1

(5VDD − 2VT )

8

(A3.8)

Tendo em vista a simetria da característica de transferência de

tensão do inversor, VIL pode ser determinado de forma similar. Ou de

forma alternativa, da figura, temos

VIH −

VDD VDD

=

− VIL

2

2

(A3.9)

Substituindo esta última em (A.3.7), permite obter:

1

VIL = (3VDD + 2VT )

8

(A.3.10)

As margens de ruído podem agora ser determinadas como segue

MRH = VOH – VIH

=

VDD – 1/8(5VDD – 2)

=

3/8(VDD + 2/3 VT)

c.q.d

e

MRL = VIL – VOL

=

1/8 (3 VDD + 2VT) – 0

=

3/8(VDD + 2/3 VT)

c.q.d

Conforme esperado, a simetria da característica de transferência

resulta em margens de ruído iguais. Certamente se Qn e Qp não

estiverem casados, a característica de tensão não será simétrica, e as

margens de ruído não serão iguais.

Embora tenhamos enfatizado bastante as vantagens de casar os

transistores do inversor CMOS, há ocasiões em que essa solução não é

adotada. Poderíamos, por exemplo, piorar o casamento em favor da

redução da área da pastilha de silício e, assim, fazer (W/L)p =(W/L)n. há

também circunstâncias em que um descasamento deliberado é

empregado de forma a ter a tensão de transição em um valor

especificado diferente de VDD/2.

Em que sentido move-se Vth quando aumentamos a relação kn/kp?

Exercícios:

A3.1) Para um inversor CMOS com MOSFET`s casados com VT = 1 V,

obtenha VIL , e VIH e as margens de ruído se VDD = 5 V.

A3.2) Considere um inversor CMOS com VTn e VTp iguais em módulo

a 2 V, (W/L)n = 20, (W/L)p = 40, µn Cox = 2. µp Cox = 20µA/V2 e VDD =

10 V. Para vI = VDD, obtenha a corrente máxima que o inversor pode

drenar enquanto vO ≤ 0,5 V.

A3.3) Mostre que a tensão de transição Vth de um inversor CMOS é

dada por

Vth =

sendo

r (VDD − Vtp ) + Vtn

1+ r

r=

kp

kn

Operação dinâmica

O atraso na propagação de sinal do inversor é normalmente

determinado na condição em que se tem um inversor idêntico

conectado na saída. Essa situação é mostrada na figura A3.4.

Figura A3.4 Circuito para análise do atraso de propagaçao do

inversor formado por Q1 e Q2, que alimenta um inversor identico

formado por Q3 e Q4.

Analisaremos esse circuito para determinar a atraso na

propagação de sinal no inversor formado pelos transistores Q1 e Q2.

Esse inversor está “sendo alimentado”por uma fonte de sinal vI de baixa

impedância de saída e ao mesmo tempo, está carregado pelo inversor

formado pelos transistores Q3 e Q4. Também estão indicadas na figura

as diversas capacitâncias internas dos transistores que estão conectadas

ao nó de saída do inversor formado por Q3 e Q4. Obviamente, uma

análise exata à mão desse circuito seria complicada demais e não

acrescentaria muita a compreensão da forma de projetar um circuito,

por isso tentaremos simplificar a análise. Especificamente, poderíamos

substituir todas as capacitâncias conectadas ao nó de saída do primeiro

inversor por uma única capacitância de carga C conectada entre o nó de

saída e o terra. Se formos capazes de fazer isso, poderemos realizar

uma análise transitória adiante bem mais simples.

Com este objetivo, notamos que durante os tempos tPLH ou tPHL, a

saída do primeiro inversor muda de 0 para VDD/2 ou de VDD para VDD/2,

respectivamente. Segue que o segundo inversor permanece no mesmo

estado durante cada um dos intervalos de análise citados. Essa

observação será útil na estimativa da capacitância de entrada do

segundo inversor. Consideraremos agora a contribuição de cada uma

das capacitâncias equivalente C .

1) A capacitância de sobreposição porta-dreno de Q1, Cgd1, e a

capacitância de sobreposição porta-dreno de Q2, Cgd2, podem

ser substituída por uma capacitância entre o nó de saída e o

terra de 2(Cgd1 + Cgd2) . O fator 2 é um grosseira aproximação

que existe em decorrência do efeito Miller e assumindo que o

ganho do inversor na região de transição é igual -1.

2) As capacitâncias dreno-corpo de Q1 e Q2, Cdb1 e Cdb2

respectivamente, ambas tem um dos terminais conectado a

uma tensão constante. Portanto, do ponto de vista de nossa

análise transitória (AC), Cdb1 e Cdb2 podem ser substituídas por

capacitância iguais entre o nó de saída e o terra. Além disso,

vamos admitir que estas capacitâncias são iguais tanto para

pequeno quanto grandes sinais.

3) Uma vez que o segundo inversor, por hipótese, ainda não

mudou de estado, vamos supor que as capacitâncias de entrada

de Q3 e Q4 sejam aproximadamente constante e iguais à

capacitância total de porta (WLcox + Cgsov + Cgsov). Isto é, a

capacitância de entrada do inversor de carga será

Cg3 + Cg4 = (WLcox + Cgsov + Cgsov)Q3 + (WLcox + Cgsov + Cgsov)Q3

*Obs: note que escrevemos cox com letra minúsculas já que esta

representa uma capacitância de porta por unidade de área.

4) A última capacitância é a capacitância de interconexão entre

inversores Cw, que simplesmente deve adicionada ao valor de C.

Logo, o valor total de C é dado por

C = Cg3 + Cg4 + Cdb1 + Cdb2 +2(Cgd1 + Cgd2) +Cw

(A3.11)

Desta forma, tendo determinado um valor aproximado para

capacitância equivalente entre o nó de saída do primeiro inversor e o

terra, podemos agora utilizar os circuitos da figura A3.5 para encontrar

uma expressão aproximada para determinar tPHL e tPLH. Como os

circuitos são semelhantes um resultado de um aplica-se ao outro.

Vamos analisar o circuito da figura A3.4 de duas formas para

encontrar um valor aproximados dos tempo de atraso na propagação.

Note que antes de encontra o valor preciso para este tempo, o mais

importantes para o projetista é obter uma equação simplificada que

mostre os efeitos dos diversos elementos presentes que determinam o

atraso do inversor. Para uma análise bem mais precisa utiliza-se de

simulação computacional.

Esta questão é relevante para que o projetista consiga obter uma

visão mais comportamental de qualquer circuito estudado e assim

consiga entender de fato o circuito.

Figura A.3.5 a) Circuito equivalente; b) formas de onda de entrada e

saída; c) trajetória do ponto de operação; d) circuito equivalente

durante a descarga.

A figura A.3.5 c) mostra o inversor com o capacitor equivalente

de saída C entre o nó de saída e o terra, agora chamamos Q1 e Q2 de QP

e QN . Como já mencionado o inversor é acionado por um pulso ideal

conforme mostrado na figura A3.5 b).

Supondo transistores casados, os tempos de descida e subida da

forma de onda de saída são iguais. Usaremos o processo de liga para

análise.

A figura A3.6 c) mostra a trajetória do ponto de operação obtido

quando o pulso de entrada vai de VOL = 0 para VOH = VDD no instante

t=0. Imediatamente antes da transição do pulso de entrada (isto é, em

t=0-), a tensão de saída é igual a VDD e o capacitor C esta carregado

com esta tensão. Em t=0, vI passa subitamente para VDD, fazendo QP

corte imediatamente (comparado com os outros tempos). Nessa

situação, o circuito equivalente passa a ser aquele mostrado na figura

A.3.5 d) com valor inicial de vO = VDD. Portanto o ponto de operação

em t= 0+ é o ponto E, no qual pode ser visto que o transistor QN estará

na região de saturação e conduzindo um valor de corrente constante. A

medida que C descarrega, a corrente em QN permanece constante até

vO= VDD - VT ( ponto F). Apontando este trecho em que o capacitor

descarrega de tPHL1, é deixado como exercício para o aluno mostrar

que :

t PHL1 =

CVt

1 ' W

2

k n (VDD − VT )

2 L n

(A3.12)

Além do ponto F, o transistor QN opera na região triodo e

portanto, sua corrente é dada pela equação:

1

W

iD = k n' (vI − VTn )vO − vO2

2

L n

(A3.13)

Este trecho de descarga é descrito por:

iD dt = −CdvO

(A3.14)

Substituindo iD da equação (A3.13) e rearranjando a equação

diferencial, obtemos (É deixado como exercício) para VT = 0,2 VDD

t PHL

1,6C

≅ '

k n W VDD

Ln

( )

(A3.15)

Uma análise similar pode ser feita para o processo de desliga,

resultando em uma expressão para tPLH idêntica a equação (A.3.15), é

claro, exceto o termo k n' (W L )n que deve ser trocado por k p' (W L ) p . O

atraso de propagação será dado como a média dos tempos de atraso na

subida e descida do sinal.

O importante é observar e verificar que, para obter menores

tempos de atrasos na propagação e, portanto maior velocidade, deve-se

procurar alcançar os requisitos:

1. O capacitor C deve ser minimizado;

2. Um valor elevado para o parâmetro de transcondutância do

processo deve ser utilizado;

3. A razão W/L deve ser aumentada e;

4. A tensão de alimentação VDD deve ser elevada.

Entretanto, há, certamente, compromissos d projeto e os limites

físicos envolvidos em todas as possíveis escolhas apresentadas.