Realização de circuitos lógicos

João Paulo Cerquinho Cajueiro

19 de agosto de 2009

A álgebra de Boole já existia desde 1854, mas passou décadas sendo utilizada

apenas por matemáticos em estudos lógicos e estatı́sticos.

E com o advento e utilização de circuitos elétricos, alguns circuitos lógicos

eram implementados sem nenhuma base matemática, em casos simples, tais

como: qual a ligação de chaves que fazem com que uma lâmpada acenda se

qualquer uma das chaves estiver acionada (resposta: paralelo).

O engenheiro Claude Shannon desenvolveu em sua tese de mestrado1 de

1937 um método de projetar circuitos chaveados (que são circuitos com base

em chaves/relês liga/desliga) com base na álgebra de Boole. Basicamente ele

mostrou que se podia analisar um circuito chaveado pela álgebra de Boole —

diz-se que há um isomorfismo entre os dois sistemas — permitindo que todos os

teoremas já existentes na álgebra de Boole pudessem ser utilizados no projeto e

simplificação de circuitos.

Os circuitos utilizados por Shannon eram circuitos com relês, que ainda

são bastante utilizados na indústria, portanto iniciaremos a análise de circuitos

lógicos por eles. Depois foram desenvolvidas as chamadas portas lógicas, que

implementam as funções lógicas em circuitos integrados, atualmente utilizando

a tecnologia CMOS, que será estudada em seguida.

1

Relês e circuitos chaveados

Um relê nada mais é que uma chave controlada por tensão. Originalmente eletromecânicos hoje em dia existem os chamados relês de estado sólido, implementado por transistores ou triacs, que normalmente são mais rápidos e duráveis,

embora tipicamente suportem menor potência.

Ainda hoje há várias aplicações que utilizam relês, principalmente em ambientes industriais, que trabalham com altas tensões e correntes e em baixa

velocidade. Utilizam-se também os chamados contatores, que nada mais são do

que relês trifásicos.

Um relê eletromecânico é um chave que se mantém normalmente fechada ou

aberta pela ação de uma mola e que é aberta (ou fechada) por um eletroimã.

Ou seja, ao se magnetizar este eletroimã o relê abre (ou fecha) e se mantém

fechado (ou aberto) sem esta magnetização. Utilizando esta idéia básica podese descrever um relê em um diagrama esquemático apenas como um indutor e

uma chave (vide figura 1).

1 considerada

por alguns como a tese de mestrado mais relevante do século

1

V1

carga

V2

Figura 1: Um relê em um diagrama esquemático.

Existem dois tipos básicos de relê: relê normalmente aberto e normalmente

fechado. Também é comum relês que tenham 2 ou mais chaves acionadas por

uma mesma bobina.

Em geral é mais fácil analisar um circuito do ponto de vista lógico separando

a parte de acionamento da parte de controle, então o sı́mbolo de um relê é separado em duas partes: a bobina (o eletroimã) e o contato (a chave), interligados

pelo mesmo nome.

1.1

Diagrama Ladder

Os diagramas ladder são muito utilizados para representar a ligação de circuitos

, os contatos normalcom relês. Neste diagrama as bobinas tem o sı́mbolo

mente abertos são simbolizados por

e os normalmente fechados por

.

Para entender este tipo de diagrama, veja o mesmo circuito da figura 1

descrito em ladder na figura 2.

L1

L2

X1

carga

X1

Figura 2: Um relê em ladder.

Logo de cara nota-se que não existem neste diagrama as tensões V1 e V2.

Isto se dá pois neste diagrama considera-se que as tensões estão entre as duas

barras L1 e L2 e abstrai-se a fonte de tensão (mas na prática não se desenha

circuitos com tensões diferentes no mesmo diagrama ladder, mas se usa dois

diagramas separados — chamados de duas redes em ladder). Este esquema com

as linhas em aparalelo nas extremidades é parecido com uma ligação real, já que

passa o cabo com a tensão e o terra e os circuitos são conectados em paralelo.

Com os circuitos conectados desta maneira, o diagrama fica parecendo uma

2

escada; daı́ o nome2 . Com este tipo de diagrama, fica fácil analisar a lógica por

trás dos circuitos. Tanto é que ele é uma das formas utilizadas para programar

CLP’s.

Por exemplo, a figura 3 mostra exemplos de diagramas ladder que acendem

uma lâmpada apenas quando 2 relês são acionados, se qualquer um dos relês for

acionado ou quando nenhum dos relês é acionado.

L1

L2 L1

L2

S1

X1

S1

X1

S2

X2

S2

X2

X1

X1

X2

X2

(a) Aciona apenas se ambos relês estiverem (b) Aciona se um ou outro relê estiver aciacionados.

onado.

L1

L2

S1

X1

X1

(c) Aciona se o relê não estiver acionado.

Figura 3: Exemplos de circuitos lógicos chaveados em ladder.

Note-se então que uma ligação em série realiza um e lógico, uma ligação

paralelo realiza um ou lógico e o uso de um contato normalmente fechado realiza

a inversão lógico, ou o não. Ao vermos álgebra de Boole observaremos que a

combinação destes três circuitos permite realizar qualquer condição lógica para

o acionamento do que quer que seja.

Um exemplo um pouco mais complexo é um circuito que acione uma comporta de um incinerador e acione um alarme se os sensores do incinerador estiverem em desacordo, vide figura 4.

Este sistema tem uma comporta P , um botão que aciona esta comporta

2 em

inglês ladder significa escada.

3

B

P

SG

SL

ST

Figura 4: Diagrama de um incinerador industrial.

(B) e 3 sensores: SL , que checa se há chama através da luminosidade; ST , que

checa se há chama através da temperatura e SG , que checa se há gás sendo

queimado. A figura 5 mostra um diagrama ladder de um circuito que controla

este incinerador.

L1

L2

SL

ST

SL

SG

ST

SG

B

P

Figura 5: Diagrama ladder de controle do incinerador.

2

2.1

Circuitos Lógicos CMOS

Transistores nMOS e pMOS

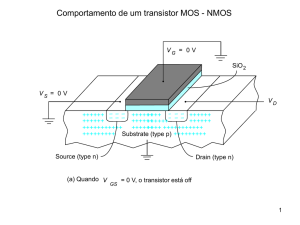

O semicondutor (silı́cio) pode ser dopado com impurezas doadoras de elétrons,

recebendo o nome de silı́cio tipo n, ou impurezas aceitadoras de elétrons, recebendo o nome de silı́cio tipo p. Basicamente o silı́cio tipo n tem a camada

de valência cheia e elétrons livres na camada de condução enquanto que o tipo

p tem a camada de condução vazia e várias lacunas (orbitais sem elétrons) na

camada de valência. Em ambos os casos consegue-se uma resistência mais baixa

que o silı́cio intrı́nseco. Por enquanto vamos considerar que não passa corrente

entre um silı́cio p e um n3 .

3 Obviamente não é verdade, vide um diodo de junção, mas para o uso normal de um

transistor MOS pode-se considerar isto.

4

O nome MOS é uma sigla que significa Metal-Óxido-Semicondutor. Esta

sequência de materiais implementa o chamado capacitor MOS (já que o óxido

de silı́cio é isolante elétrico), responsável pelo funcionamento dos transistores

MOS. A figura 6 mostra a vista em corte de 2 transistores: um nMOS (sobre

substrato p) e regiões n ao lado do capacitor e um pMOS (trocando n por p e

vice-versa). O terminal do metal é chamado de porta e os dois terminais das

regiões do lado do capacitor são chamados de dreno e fonte.

VDD

n+

A

B

n+

A

p+

VSS

p+

n

p

Figura 6: Vista em corte de transistores nMOS e pMOS — tecnologia CMOS.

Para circuitos lógicos, podemos inicialmente considerar o transistor como

uma chave entre dreno e fonte controlada pela tensão entre porta e fonte (VGS ).

Para tensões VGS negativas ou positivas mas baixas não existe ligação entre

dreno e fonte e o transistor apresenta uma resistência praticamente infinita (a

resistência entre dreno e fonte de um transistor aberto é superior a 1 MΩ),

mas acima de uma tensão limiar VT h , juntam-se elétrons suficientes embaixo do

capacitor de modo que esta região atua como se fosse um silı́cio n (diz-se que há

a inversão do silı́cio), formando um canal entre dreno e fonte. a resistência do

transistor ligado varia de centenas de Ohms a alguns quiloOhms, dependendo

da tecnologia e da geometria do mesmo e da tensão aplicada.

Logo, Um nMOS fica aberto quando VGS ≤ VT h e fechado quando VGS >

VT h .

Um transistor pMOS tem o mesmo funcionamento, sendo que neste caso é

necessário formar um canal p, então tanto VGS quanto VT h são negativos, ou

seja, ele fica aberto quando VGS ≥ VT h e fechado quando VGS < VT h e VT h é

negativo.

2.2

Inversor CMOS

Um inversor é a porta lógica mais simples da tecnologia CMOS, mas o princı́pio

de funcionamento de vários circuitos CMOS já está presente nele, o que faz do

inversor o circuito óbvio a começar a se estudar lógica CMOS. Porém, antes

de estudarmos o inversor CMOS, vamos estudar dois outros circuitos inversores

com transistores MOS.

Um inversor pode ser feito utilizando apenas um transistor MOS canal n

(nMOS) e um resistor (figura 7.a) ou, de modo similar, um transistor MOS

canal p (pMOS) e um resistor (figura 7.b). Vamos analisar primeiro o inversor

nMOS.

Quando ent é VSS (VSS é normalmente a menor tensão do circuito) no

circuito 7.a, a tensão VGS deste transistor é zero, logo ele age como uma chave

aberta. Nesta situação não há corrente passando pelo resistor e a tensão na

saı́da sai é VDD (a maior tensão do circuito, em geral). Ao se aplicar VDD em

ent, o transistor liga e o circuito funciona como o divisor resistivo série R e RON

(onde RON é a resistência do transistor ligado). Se R >> RON , então a tensão

5

sai se aproximará de VSS. Vê-se então que este circuito funciona adequadamente

como um inversor lógico, pois sai = ent.

Pode-se realizar esta mesma análise para o inversor pMOS, lembrando apenas

que este transistor trabalha com tensões negativas, Repetindo a análise, chega-se

a conclusão que sai chega próximo de VDD quando ent é VSS (pois o transistor

está ligado) e que sai é VSS quando ent é VDD (pois o transistor está desligado).

Estes dois circuitos funcionam adequadamente como inversores, mas apresentam alguns problemas. Os principais são que o circuito consome potência em

um estado e que um resistor de alto valor ocupa uma grande área. Na verdade o

segundo problema pode ser contornado usando um outro transistor polarizado

de modo a ter uma resistência alta, mas o problema da potência continua. Se o

transistor está ligado, há um caminho de resistência finita ligando VDD e VSS

consumindo energia. Num único inversor esta é uma potência pequena, mas ela

alcança nı́veis absurdos quando se fala de um circuito com milhares ou milhões

de portas lógicas.

O inversor nMOS consome potência sempre que a entrada é VDD, enquanto

que o pMOS consome sempre que a entrada é VSS, ou seja, eles consomem

potência em estados complementares. Um inversor CMOS se utiliza disto para

que não haja consumo de potência em nenhum estado.

A figura 8 apresenta o diagrama esquemático de um inversor MOS complementar (ou CMOS). Este circuito consiste de apenas 2 transistores: um nMOS

(M1) e um pMOS (M2). A fonte do nMOS liga a VSS e a fonte do pMOS liga

a VDD. A entrada é conectada às portas dos 2 transistores e a saı́da vem dos

drenos dos 2 transistores. Quando a entrada é VSS, o M1 fica desligado e o

M2 ligado, logo a saı́da fica ligada à VDD. Para uma entrada igual a VDD, o

M2 desliga e o M1 liga, conectando a saı́da à VSS. Ele funciona adequadamente

como um inversor, mas não existe um caminho de corrente entre VDD e VSS em

nenhum dos dois estados. Logo este circuito não consome energia em nenhum

dos dois estados.

Outras caracterı́sticas deste circuito são:

1. A saı́da é praticamente igual a VDD ou VSS e independe dos tamanhos

dos transistores.

2. A resistência de entrada é praticamente infinita, já que o gate de um

transistor MOS é simplesmente um capacitor.

3. A resistência de saı́da é a de um transistor MOS com VGS = |V DD − V SS|

e VDS = 0 e pode ser feita bastante pequena.

VDD

VDD

ent

sai

sai

ent

VSS

VSS

a

b

Figura 7: Porta Lógica inversora com transistor a)nMOS e b)pMOS.

6

2.3

Lógica MOS Complementar

Analisando novamente o inversor, vemos que ele é composto de duas partes: o

transistor nMOS e o transistor pMOS (obviamente!). O transistor nMOS age

como uma chave que liga a saı́da do circuito a VSS para indicar nı́vel lógico

zero e fica aberto quando a saı́da for de nı́vel lógico 1. O transistor pMOS tem

a função contrária a esta. Podemos dizer então que este circuito é composto de

uma rede pull-down feita de transistores nMOS (PDN — pull-down network ) e

uma rede pull-up de transistores pMOS (PUN — pull-up network ).

Para chegarmos a circuitos mais complexos basta então ampliar o conceito

de rede pull-down e rede pull-up:

Num circuito CMOS que realiza uma função lógica F de n variáveis,

a rede pull-up é uma chave que conecta a saı́da a VDD sempre que

F = 1 e fica aberta quando F = 0; e a rede pull-down é uma chave

que conecta a saı́da a VSS sempre que F = 0 e fica aberta quando

F = 1.

Ou seja, o circuito nMOS e o pMOS agem como chaves complementares.

Quando a saı́da deve ser 0 a rede de cima abre e a de baixo fecha; quando a

saı́da deve ser 1, rede de baixo fecha e a de cima abre. Desta forma consegue-se

manter todas as caracterı́sticas desejáveis do circuito inversor CMOS.

Como exemplo deste tipo de circuito, a figura 9 apresenta uma porta NAND

de 2 entradas. A rede pull-down, composta por transistores nMOS, deve ligar

para o terra quando A e B forem 1. Pensando nos transistores como chaves, a

ligação série implementa uma chave que realiza esta função. Ou seja, a ligação

série é o equivalente de uma operação AND.

A rede pull-up, por sua vez, é composta de transistores pMOS que ligam

com zero. Analisando deste ponto de vista, esta rede deve ligar quando A ou B

forem 0, o que é realizado por uma ligação em paralelo dos transistores.

Resumindo: enquanto a rede pull-down é em série para ligar quando A e B

forem 1, a pull-up é em paralelo, para realizar a operação OR. Ou seja uma rede

é o dual da outra. Isto não é verdadeiro apenas para esta porta NAND, mas

para qualquer porta CMOS (é possı́vel chegar nesta conclusão por deMorgan).

Com isto não é preciso construir as duas redes, basta chegar na topologia de

uma delas e a outra é o dual da primeira (onde é série fica paralelo e onde é

paralelo fica série).

Uma restrição deste tipo de circuito é que os transistores nMOS agem adequadamente como chaves apenas quando ligados à VSS (e ligam com VDD

no gate) enquanto que os pMOS só funcionam como chaves quando ligados a

VDD

M2

ent

sai

M1

VSS

Figura 8: Porta Lógica inversora MOS complementar.

7

VDD (e ligam com VSS no gate). Ista faz com que só seja possı́vel uma rede

pull-down que liga com 1 e uma rede pull-up que liga com zero, então só é

possı́vel implementar funções do tipo inversoras, ou seja, funções cujas entradas

não aparecem barradas, mas que a saı́da seja barrada (tais como NAND, NOR,

(A + B)(C + D),etc).

Como exemplo, considere-se a função F (A, B, C, D) = A + B (C + D). Um

transistor nMOS e outro pMOS são utilizados para cada uma das variáveis.

Pode-se construir a PDN e obter a PUN pelo dual da primeira. Da maneira

como o circuito aparece, a PDN é obtido facilmente, lembrando que transistores

em série realizam a função E e em paralelo a função OU. Então a PDN fica A

em paralelo com (B em série com (C e D em paralelo)) (figura 10.a). A PUN

pode ser obtida aplicando deMorgan até se obter F (A, B, C, D) = A B + CD

e aplicando o mesmo método usado para se chegar na PDN ou então apenas

fazendo o dual da PDN. O circuito final pode ser visto na figura 10.b.

2.4

Análise dinâmica

Considere-se que este inversor CMOS esteja conectado a outras portas CMOS

de configuração semelhante. É possı́vel então simplificar dizendo que a saı́da de

nosso inversor é ligada a um capacitor CL equivalente (figura 11).

Com este capacitor, ao se variar a saı́da de 0 para 1 e vice-versa o capacitor

é carregado com VDD pelo pMOS e descarregado pelo nMOS, o que causa um

consumo de corrente no chaveamento do circuito.

VDD

A

sai

B

VSS

Figura 9: Porta Lógica NAND CMOS.

8

VDD

D

B

C

B

A

A

F

D

C

B

VSS

A

D

C

VSS

a

b

Figura 10: a)Rede pull-down do circuito que realiza a função F (A, B, C, D) =

A + B (C + D) e b)Circuito completo da porta lógica.

VDD

M2

ent

sai

M1

VSS

Figura 11: Inversor CMOS com capacitor de carga na saı́da.

9