ESTUDO DA TENSÃO EARLY EM FUNÇÃO DA LARGURA

DE CANAL DE TRANSISTORES DE PORTA EM ANEL

CIRCULAR

Leonardo Sandre Sapage1 e Salvador Pinillos Gimenez2

1,2

Centro Universitário da FEI, Brasil

[email protected] e [email protected]

O desempenho de circuitos integrados analógicos é

fortemente afetado pela forma geométrica do dispositivo

fabricado [1]. Um alto valor de ganho de malha aberta

(AV0) é obtido utilizando dispositivos que possuem

elevados valores de tensão Early (|VEA|) [1]. O uso de

estratégias de melhorar |VEA| aumentam as capacitâncias

parasitas e a área gasta de silício. Outra maneira de

melhorar |VEA| é através da utilização de novos

dispositivos, como por exemplo o transistor de canal

gradual (GC SOI nMOSFET). Alternativamente, para

uma dada tecnologia, pode-se estudar a influência da

forma geométrica do dispositivo em relação à |VEA|. A

referência [2] mostrou que o transistor de porta circular

(CGT) SOI MOSFET operando com dreno externo

apresenta um melhor |VEA| que ele operando com dreno

interno e que o transistor convencional (RGT),

considerando uma mesma razão de aspecto (W/L), onde

W é a largura do canal. O objetivo desse trabalho é

estudar o comportamento de |VEA| entre o CGT

operando com dreno interno e externo em função de W,

por meio de simulação tridimensional.

2. Edição dos Dispositivos

Para realizar o estudo de |VEA| em função de W,

foram definidos três (3) CGTs com três (3) diferentes

valores de W (12,6 µm, 25 µm e 100 µm), considerando

o comprimento de canal (L) fixo em 1 µm. Utilizandose a equação (1) (razão de aspecto do RGT e CGT),

determinaram-se os valores dos raios internos (R1) e

externos (R2) que definem as dimensões das portas em

formato de anel de cada um dos CGTs.

2π

2π

W

(1)

=

=

L Re tan gular ln(R2 / R1) Circular ln(1 + L / R1) Circular

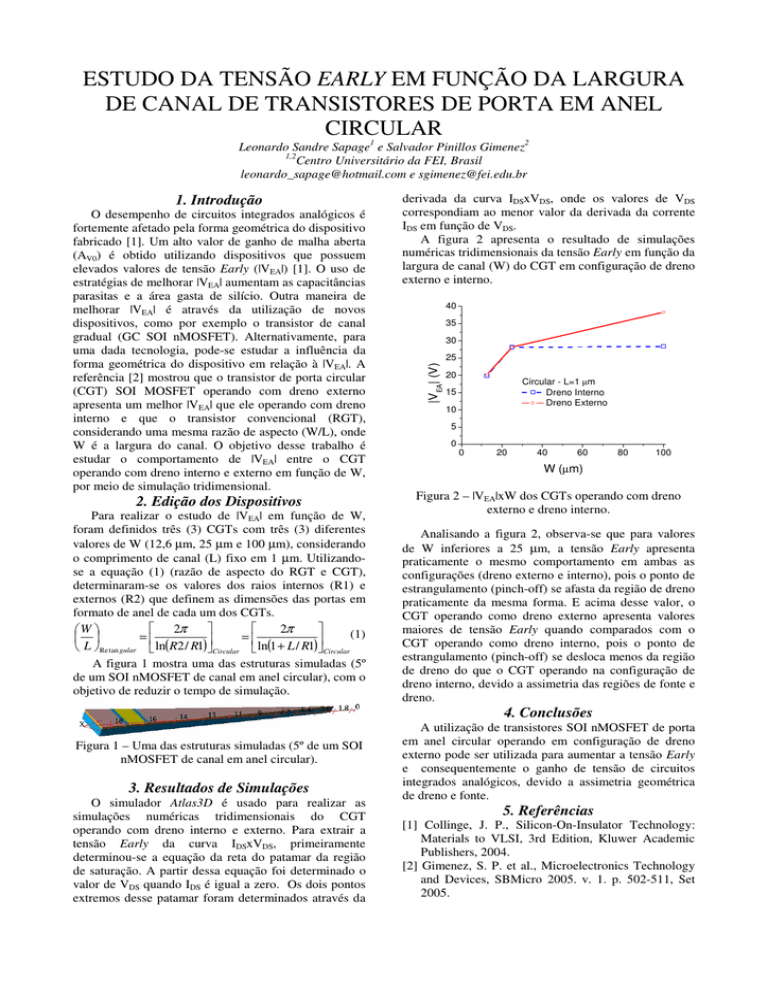

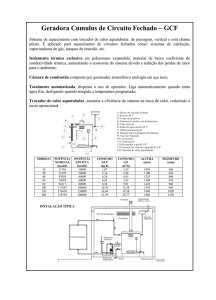

A figura 1 mostra uma das estruturas simuladas (5º

de um SOI nMOSFET de canal em anel circular), com o

objetivo de reduzir o tempo de simulação.

derivada da curva IDSxVDS, onde os valores de VDS

correspondiam ao menor valor da derivada da corrente

IDS em função de VDS.

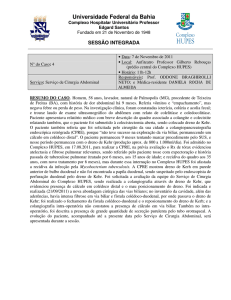

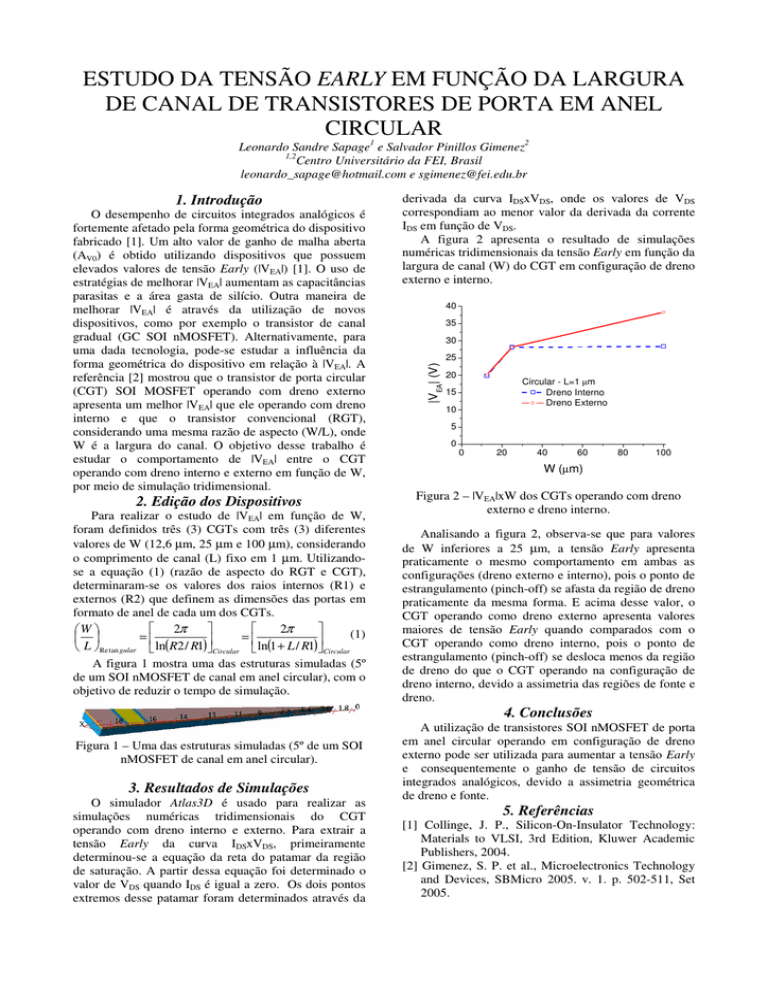

A figura 2 apresenta o resultado de simulações

numéricas tridimensionais da tensão Early em função da

largura de canal (W) do CGT em configuração de dreno

externo e interno.

40

35

30

25

|VEA| (V)

1. Introdução

20

Circular - L=1 µm

Dreno Interno

Dreno Externo

15

10

5

0

0

20

40

60

80

100

W (µm)

Figura 2 – |VEA|xW dos CGTs operando com dreno

externo e dreno interno.

Analisando a figura 2, observa-se que para valores

de W inferiores a 25 µm, a tensão Early apresenta

praticamente o mesmo comportamento em ambas as

configurações (dreno externo e interno), pois o ponto de

estrangulamento (pinch-off) se afasta da região de dreno

praticamente da mesma forma. E acima desse valor, o

CGT operando como dreno externo apresenta valores

maiores de tensão Early quando comparados com o

CGT operando como dreno interno, pois o ponto de

estrangulamento (pinch-off) se desloca menos da região

de dreno do que o CGT operando na configuração de

dreno interno, devido a assimetria das regiões de fonte e

dreno.

4. Conclusões

Figura 1 – Uma das estruturas simuladas (5º de um SOI

nMOSFET de canal em anel circular).

3. Resultados de Simulações

O simulador Atlas3D é usado para realizar as

simulações numéricas tridimensionais do CGT

operando com dreno interno e externo. Para extrair a

tensão Early da curva IDSxVDS, primeiramente

determinou-se a equação da reta do patamar da região

de saturação. A partir dessa equação foi determinado o

valor de VDS quando IDS é igual a zero. Os dois pontos

extremos desse patamar foram determinados através da

A utilização de transistores SOI nMOSFET de porta

em anel circular operando em configuração de dreno

externo pode ser utilizada para aumentar a tensão Early

e consequentemente o ganho de tensão de circuitos

integrados analógicos, devido a assimetria geométrica

de dreno e fonte.

5. Referências

[1] Collinge, J. P., Silicon-On-Insulator Technology:

Materials to VLSI, 3rd Edition, Kluwer Academic

Publishers, 2004.

[2] Gimenez, S. P. et al., Microelectronics Technology

and Devices, SBMicro 2005. v. 1. p. 502-511, Set

2005.