Universidade Federal do Piauí

Centro de Tecnologia

Curso de Engenharia Elétrica

DISPOSITIVOS

ELETRÔNICOS

Transistores de Efeito de Campo

- Parte I - JFETs

Prof. Marcos Zurita

[email protected]

www.ufpi.br/zurita

Teresina - 2012

Sumário

●

●

●

●

●

●

●

1. Introdução

2. O Transistor JFET

3. Características do JFET

4. Regiões de Operação

5. Curva de Transferência

6. Polarização do JFET

Bibliografia

Dispositivos Eletrônicos – Prof. Marcos Zurita

2

1. Introdução

Dispositivos Eletrônicos – Prof. Marcos Zurita

3

Introdução

Transistores de Efeito de Campo (FET)

●

●

●

●

FET – Field Effect Transistor

São dispositivos cuja corrente entre dois pinos

pode ser controlada através da tensão em um

terceiro pino.

Os mais populares membros

I

da família de transistores FET

são os MOSFETs.

Terminal de

Outro tipo de FET é o JFET,

controle

FET

que, por sua simplicidade,

será abordado inicialmente.

V

Dispositivos Eletrônicos – Prof. Marcos Zurita

4

Introdução

Transistores FET em diferentes encapsulamentos

Dispositivos Eletrônicos – Prof. Marcos Zurita

5

2. O Transistor JFET

Dispositivos Eletrônicos – Prof. Marcos Zurita

6

O Transistor JFET

●

●

●

JFET: Transistor de Efeito de Campo de Junção (do

inglês, Junction Field Effect Transistor);

Formado pela associação entre SCs tipo p e n, sendo

um deles fortemente dopado.

Dreno / Drain

(D)

Basicamente composto por:

●

●

●

um canal SC responsável pela

condução de corrente entre dois

terminais (Fonte e Dreno);

um mecanismo de controle do

canal, operado por um terceiro

terminal (Porta).

Região de

depleção

Porta / Gate

(G)

Há dois tipos de JFETs:

●

JFET canal n;

p+

n

p+

Canal n

Fonte / Source

(S)

• JFET canal p.

Dispositivos Eletrônicos – Prof. Marcos Zurita

7

O Transistor JFET

●

Estrutura básica do JFET canal n e canal p

Dreno / Drain

(D)

Dreno / Drain

(D)

Região de

depleção

Porta / Gate

(G)

p+

n

Região de

depleção

Porta / Gate

(G)

p+

n+

Canal n

Fonte / Source

(S)

●

●

p

n+

Canal p

Fonte / Source

(S)

p+ e n+: regiões p e n fortemente dopadas (≥1018/cm3).

Como o gate é muito mais fortemente dopado que o

canal, a região de depleção estende-se quase que

totalmente no lado do canal (vide Eq. 2.12).

8

Dispositivos Eletrônicos – Prof. Marcos Zurita

O Transistor JFET

●

Embora o dispositivo seja simétrico é conveniente haver

uma distinção entre os terminais conectados ao canal:

●

●

●

Terminal Fonte (S – Source): de onde partem os elétrons

num JFET canal n (“fonte” de elétrons).

Conectado ao

Dreno (D)

Terminal Dreno (D – Drain): destino dos

elétrons num JFET canal n. Comumente

conectado ao dissipador térmico em

dispositivos que o possuem;

Simbologia:

S

G

S

S

G

G

D

S

D

JFET canal n

G

D

D

JFET canal p

Dispositivos Eletrônicos – Prof. Marcos Zurita

9

3. Características do JFET

Dispositivos Eletrônicos – Prof. Marcos Zurita

10

Características do JFET

●

Admita um JFET canal n, polarizado por uma fonte de

tensão vDS (entre D e S) e outra vGS (entre G e S).

Análise para vGS = 0V e vDS ≥ 0V

● Como v

GS = 0V, a junção

entre o gate e o canal fica

reversamente polarizada

para qualquer valor positivo

de vDS.

● Ao aplicar v

DS > 0V, uma

corrente de elétrons fluirá

do terminal fonte para o

dreno, através do canal,

limitada por sua resistência.

D

Região de

depleção

VDS

n

p+

p+

G

VGS

S

Dispositivos Eletrônicos – Prof. Marcos Zurita

11

Características do JFET

●

●

Se a tensão vDS for suficientemente pequena, a região

de depleção pode ser desprezada e a largura do canal

assumida como a distância entre as regiões de gate (2a).

Nessas condições, a resistência do canal pode ser

obtida a partir da Eq. 1.23 como sendo:

rO =

●

L

1 L

1

=

=

A A

q n N D

L

2 a⋅W

2a

Logo, a corrente através do

canal (iDS) será dada por:

W

ou seja:

I DS =v DS / r 0

I DS =2 a

W

q n N D v DS

L

L

(Eq. 6.1)

Dispositivos Eletrônicos – Prof. Marcos Zurita

x

z

y

12

Características do JFET

●

●

●

Enquanto vDS permanecer suficientemente baixo, a

corrente através do canal aumentará linearmente,

conforme previsto pela lei de Ohm através da Eq. 6.1.

Entretanto, à medida que vDS se aproxima de um dado

valor (VP), o tamanho da região de depleção torna-se

cada vez mais significativa.

A largura da região de depleção dependerá da ddp entre

o gate (0V, neste caso) e o canal, que, conforme a teoria

de semicondutores (Eq. 2.45), é dada por:

onde,

2 N A N D

W deplecao=

V 0−V

q N A ND

juncao

V juncao =vGS −V canal x , y

Dispositivos Eletrônicos – Prof. Marcos Zurita

(Eq. 6.2)

(Eq. 6.3)

13

Características do JFET

●

●

●

Entretanto, essa ddp (Eq. 6.3) não é constante ao longo

do canal, visto que vDS está distribuída entre o terminal

fonte e o dreno.

Isto provocará uma distorção da

região de depleção, cuja largura

crescerá ao longo do canal comforme a distância até o dreno

(onde a ddp é maior) diminui.

Naturalmente, esse aumento

da região de depleção reduzirá

a área do canal (2aW), aumentando a sua resistência.

Dispositivos Eletrônicos – Prof. Marcos Zurita

14

Características do JFET

●

●

●

A partir vDS = VP a região de depleção aumenta a ponto

de “estrangular” o canal e corrente através dele

praticamente não cresce mais com o aumento de vDS.

Corrente Máxima de Dreno (IDSS) - ou corrente vDS de

saturação: é a corrente iDS do JFET obtida quando vGS =

0V e vDS = VP.

A corrente iDS de saturação (IDSS) de um JFET pode ser

calculada a partir da Eq. 6.1, fazendo vDS = VP, ou seja:

W

I DSS =2 a

q N D n V P

L

Dispositivos Eletrônicos – Prof. Marcos Zurita

(Eq. 6.4)

15

Características do JFET

●

●

●

●

●

Tensão de Pinch-off (VP) – ou tensão de estrangulamento: mínima tesão entre o dreno e o fonte capaz de

provocar o estrangulamento do canal de um JFET.

Para vDS > VP a corrente através do canal virtualmente

não cresce mais, pois fluxo de portadores atinge seu

valor máximo (satura) em vDS = VP.

Para valores de vDS suficientemente elevados acima de

VP, ocorre um aumento abrupto na corrente iDS.

Tensão de Ruptura (VDSmax ou BVDSS) – tensão vDS a

partir da qual ocorre a ruptura do canal do JFET.

Na ruptura, iDS é limitada unicamente pelo circuito

externo ao JFET, podendo ocasionar sua queima.

Dispositivos Eletrônicos – Prof. Marcos Zurita

16

Características do JFET

Curva iD-vDS do JFET para vGS = 0

pinch-off

Ruptura

Nível de saturação

IDSS

Aumento da resistência devido

ao estreitamento do canal

Resistência do canal n

0

VP

Dispositivos Eletrônicos – Prof. Marcos Zurita

VDSmax

17

Características do JFET

Análise para vGS < 0V e vDS > 0V

● Ao se aplicar uma tensão negativa em v

GS, a região de

depleção crescerá de maneira semelhante a análise

D

anterior (com vGS = 0V), porém,

VGS = -4V

para valores menores de vDS.

VGS = -2V

VGS = -1V

● De fato, mesmo se v

fosse

DS

VGS = 0V

fixado em um valor positivo,

G p+

p+ G

seria possível modular a

largura do canal unicamente

VDS = 10V

através de vGS.

n

● Dessa forma, quanto mais

S

negativo for vGS, mais estreito será o canal e menor será

sua capacidade de condução de corrente.

18

Dispositivos Eletrônicos – Prof. Marcos Zurita

Características do JFET

●

●

●

●

Consequentemente, a saturação será atingida para

valores tanto menores de vDS quanto mais negativa for a

tensão de gate.

Se vGS tornar-se negativo o bastante o canal será

completamente estrangulado, levando o valor da

corrente de saturação a zero para qualquer valor de vDS.

Tensão de Corte (VGS(desligado) ou VGS(off)): é o valor de

vGS para o qual o canal torna-se completamente

estrangulado. Corresponde, em módulo, a VP.

Na condição de corte (|vGS| = VP), o JFET comporta-se

de forma semelhante a uma chave aberta (ou

desligada).

Dispositivos Eletrônicos – Prof. Marcos Zurita

19

Características do JFET

Curvas ID-VDS do JFET para VGS ≥ 0

VGS = 0 V

IDSS

-VGS1

-VGS2

-VGS3

-VGS4

-VGS5

0

VP

-VGS = VP

Dispositivos Eletrônicos – Prof. Marcos Zurita

20

4. Regiões de Operação

Dispositivos Eletrônicos – Prof. Marcos Zurita

21

Regiões de Operação

●

●

Conforme os valores de vDS e vGS, é possível estabelecer em que região de operação o JFET se encontra:

I - Região Ôhmica:

●

●

II - Região de Saturação:

●

●

-VP ≤ vGS ≤ 0 e vDS ≥ VP - vGS

I

II

III - Região de Corte:

●

●

Linha de estrangulamento

(Lugar geométrico dos

valores de pinch-off)

-VP < vGS ≤ 0 e vDS ≤ VP - vGS

VGS = 0 V

-VGS1

vGS ≤ -VP

-VGS2

IV - Região de Ruptura:

●

vDS > VDSmax

IV

-VGS3

-VGS4

-VGS5

Dispositivos Eletrônicos – Prof. Marcos Zurita

III

22

Regiões de Operação

Características vDS-iDS de um JFET canal n

●

Região Ôhmica (-VP < vGS ≤ 0 e vDS ≤ VP - vGS)

●

●

Também conhecida como “Região de Triodo”.

A corrente de dreno nesta região pode ser expressa em

função da corrente de saturação (IDSS) como sendo:

i D= I DSS

●

[ ]

v GS

2 1−

VP

v DS

v DS

−

−V P

VP

2

(Eq. 6.5)

Uma aproximação alternativa e mais simplificada pode ser

definida com base na Eq. 6.1, como:

i D= I DS

v GS

1−

VP

Dispositivos Eletrônicos – Prof. Marcos Zurita

(Eq. 6.6)

23

Regiões de Operação

●

●

Na região de triodo o JFET comporta-se como um resistor

controlado por tensão, cuja resistência é tanto maior

quanto maior for vGS.

Uma aproximação da resistência entre os terminais de

dreno e fonte na região de triodo é dada por:

r d=

●

ro

(Eq. 6.7)

2

1−v GS /V P

Onde ro é a resistência do canal para vGS = 0, que,

conforme visto anteriormente pode ser expresso por:

[

W

r o= 2 a

q n N D

L

−1

]

Dispositivos Eletrônicos – Prof. Marcos Zurita

(Eq. 6.8)

24

Regiões de Operação

●

Região de Saturação (-VP ≤ vGS ≤ 0 e vDS ≥ VP - vGS)

●

●

Também conhecida como “Região de Amplificação”.

A corrente de dreno nesta região pode ser expressa em

função da corrente de saturação (IDSS) através da equação

de Shockley:

2

i D= I DSS

●

●

vGS

1−

1 v DS

VP

(Eq. 6.9)

Onde λ é o parâmetro de inclinação da curva da corrente

de dreno na região de saturação, sendo definida como o

inverso da Tensão Early (VA).

Uma simplificação da Eq. 6.9 pode ser obtida desprezando-se o termo (1+λvDS), o que corresponde a assumir que

o crescimento de ID após a saturação é desprezível.

Dispositivos Eletrônicos – Prof. Marcos Zurita

25

Regiões de Operação

●

Tensão de Early (VA): graficamente, corresponde ao

ponto de interseção com o eixo VDS das projeções das

curvas das correntes de dreno na região de saturação.

-VA = -1/λ

Dispositivos Eletrônicos – Prof. Marcos Zurita

26

Polarização do JFET

●

Alternativamente, a resistência ro definida

anteriormente pode ser calculada na região de

saturação através da tensão de Early:

∣V A∣

r o=

iD

●

(Eq. 6.10)

É possível deduzir, a partir da simplificação da Eq.

6.9, a equação da tensão de gate em função da

corrente de dreno:

v GS =V P

iD

1−

I DSS

Dispositivos Eletrônicos – Prof. Marcos Zurita

(Eq. 6.11)

27

Regiões de Operação

●

Região de Corte (vGS ≤ -VP)

●

Nesta região o JFET comporta-se como uma chave

aberta para qualquer valor de vDS, logo:

i D=0

●

(Eq. 6.12)

Região de Ruptura (vDS > VDSmax):

●

●

Esta não é propriamente uma região de operação

desejável, pois pode causar a queima do componente.

Nesta região a corrente de dreno é limitada unicamente

pelo circuito externo ao transistor, logo não é possível

estabelecer uma equação geral para ela.

Dispositivos Eletrônicos – Prof. Marcos Zurita

28

5. Curva de Transferência

Dispositivos Eletrônicos – Prof. Marcos Zurita

29

Curva de Transferência

●

●

Curva de transferência: relaciona diretamente a corrente de dreno (iDS) à tensão de controle do JFET (vGS).

Pode ser obtida a partir da eq. de Shockley (Eq. 6.9) ou

das curvas iD-vDS.

Dispositivos Eletrônicos – Prof. Marcos Zurita

30

Curva de Transferência

●

A curva de transferência evidencia dois importantes

parâmetros do JFET:

IDSS: interseção da curva com o eixo vertical (ID).

● V : interseção da curva com o eixo horizontal (v

P

GS).

Além disso, ela também permite a determinação do ponto de

operação do JFET em um circuito, pelo do método gráfico.

●

●

Esboço da Curva de Transferência

●

Pode ser feito com o auxílio da tabela abaixo obtida a partir

da Eq. 6.9:

ID

vGS

IDSS

0

IDSS/2

0,3 VP

IDSS/4

0,5 VP

0

VP

Dispositivos Eletrônicos – Prof. Marcos Zurita

31

Curva de Transferência

Ex: Esboce a curva de transferência para JFET de canal

n, com IDSS = 12mA e VP = -6V.

Sol:

●

●

●

●

P/ ID = IDSS → vGS = 0

ID = 12mA → vGS = 0V

P/ ID = IDSS/2 → vGS = 0,3VP

ID = 6mA → vGS = -1,8V

P/ ID = IDSS/4 → vGS = 0,5VP

ID = 3mA → vGS = -3V

P/ ID = 0 → vGS = VP

ID = 0mA → vGS = -6V

Dispositivos Eletrônicos – Prof. Marcos Zurita

32

Curva de Transferência

Ex: Esboce a curva de transferência para JFET de canal

p, com IDSS = 4mA e VP = 3V.

Sol:

●

●

●

●

P/ ID = IDSS → vGS = 0

ID = 4mA → vGS = 0V

P/ ID = IDSS/2 → vGS = 0,3VP

ID = 2mA → vGS = 0,9V

P/ ID = IDSS/4 → vGS = 0,5VP

ID = 1mA → vGS = 1,5V

P/ ID = 0 → vGS = VP

ID = 0mA → vGS = 3V

Dispositivos Eletrônicos – Prof. Marcos Zurita

33

6. Polarização do JFET

Dispositivos Eletrônicos – Prof. Marcos Zurita

34

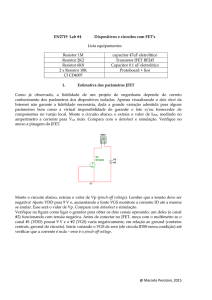

Polarização do JFET

●

●

●

O projeto e a análise de circuitos envolvendo JFETs

parte da determinação dos parâmetros de operação do

componente.

Tais parâmetros dependem do circuito a sua volta e da

polarização por ele imposta.

Podemos definir 5 tipos básicos de polarização do JFET:

●

●

●

●

●

●

Polarização Fixa;

Autopolarização;

Polarização por Divisor de Tensão;

Polarização por Fonte de Corrente;

Polarização por Duas Fontes.

Os três primeiros tipos (mais elementares) serão

abordados neste capítulo.

Dispositivos Eletrônicos – Prof. Marcos Zurita

35

Polarização do JFET

Algorítimo de Determinação da Polarização

●

●

De maneira geral, a solução de qualquer uma das

configurações de polarização parte da determinação da

equação da tensão de controle do JFET, isto é, vGS.

Conhecida a equação de vGS, o passo seguinte é a

escolha de um dos dois métodos básicos de resolução:

●

●

Método matemático: consiste em aplicar a equação de vGS

na equação de Shockley e soluciona-la. Para algumas

configurações pode não haver resolução analítica.

Método gráfico: consiste em traçar a curva característica

do circuito de polarização diretamente sobre a curva de

transferência do JFET. O ponto de operação é então

determinado pela interseção entre as curvas.

Dispositivos Eletrônicos – Prof. Marcos Zurita

36

Polarização do JFET

Polarização Fixa

●

●

●

Caracteriza-se pela presença de uma fonte DC fixa

dedicada a polarização do gate.

É tipo mais simples de

polarização do JFET.

Pode ser solucionada

tanto pelo método matemático quanto pelo

método gráfico (curva

de transferência).

Dispositivos Eletrônicos – Prof. Marcos Zurita

37

36

Polarização do JFET

●

●

Uma vez que os capacitores são 'circuitos abertos' em

análise DC, podemos eliminá-los do circuito para determinar a polarização.

A determinação da eq.

de vGS, pode ser feita

através da análise de

malha:

−V G G RG i G −v GS =0

mas iG = 0, logo:

−V G G −v GS =0

ou seja:

v GS =−V G G

(Eq. 6.13)

Dispositivos Eletrônicos – Prof. Marcos Zurita

38

Polarização do JFET

●

A Eq. 6.13 sugere que, para a análise da polarização, o

circuito dado equivale a um onde a fonte VGG é diretamente conectada ao gate.

● A solução matemática pode

ser encontrada simplesmente

aplicando a Eq. 6.13 à Eq. de

Shockley, que, desprezando

λ torna-se:

i D= I DSS

vG G

1

VP

Dispositivos Eletrônicos – Prof. Marcos Zurita

2

(Eq. 6.14)

39

Polarização do JFET

●

●

●

●

A solução gráfica parte da determinação da curva de

transferência do JFET em questão, que pode ser

esboçada através do método exposto na página 31.

Com a curva de transferência

traçada basta traçar sobre ela

Reta

a curva de vGS (Eq. 6.13), que,

VGS = -VGG

neste caso é simplesmente

uma reta vertical em vGS = -VGG.

Ponto Q

A interseção entre as curvas

iDQ

determina o ponto de operação

do JFET, também chamado de

ponto quiescente (Q).

A partir do ponto Q encontra

-VGG

-se o valor de iDQ.

Dispositivos Eletrônicos – Prof. Marcos Zurita

40

Polarização do JFET

●

Ex.: Determine iDQ, vGSQ e vD para o circuito abaixo.

Dispositivos Eletrônicos – Prof. Marcos Zurita

41

Polarização do JFET

●

Sol.:

v GSQ=−V G G =−2V

Ponto Q

Dispositivos Eletrônicos – Prof. Marcos Zurita

42

Polarização do JFET

Autopolarização

●

●

●

Elimina a necessidade de uma fonte dedicada à polarização do gate.

Polarização através da tensão

sobre o resistor RS.

vGS torna-se uma função da

corrente de saída iD, e da

resistência RS.

Dispositivos Eletrônicos – Prof. Marcos Zurita

43

42

Polarização do JFET

●

●

Assim como na análise anterior, podemos eliminar os

capacitores do circuito para determinar a polarização.

A determinação da eq.

de vGS, pode ser feita

através da análise de

malha:

RG i G −vGS −R S i S =0

mas iG=0 e iS =iD, logo:

v GS =−RS i D

(Eq. 6.15)

Dispositivos Eletrônicos – Prof. Marcos Zurita

44

Polarização do JFET

●

Conforme a Eq. 6.15, a análise da polarização nesta

configuração pode ser feita assumindo um circuito

equivalente cujo gate é diretamente ligado ao terra.

● A solução matemática pode ser

encontrada substituindo a Eq. 6.15 na

equação de Shockley, resultando em:

i D= I DSS

●

RS i D

1

VP

2

(Eq. 6.16)

A manipulação algébrica desta equação resulta em:

2

i D K 1 i D K 2=0

Dispositivos Eletrônicos – Prof. Marcos Zurita

(Eq. 6.17)

45

Polarização do JFET

onde os termos K1 e K2 são dados por:

K 1 =V P

2 I DSS RS −V P

I DSS R

2

S

2

VP

K 2=

RS

●

●

(Eq. 6.18)

(Eq. 6.19)

Naturalmente, a resolução da Eq. 4.17 resulta em duas

raízes possíveis para iD. A solução válida (iDQ) é sempre

a raiz de menor magnitude.

Uma vez determinada a corrente de dreno quiescente

(iDQ) basta inseri-la na Eq. 6.15 para determinar a tensão

de gate quiescente (vGSQ).

Dispositivos Eletrônicos – Prof. Marcos Zurita

46

Polarização do JFET

●

●

●

A resolução pelo método gráfico, consiste simplesmente

em traçar a curva de vGS sobre a curva de transferência

do JFET, previamente esboçada.

A eq. de vGS neste caso é uma

reta (Eq. 6.15), cuja inclinação é dada por RS.

Reta

Para traça-la basta a VGS = -RSiD

determinação de 2

iDQ

pontos:

Ponto Q

● i

D = 0 → vGS = 0

● i

D = iarbitrário

→ vGS = RS.iarbitrário

vGSQ

Dispositivos Eletrônicos – Prof. Marcos Zurita

47

Polarização do JFET

●

Ex.: Determine iDQ, vGSQ e vD para o circuito abaixo.

Dispositivos Eletrônicos – Prof. Marcos Zurita

48

Polarização do JFET

●

Sol.: Arbitrando iD = 8 mA e aplicando-se o valor de RS =

1 kΩ na Eq. 6.15 encontra-se vGS = -8 V e a reta de

autopolarização pode então ser traçada:

Reta vGS = 1×103iD

Dispositivos Eletrônicos – Prof. Marcos Zurita

49

Polarização do JFET

●

A determinação do ponto quiescente pode então ser

feita pela interseção da reta de autopolarização com a

reta de carga do JFET:

v GSQ=−2,6V

i DQ=2,6 mA

v D=V DD −R D i DQ

v D=20V−3,3×103⋅2,6×10−3

v D=11,42 V

Dispositivos Eletrônicos – Prof. Marcos Zurita

50

Polarização do JFET

Polarização por Divisor de Tensão

●

●

Caracteriza-se por fixar a polarização do gate sem a

necessidade de uma fonte dedicada e de forma mais

independente dos parâmetros de saída do JFET.

Através dessa configuração

é possível ajustar o ponto

de operação do JFET

sem variar a resistência

RS, como ocorre na

autopolarização.

Dispositivos Eletrônicos – Prof. Marcos Zurita

51

Polarização do JFET

●

Eliminando os capacitores para a análise de polarização,

pode-se determinar vG diretamente através do divisor de

tensão formado por R1 e R2, ou seja:

v G =V DD

●

R2

R1 R2

(Eq. 6.20)

Por outro lado, vGS é

dado por:

v GS =vG −v S

logo:

v GS =vG −R S i D

(Eq. 6.21)

Dispositivos Eletrônicos – Prof. Marcos Zurita

52

Polarização do JFET

●

●

O procedimento para determinar o ponto de operação

deste tipo de circuito de polarização é muito semelhante

ao da autopolarização, com a diferença que neste caso

a reta de polarização (Eq. 6.21) não parte mais da

origem dos eixos e sim do ponto iD = 0, vGS = vG.

Outro ponto notável da

reta descrita pela Eq.

6.21 pode ser obtido

fazendo-se vGS = 0, o

que resulta em

iD = vG /RS.

Dispositivos Eletrônicos – Prof. Marcos Zurita

53

Polarização do JFET

●

A corrente de dreno pode ser reduzida ou aumentada

conforme se aumenta ou diminui os valores de RS.

Aumentando os

valores de RS

Dispositivos Eletrônicos – Prof. Marcos Zurita

54

Polarização do JFET

●

Ex.: Determine ID, VGSQ e VD para o circuito abaixo.

Dispositivos Eletrônicos – Prof. Marcos Zurita

55

Polarização do JFET

●

Sol.: Resolução pelo método gráfico.

Dispositivos Eletrônicos – Prof. Marcos Zurita

56

Polarização do JFET

Tipo de Polarização

Configuração

Principais Equações

Solução Gráfica

Fixa

v GS =−V G G

Autopolarização

v GS =R S i D

Divisor de Tensão

v GS =vG −R S i D

v G =V DD

R2

R1 R2

Dispositivos Eletrônicos – Prof. Marcos Zurita

57

Bibliografia

●

●

●

●

●

Adel S. Sedra, Kenneth C. Smith,

“Microeletrônica”, 5ª Edição, Pearson, 2007.

Behzad Razavi, “Fundamentos de

Microeletrônica”, 1º Edição, LTC, 2010.

Robert L. Boylestad, Louis Nashelsky,

“Dispositivos Eletrônicos e Teoria de

Circuitos”, 8º Edição, Prentice Hall, 2004.

David Comer, Donald Comer, “Fundamentos de

Projeto de Circuitos Eletrônicos”, LTC, 2005.

Jimmie J. Cathey, “Dispositivos e Circuitos

Eletrônicos”, 2ª Ed., Coleção Schaum,

Bookman, 2003.

Dispositivos Eletrônicos – Prof. Marcos Zurita

58