Universidade de Coimbra

Departamento de Engenharia Electrotécnica

ELECTRÓNICA II 2003/2004

Trabalho Prático Nº 2

FET’s: Características, Polarização e Amplificadores

1.

OBJECTIVOS

Determinar os parâmetros que definem a característica do JFET

Construir um amplificador em source comum e polarizá-lo

Calcular o seu ganho e verificá-lo experimentalmente

2.

INTRODUÇÃO

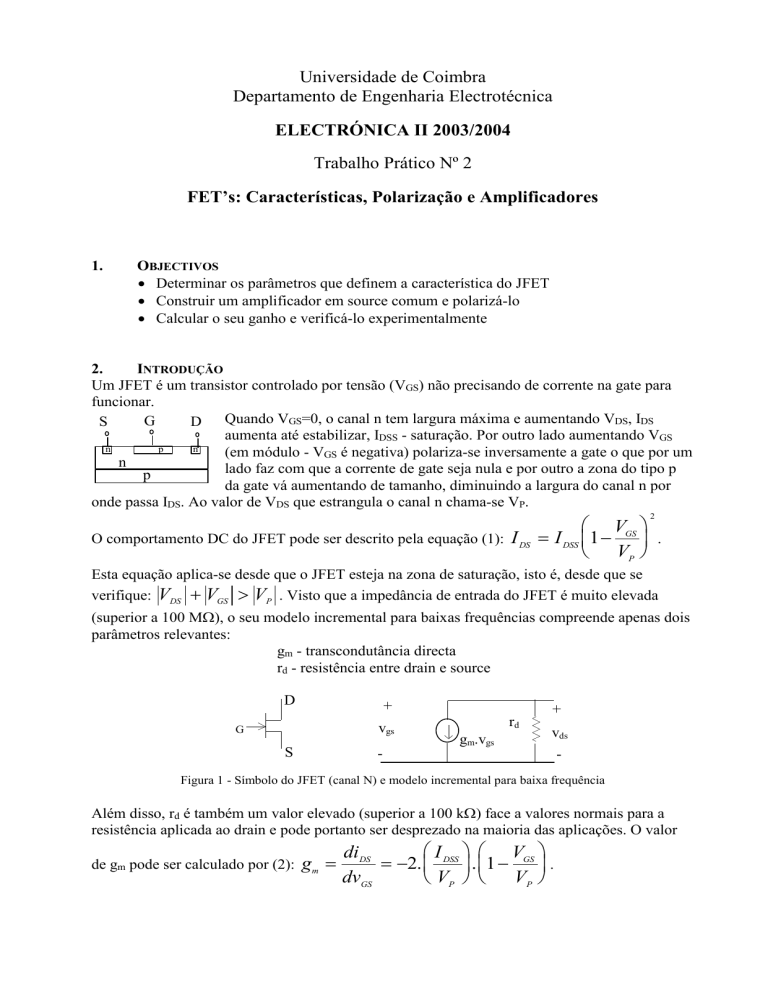

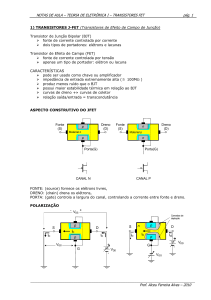

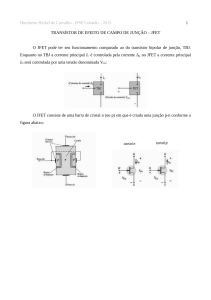

Um JFET é um transistor controlado por tensão (VGS) não precisando de corrente na gate para

funcionar.

G

S

D Quando VGS=0, o canal n tem largura máxima e aumentando VDS, IDS

aumenta até estabilizar, IDSS - saturação. Por outro lado aumentando VGS

n

n

p

(em módulo - VGS é negativa) polariza-se inversamente a gate o que por um

n

lado faz com que a corrente de gate seja nula e por outro a zona do tipo p

p

da gate vá aumentando de tamanho, diminuindo a largura do canal n por

onde passa IDS. Ao valor de VDS que estrangula o canal n chama-se VP.

O comportamento DC do JFET pode ser descrito pela equação (1):

I DS

V

I DSS 1 GS

VP

2

.

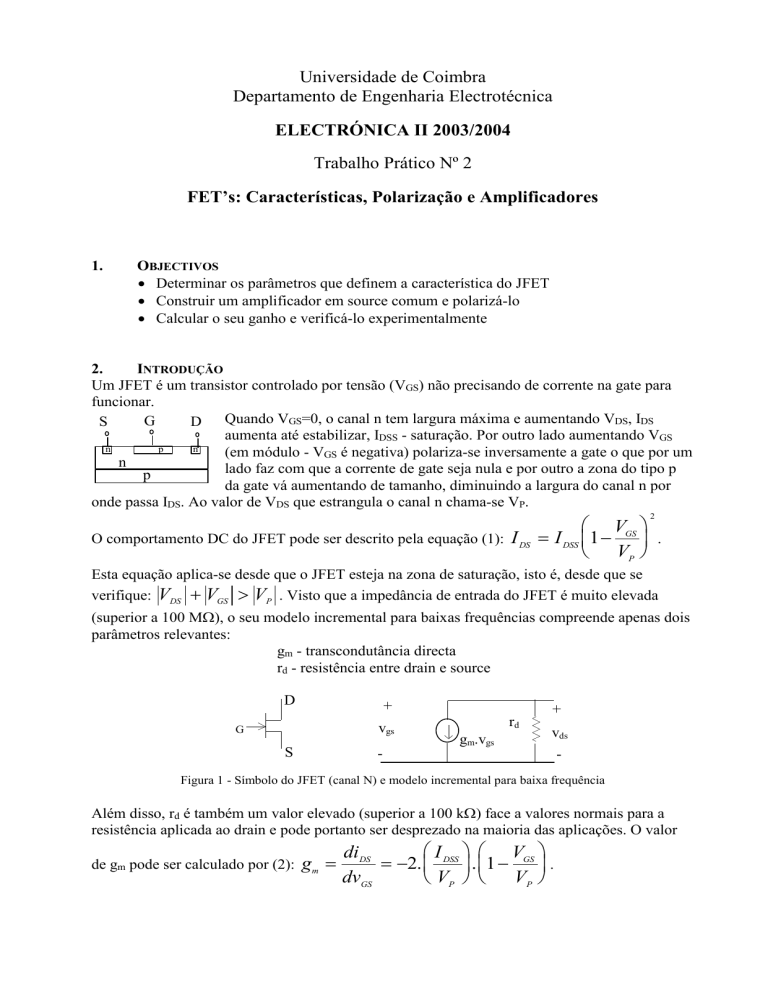

Esta equação aplica-se desde que o JFET esteja na zona de saturação, isto é, desde que se

verifique: VDS VGS VP . Visto que a impedância de entrada do JFET é muito elevada

(superior a 100 M), o seu modelo incremental para baixas frequências compreende apenas dois

parâmetros relevantes:

gm - transcondutância directa

rd - resistência entre drain e source

D

+

vgs

G

S

rd

gm.vgs

+

vds

-

-

Figura 1 - Símbolo do JFET (canal N) e modelo incremental para baixa frequência

Além disso, rd é também um valor elevado (superior a 100 k) face a valores normais para a

resistência aplicada ao drain e pode portanto ser desprezado na maioria das aplicações. O valor

de gm pode ser calculado por (2):

gm

I V

diDS

2. DSS . 1 GS .

dvGS

VP VP

3.

DETERMINAÇÃO DE IDSS E DE VP

De acordo com (1) apenas é necessário conhecer os valores de VP e de IDSS para conhecer a

característica de saída para a zona de saturação.

Limitador de

corrente

+

D

G

+

S

VGG

+

+

=

V

V

Figura 2 - Circuito para a determinação de VP

VP pode ser

determinado com o

auxílio do circuito da

figura 2. Aumenta-se o

valor de VGS (no

sentido negativo) até

obter uma indicação de

impedância infinita no

ohmímetro (utilizar

para esta medição uma escala de 100 k).

Na figura 2 também aparece o circuito equivalente do ohmímetro digital (notar que é preciso

ligar ao drain o terminal do ohmímetro que tem tensão positiva). Como se vê, o ohmímetro

polariza adequadamente o circuito de drain do JFET, e a indicação de impedância infinita (para

uma escala de alta resistência) significa que a corrente no circuito exterior é muito baixa.

Portanto, este é um método válido de detectar a condição de “pinch-off”, e logo VP. A resistência

de 10 k é simplesmente uma precaução contra o risco de aplicar uma corrente escessiva na

gate.

IDSS é a corrente que flui através do drain quando

VGS=0 e o JFET está saturado. Se fizermos VGS=0 e

formos aumentando VDS, a corrente de drain vai

subindo até estabilizar - e o valor em que estabiliza é

precisamente IDSS. Assim, IDSS pode ser determinado

aumentando gradualmente VDD no circuito da figura 3

ao mesmo tempo que se monitoriza IDS.

I

G

D

V

VDD

S

Figura 3 - Circuito para a determinação de IDSS

4.

POLARIZAÇÃO

VDD=15V

RD

ci

CD

G

+

S

vi

RS

500k

CS

Figura 4 - Circuito de auto-polarização para o

amplificador source-comum

V0

A figura 4 mostra o chamado circuito de autopolarização para o JFET canal N. Normalmente, em

circuitos amplificadores, o JFET é utilizado na zona

de saturação. Então, para estabelecer um

determinado valor IDS, resolve-se a equação:

2

V

I DS I DSS . 1 GS , para obter VGS; a

VP

equação VGS RS * I DS (3) permite obter RS.

Conhecido VGS e logo também VG=-VGS,

determina-se RD para obter o valor de VDS

desejado.

VDD = (RD+RS)* IDS + VDS

AMPLIFICAÇÃO COM JFET’S

5.

No circuito da figura 4, o JFET está na configuração de source-comum. Com efeito, para a

componente de sinal o condensador CS curto-circuita efectivamente a resistência RS. Assim, o

circuito equivalente para sinal será o da figura 5:

+

+

vi

-

500k

vgs

+

rd

gm.vgs

-

v0

RD

-

Figura 5 - Equivalente para sinal do circuito da figura 5

6.

Como rd>>RD, rd pode ser desprezado

face a RD. Assim, o ganho em voltagem

é expresso simplesmente por

V0

gm . RD

Vi

MONTAGENS

a) Determinar VP e IDSS utilizando as montagens das figuras 2 e 3. Os JFET’s utilizados -BF245C

- têm IDSS compreendido entre 12 e 25 mA e VP inferior (em módulo) a -8V:

b) Polarizar o circuito da figura 4, para

1

I DS . I DSS e VDS VGS VP 2 . Determinar

3

os valores apropriados para RS e RD (ver ponto 4. - Polarização).

c) Montar o circuito da figura 4, utilizando C0=Ci=0,22F e CS tal que: RS*CS>10-2.

d) Verificar os valores ID e VDS face aos pretendidos e explicar qualquer eventual divergência (se

necessário, refazer as determinações de VP e IDSS).

e) Aplicar uma onda sinusoidal de 10 kHz a Vi. Determinar (experimentalmente) qual a máxima

excursão simétrica que se obtém em V0. Justificar o valor encontrado.

f) Também com uma onda sinusoidal de 10 kHz em Vi, medir o ganho

o valor encontrado.

7.

MATERIAL

1 JFET BF245C

Resistências: 10 k500 koutras conforme cálculos

Condensadores: 2x 0,22 F, outro conforme cálculos

2 multímetros digitais

Esquema do JFET BF245C

(visto por baixo)

Dreno (pino da esquerda),

Source (pino do meio), e Gate, pino da direita

V0

Vi

do circuito. Justificar