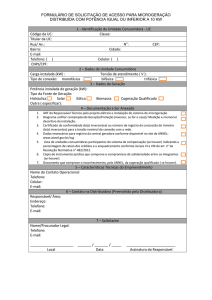

Microeletrônica

Germano Maioli Penello

http://www.lee.eng.uerj.br/~germano/Microeletronica%20_%202015-1.html

Sala 5145 (sala 17 do laboratorio de engenharia elétrica)

Aula 17

1

Modelos para projetos digitais

Após ver alguns detalhes da fabricação dos MOSFETs, agora veremos modelos

que utilizaremos em designs digitais

De uma forma simples, o MOSFET é analisado em

projetos digitais como uma chave logicamente controlada.

2

Modelos para projetos digitais

Efeito Miller

Neste exemplo, a capacitância vista pela fonte de entrada e de saída é o

dobro da capacitância conectada entre a entrada e a saída

Usaremos este resultado para construir um modelo de MOSFET para análise

digital.

3

Modelo de MOSFET digital

Resistência de chaveamento efetiva

Como estimar

uma resistência

para este

resultado?

Inverso da inclinação da reta

4

Modelo de MOSFET digital

Resistência de chaveamento efetiva

Modelo inicial para um MOSFET chaveando

Limitação desse modelo: Consideração feita que o tempo de subida e de

descida é zero. O ponto que define a chave aberta e fechada é bem definido.

Usado para cálculo a mão, apresentam resultados dentro de um fator de dois

do resultado obtido por simulação ou pela experiência.

5

Modelo de MOSFET digital

Resistência de chaveamento efetiva

O modelo feito aqui não inclui a redução da mobilidade observada em

dispositivos submicron. Um melhor resultado é obtido através de valores

medidos ou simulados:

NMOS de canal longo (fator de escala de 1 mm e VDD = 5V)

PMOS de canal longo (fator de escala de 1 mm e VDD = 5V)

mobilidade elétron é maior que a do buraco

6

Modelo de MOSFET digital

Resistência de chaveamento efetiva

MOSFETs de canal curto não seguem a lei quadrática para a corrente!

Usamos a corrente Ion para estimar a resistência

NMOS de canal curto (fator de escala de 50 nm e VDD =1V)

PMOS de canal longo (fator de escala de 1 mm)

Equações reescritas para incluir L

7

Modelo de MOSFET digital

Efeitos Capacitivos

Adicionando efeitos das capacitâncias no modelo

Cox é a capacitância na região de triodo (superestimado para facilitar as

contas à mão – cálculo melhor é feito com simulações)

Capacitância é vista como 2(Cox/2) = Cox

8

Modelo de MOSFET digital

Efeitos Capacitivos

Adicionando efeitos das capacitâncias no modelo

Modelo

melhorado

9

Modelo de MOSFET digital

Resumo

10

Tempo de transição e de atraso

Relembrando

11

Tempo de transição e de atraso

Tempo de subida - tr

Tempo de subida da saída- tLH

Tempo de descida- tf

Tempo de descida da saída- tHL

Tempo de atraso low to high - tPLH

Tempo de atraso high to low - tPHL

12

Tempo de transição e de atraso

No nosso modelo digital:

Ctot = capacitância total entre o dreno e o terra.

Modelo simplificado para ser usado no cálculo a mão apenas!

13

Exemplo

Descarga

Carga

14

Exemplo

Descarga

Carga

Canal longo

Canal curto

15

Exemplo

Descarga

Carga

16

Exemplo

Simulação

17

Projeto digital

Por que NMOS e PMOS têm tamanhos diferentes?

18

Projeto digital

Por que NMOS e PMOS têm tamanhos diferentes?

Casamento da resistência de chaveamento efetiva

19

MOSFET pass gate

NMOS é bom para

passar sinal lógico 0

NMOS não é bom

para passar sinal

lógico 1

20

MOSFET pass gate

NMOS é bom para

passar sinal lógico 0

NMOS não é bom

para passar sinal

lógico 1

21

MOSFET pass gate

Em uma análise complementar, observamos que

PMOS não é bom

para passar sinal

lógico 0

PMOS é bom para

passar sinal lógico 1

22

Atraso num pass gate

Capacitância na entrada

Capacitância na saída

Podemos estimar o atraso pela capacitância de saída:

23

Atraso num pass gate

Exemplo:

24

Atraso num pass gate

Valor calculado diferente do medido (simulado)!

Cálculo manual fornece resultados aproximados e ajuda a indicar o local da

limitação de velocidade num circuito digital, mas não fornece um resultado exato!

25

Transmission gate

Acoplar um NMOS e um PMOS

Desvantagens:

Aumento de área utilizada no leiaute

Dois sinais de controle

26

Atraso em conexão de

pass gates

Equação de uma linha de transmissão (aula 8)

10x NMOS (50 nm) em série tdelay ~

= 74ps

27

Medidas

Comentário sobre medidas com osciloscópios

Por que usar a ponta de prova em vez de um fio simples?

Cabo coaxial

Ponta de prova

Impedância do osciloscópio

O cabo coaxial introduz uma capacitância significativa no circuito de medida.

O cabo (1m) e o osciloscópio têm em conjunto uma capacitância de 110pF.

Todo ponto medido sofrerá o efeito desta capacitância e da resistência do osciloscópio

28

Medidas

Comentário sobre medidas com osciloscópios

Por que usar a ponta de prova em vez de um fio simples?

Ponta de prova

Cabo coaxial

Impedância do osciloscópio

Para evitar isso, a ponta de prova tem um capacitor e um resistor acoplados

(ponta de prova compensada).

RC da ponta de prova é 9x a impedância do cabo em conjunto com o osciloscópio

para que exista um divisor de tensão de 10:1 em toda frequência de interesse.

Se, em vez de medir com a ponta de prova, tentarmos medir com um cabo ligado

direto no osciloscópio, não teremos bons resultados para frequências altas

29

Inversor CMOS

Bloco de construção fundamental para a circuitos digitais

Analise o circuito quando a entrada está em estado lógico alto.

Repita esta análise para a entrada em estado lógico baixo.

30

Inversor CMOS

Bloco de construção fundamental para a circuitos digitais

A dissipação de potência estática do inversor é praticamente zero!

O NMOS e o PMOS podem ser projetados para ter as mesmas características

O gatilho de chaveamento lógico pode ser alterado com o tamanho dos MOSFETs

31

Inversor CMOS

Características DC

Característica de transferência de tensão

32

Inversor CMOS

Características DC

Característica de transferência de tensão

Pontos A e B definidos pela inclinação da reta igual a -1

Ventrada < VIL estado lógico 0 na entrada

Ventrada > VIH estado lógico 1 na entrada

VIL < Ventrada < VIH não tem estado lógico definido

Situação ideal VIH - VIL = 0

33

Inversor CMOS

Características DC

VTC - Característica de transferência de tensão

34

Inversor CMOS

Características DC

VTC - Característica de transferência de tensão

Importante – Se o sinal não varre totalmente os limites inferiores e superiores

da tensão uma corrente significativa passa pelo inversor! (potência dissipada!)

O mesmo fenômeno é significativo se o transistor chaveia lentamente.

35

Inversor CMOS

Ruído

Os limites de ruído indicam quão bem o inversor opera em condições ruidosas.

Caso ideal:

Se

Caso ideal:

36

Inversor CMOS

Ponto de chaveamento do inversor (VSP)

Os dois transistores estão na região de saturação e a mesma corrente passa por eles

37

Inversor CMOS

Limite de ruído e VTC ideais

Nesta situação idealizada, os MOSFETs nunca estão ligados em um mesmo instante

Limites de ruídos iguais garante melhor performance

38

Exemplos

Se bn/bp = 1, temos VSP = VDD/2

Desenhando MOSFETs

com mesmo L

Mesmo resultado eu

obtivemos para fazer

Num MOSFET de canal longo

39

Trabalho

Perdeu ponto quem incluiu erros no texto!

Ex:

.include/pasta

- isso está errado! Você deve incluir arquivo, não pasta!

.include/pasta/arquivo.txt - correto!

Perdeu ponto quem escreveu em unidades de l e não incluiu a escala!

.options scale = 50 n

40

Projetos

•

•

•

•

•

•

•

•

Somador completo de dois bits

Subtrator completo de dois bits

Flip flop D edge triggered

Flip flop T edge triggered

Flip flop SR com saida tristate

Quad 2-input MUX

Ring oscillator

Schmidt trigger

41