EDA PARA PROJETO DE CIRCUITO INTEGRADO

ANALÓGICO BASEADO EM TÉCNICAS DE PARETO

Rafael Castello Wassouf, Rodrigo Alves de Lima Moreto, Salvador Pinillos Gimenez.

Centro Universitário da FEI

Av. Humberto de Alencar Castelo Branco, 3972.

[email protected], [email protected]

Resumo: Visto que o projeto de circuitos integrados

(CIs) analógicos é um sistema de múltiplas variáveis de

entrada e múltiplos objetivos e que atualmente sua

otimização é complexa, demorada e depende da

experiência do projetista, este trabalho de iniciação

cientifica visa à implementação de uma ferramenta

computacional de auxílio ao projeto de CIs analógicos

utilizando a metodologia de Fronteira de Pareto. O uso

desta ferramenta permitirá a redução do ciclo de projeto

dos CIs analógicos.

1. Introdução

No presente contexto mundial, com o desenfreado

avanço tecnológico e a alta demanda por projetos de

engenharia, que utilizam em sua implementação os

Circuitos Integrados (CIs) analógicos são enormes.

Além disso, atualmente existem poucas ferramentas de

auxílio ao projeto de CIs analógicos (Electronic Design

Automation, EDA). Elas servem para auxiliar o projeto

de CIs analógicos e reduzir o tempo de projeto [1].

O projeto de CIs analógicos é um sistema de

múltiplas variáveis de entrada com múltiplas variáveis

de saída (Multi-Objective Problem, MOP) [1].

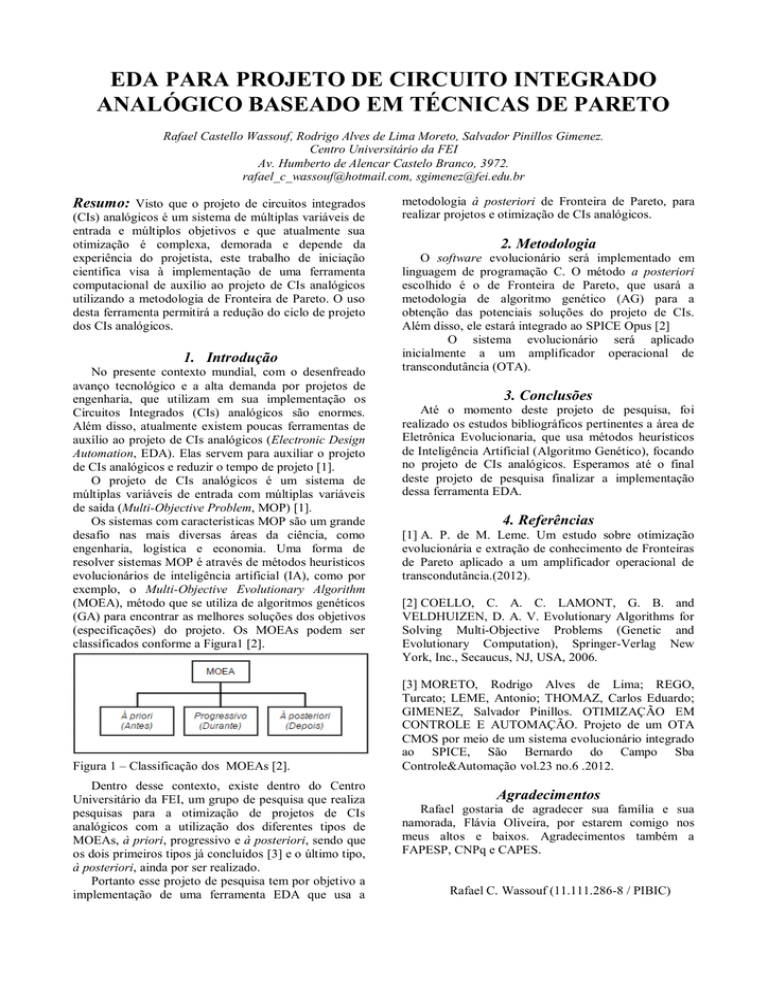

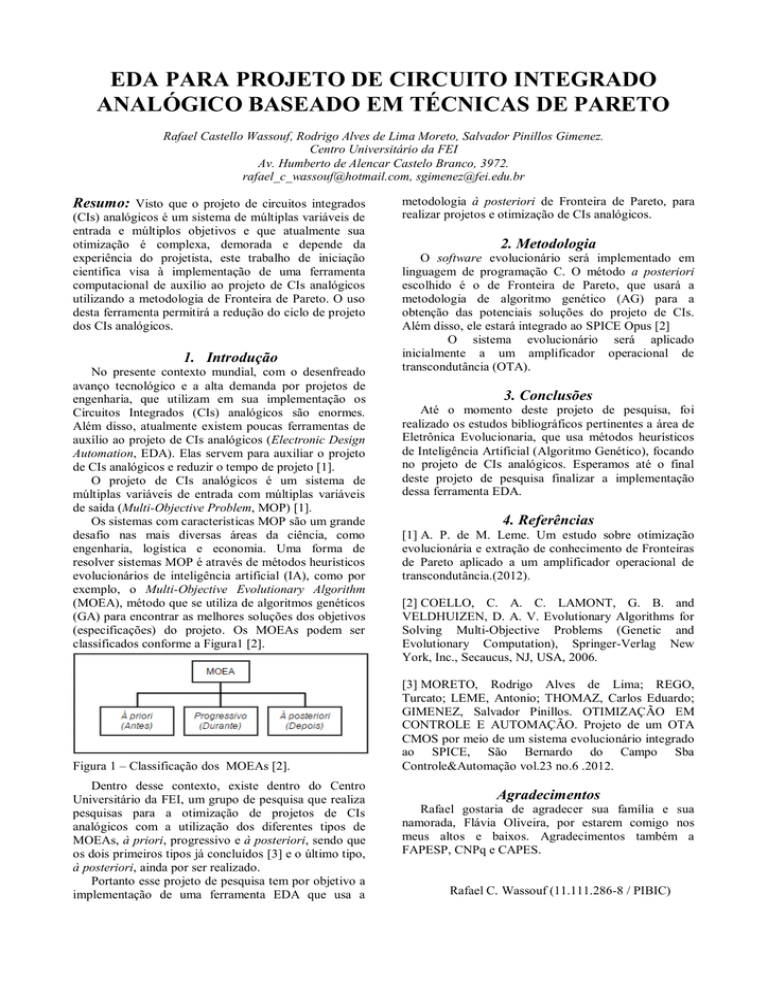

Os sistemas com características MOP são um grande

desafio nas mais diversas áreas da ciência, como

engenharia, logística e economia. Uma forma de

resolver sistemas MOP é através de métodos heurísticos

evolucionários de inteligência artificial (IA), como por

exemplo, o Multi-Objective Evolutionary Algorithm

(MOEA), método que se utiliza de algoritmos genéticos

(GA) para encontrar as melhores soluções dos objetivos

(especificações) do projeto. Os MOEAs podem ser

classificados conforme a Figura1 [2].

Figura 1 – Classificação dos MOEAs [2].

Dentro desse contexto, existe dentro do Centro

Universitário da FEI, um grupo de pesquisa que realiza

pesquisas para a otimização de projetos de CIs

analógicos com a utilização dos diferentes tipos de

MOEAs, à priori, progressivo e à posteriori, sendo que

os dois primeiros tipos já concluídos [3] e o último tipo,

à posteriori, ainda por ser realizado.

Portanto esse projeto de pesquisa tem por objetivo a

implementação de uma ferramenta EDA que usa a

metodologia à posteriori de Fronteira de Pareto, para

realizar projetos e otimização de CIs analógicos.

2. Metodologia

O software evolucionário será implementado em

linguagem de programação C. O método a posteriori

escolhido é o de Fronteira de Pareto, que usará a

metodologia de algoritmo genético (AG) para a

obtenção das potenciais soluções do projeto de CIs.

Além disso, ele estará integrado ao SPICE Opus [2]

O sistema evolucionário será aplicado

inicialmente a um amplificador operacional de

transcondutância (OTA).

3. Conclusões

Até o momento deste projeto de pesquisa, foi

realizado os estudos bibliográficos pertinentes a área de

Eletrônica Evolucionaria, que usa métodos heurísticos

de Inteligência Artificial (Algoritmo Genético), focando

no projeto de CIs analógicos. Esperamos até o final

deste projeto de pesquisa finalizar a implementação

dessa ferramenta EDA.

4. Referências

[1] A. P. de M. Leme. Um estudo sobre otimização

evolucionária e extração de conhecimento de Fronteiras

de Pareto aplicado a um amplificador operacional de

transcondutância.(2012).

[2] COELLO, C. A. C. LAMONT, G. B. and

VELDHUIZEN, D. A. V. Evolutionary Algorithms for

Solving Multi-Objective Problems (Genetic and

Evolutionary Computation), Springer-Verlag New

York, Inc., Secaucus, NJ, USA, 2006.

[3] MORETO, Rodrigo Alves de Lima; REGO,

Turcato; LEME, Antonio; THOMAZ, Carlos Eduardo;

GIMENEZ, Salvador Pinillos. OTIMIZAÇÃO EM

CONTROLE E AUTOMAÇÃO. Projeto de um OTA

CMOS por meio de um sistema evolucionário integrado

ao SPICE, São Bernardo do Campo Sba

Controle&Automação vol.23 no.6 .2012.

Agradecimentos

Rafael gostaria de agradecer sua família e sua

namorada, Flávia Oliveira, por estarem comigo nos

meus altos e baixos. Agradecimentos também a

FAPESP, CNPq e CAPES.

Rafael C. Wassouf (11.111.286-8 / PIBIC)