ELD - Eletrônica Digital

Aula 5 – Circuitos Aritméticos e Códigos Especiais

Prof. Antonio Heronaldo de Sousa

Agenda

- Somador Incompleto

- Somador Completo

- Projeto de Somador para N bits

- Somador Paralelo CI-7483

- Números Binários Sinalizados

- Circuito Integrado Comparador 7485

- Circuitos de Subtração

- Adição BCD

- Unidade Lógica e Aritmética - ALU

- Paridade

- Código Gray

Somador Incompleto

Somador Incompleto: também chamado de meio-somador, é um circuito

combinacional que realiza a soma aritmética de dois bits de entrada (A e B), gerando

como saída um bit de soma (S) e um bit de transporte (C = carry ou “vai um”).

A

S

Meio-somador

B

C

A

B

S

C

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Exemplo:

Somador Incompleto - Projeto

A

B

S

C

0

0

0

0

0

1

1

0

1

0

1

0

1

1

0

1

Somador Completo

Somador Completo: é um circuito combinacional que realiza a soma aritmética de

dois bits de entrada (A e B) e o bit de transporte de entrada (Cin), gerando como

saída um bit de soma (S) e um bit de transporte de saída(Cout).

A

B

Cin

Exemplo:

Somador

Completo

S

Cout

A

B

Cin

S

Cout

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Somador Completo - Projeto

A

B

Cin

S

Cout

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Somador Completo – Projeto alternativo

A

B

Cin

S

Cout

0

0

0

0

0

0

0

1

1

0

0

1

0

1

0

0

1

1

0

1

1

0

0

1

0

1

0

1

0

1

1

1

0

0

1

1

1

1

1

1

Projeto Somador para N bits: Somador Paralelo

Somador Paralelo: é um circuito combinacional que realiza a soma aritmética de

dois números binários de entrada (A e B), que considera um transporte de entrada

(Cin) e gera uma soma (S) de saída, com o mesmo número de bits dos operandos, e

um bit de transporte de saída final (Cout).

Este tipo de somador é conhecido como Somador Paralelo Ripple Carry, pois sua

topologia baseia-se na propagação (ripple) dos bits de transporte (carry)

intermediários. Nessa topologia os bits de carry e soma de cada estágio só estão

disponíveis após os tempos de propagação dos estágios anteriores.

Somador Paralelo CI-7483

Realiza a soma aritmética de dois números binários de entrada (A e B), de 4 bits.

Considera um transporte de entrada (C0) e gera uma soma de saída (∑) de 4 bits e

um bit de transporte final (C4).

Números Binários Sinalizados

Sinal-Magnitude ou Sinal-Módulo: processo de representação dos

números sinalizados, onde cada número é representado por um bit de sinal

(o mais significativo: An) e o restante (An-1...A0) forma sua magnitude ou

módulo.

Sinal

Magnitude

Binário+

A 6 A5 A 4 A 3 A 2 A 1 A 0

0

1

1

0

1

0

0

A6 A5 A4 A3 A2 A1 A0

1

1

1

0

1

0

0

+52(10)

-52(10)

Dec+

Binário-

Dec-

0 000 0

1 000 0

0 001 +1

1 001 -1

0 010 +2

1 010 -2

0 011 +3

1 011 -3

0 100 +4

1 100 -4

0 101 +5

1 101 -5

0 110 +6

1 110 -6

0 111 +7

1 111 -7

Sinal-Magnitude ou Sinal-Módulo

Procedimento de Soma/Subtração:

Sinais iguais: Soma-se os dois módulos; o sinal do resultado é o mesmo

dos operandos; e pode haver estouro de módulo.

Sinais diferentes: Encontra-se o número com maior módulo; subtrai-se o

menor do maior; e o sinal do resultado é o mesmo do operando de maior

módulo.

Desvantagem: Possui lógica que requer vários testes de condições,

tornando os circuitos mais complexos.

Números Binários Sinalizados

Complemento de Um: processo de representação dos números

sinalizados, onde cada número tem seus bits invertidos para formar seu

complemento. Equivale a efetuar 1 menos cada dígito do número.

A6 A 5 A4 A3 A2 A1 A0

0

1

1

0

1

0

0

A6 A5 A4 A3 A2 A1 A0

1

0

0

1

0

1

1

+52(10)

-52(10)

Binário+

Dec+

Binário-

Dec-

0000

0

1111

0

0001

+1

1110

-1

0010

+2

1101

-2

0011

+3

1100

-3

0100

+4

1011

-4

0101

+5

1010

-5

0110

+6

1001

-6

0111

+7

1000

-7

Complemento à Base

Complemento à base: processo de representação dos números

sinalizados, onde subtrai-se da base cada dígito do número para formar seu

complemento.

Exemplo: base 10 com 1 dígito: 10 - X

Decimal

0

1

5

6

7

8

9

Número

Sinalizado

0

+1 +2 +3 +4 -5

-4

-3

-2

-1

Exemplos:

3–2=1

3 + 8 = 11 → 1

2 – 3 = -1

2 + 7 = 9 → -1

2

3

4

Equivale a subtrair cada dígito de (base – 1) e

depois somar 1 ao resultado.

9

-2

---7 +1 8

9

-3

---6 +1 7

Complemento à Base

Complemento à base: processo de representação dos números

sinalizados, onde subtrai-se da base cada dígito do número para formar seu

complemento.

Exemplo: base 10 com 2 dígitos: 100 - X

Decimal

0

1

3

...

49

51

...

97

98

99

Número

Sinalizado

0

+1 +2 +3

...

+49 -50 -49

...

-3

-2

-1

Exemplos:

2 – 3 = -1

2 + 97 = 99

3–2=1

3 + 98 = 101 → 01

2

50

Equivale a subtrair cada dígito de (base – 1) e

depois somar 1 ao resultado.

99

-03

---96 +1 97

99

-02

---97 +1 98

Complemento de Dois

Complemento de Dois: processo de representação dos números

sinalizados, onde é realizado o complemento de um do número original e

depois somado 1 ao resultado para formar seu complemento.

A6 A 5 A4 A3 A2 A1 A0

0

1

1

0

1

0

0

A6 A5 A4 A3 A2 A1 A0

1

0

0

1

1

0

0

+52(10)

-52(10)

Binário+

Dec+

Binário-

Dec-

0000

0

1111

-1

0001

+1

1110

-2

0010

+2

1101

-3

0011

+3

1100

-4

0100

+4

1011

-5

0101

+5

1010

-6

0110

+6

1001

-7

0111

+7

1000

-8

Complemento de Dois

Procedimento de Soma:

Dois números positivos: Soma-se os dois módulos; o sinal do resultado é o

mesmo dos operandos; e pode haver estouro de módulo.

Exemplo (números de seis bits):

Vai-um

Soma

1 1

0 0 0 1 1 1+

010010

----------------011001

7+

18

---25

Complemento de Dois

Procedimento de Soma:

Dois números negativos: a operação pode ser feita por meio da soma dos

números complementados.

Exemplo (números de seis bits):

Vai-um

1 1 1

Soma

1 1 1 1 0 0+

101101

----------------101001

-4+

-19

----23

010111

23

Complemento de Dois

Procedimento de Soma:

Dois números negativos: a operação pode ser feita por meio da soma dos

números complementados.

Exemplo (números de seis bits):

Vai-um

1 1 1

Soma

1 1 1 1 0 0+

101101

----------------101001

-4+

-19

----23

010111

23

Complemento de Dois

Procedimento de Soma/Subtração:

Números com sinais diferentes: Caso o número seja positivo, deve ser

mantido; caso seja negativo, deve ser complementado; e depois, deve ser

feita a soma.

Exemplo (números de seis bits):

Vai-um

Soma

0

Vai-um

1 0 1 1 0 1+

000100

---------------110001

-19+

4

----15

001111

15

Soma

0

0 0 0 1 0 0+

101101

----------------110001

4+

-19

----15

001111

15

Circuito Integrado Comparador 7485

Realiza a comparação de dois números binários de entrada (A e B), de 4 bits não

sinalizados, gerando três saídas para indicar se A>B, se A=B e se A<B.

Adição em BCD

1º) Somar separadamente os dígitos de mesmo significado; e

2º) Quando a soma de dois dígitos for maior que 910, uma soma

suplementar com 610 deve ser procedida e sempre haverá um transporte

para o próximo estágio da soma.

Exemplo:

Vai-um

111

0010

0101

0100

0001

0111

0101

------------------------------Parcial: 0011

1100

1001

Vai-um

111

= 254

= 175

= 3C9

1

Parcial: 0011

1100

1001

Ajuste+

0110

-------------------------------------------Final:

0100

0010

1001

= 429

Unidade Lógica e Aritmética - ALU

É um circuito combinacional que realiza operações lógicas e aritméticas entre dois

operandos (A0-A3 e B0-B3), indicadas por uma palavra seletora (S0-S3), gerando uma

palavra de resultado F0-F3.

ALU no CI-74181

Bit de Overflow (V)

Bit sinalizador de condição de estouro de representação numérica em um dado

conjunto de bits.

Exemplo: Soma de 4 bits

A

B

S

C3

C4

V

01015

01106

101111

1

0

1

01015

00102

01117

0

0

0

01015

1010-6

1111-1

0

0

0

01106

1011-5

00011

1

1

0

1011-5

1010-6

0101-11

0

1

1

Bit de Paridade

Bit extra anexado a um conjunto de bits para indicar que o número de bits em “1”

é par ou ímpar. É usado em comunicação de dados para minimizar erros. A

paridade pode ser par ou ímpar.

Ex. Paridade PAR

01001→ 01001→ 2=par→

0 01001→ 2=par

10110 → 10110 → 3=ímpar→1 10110→ 4=par

Ex. Paridade ÍMPAR

01001→ 01001→ 2=par→

1 01001→ 3=ímpar

10110 → 10110 → 3=ímpar→ 0 10110→ 3=ímpar

Gerador de Paridade

Gerador de Paridade

Código Gray

Sistema de codificação binária não ponderado, onde apenas um bit varia entre

duas representações consecutivas. É utilizado na codificação de informação para

diminuir erros em sistemas digitais.

Gray (x4)

0000

0001

Binário

Gray(x2)

Bin

Gray

0011

00

00

000

000

0010

01

01

001

001

10

11

010

011

0101

11

10

011

010

0100

0110

0111

1100

100

110

101

111

1111

110

101

1110

111

100

1101

1010

1011

1001

1000

Código Gray

Aplicações: Encoder incremental

Exemplo: mouse de computador

Gray(x2)

00

01

11

10

Código Gray

Circuito para transformar um número Binário de 3 bits para o código Gray:

Bin

Gray

000

000

001

001

010

011

011

010

100

110

101

111

110

101

111

100

Código Gray

Algoritmo genérico: realiza-se um XOR bit a bit do número binário natural com o

resultado de sua divisão por dois.

Bin

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

/2

0000

0000

0001

0001

0010

0010

0011

0011

0100

0100

0101

0101

0110

0110

0111

0111

Gray

0000

0001

0011

0010

0110

0111

0101

0100

1100

1101

1111

1110

1010

1011

1001

1000

Somador com Look Ahead Carry

Somador paralelo que realiza a operação de adição, gerando os bits de transporte

(carry) diretamente a partir dos bits dos operando, sem esperar a propagação

(ripple) dos bits de transporte intermediários.

Subtrator Incompleto

Subtrator Incompleto: também chamado de meio-subtrator , é um circuito

combinacional que realiza a subtração aritmética de dois bits de entrada (A e B),

gerando como saída um bit de subtração (S) e um bit de transporte (T = borrow ou

“vem um”).

A

B

S

T

0

0

0

0

0

1

1

1

1

0

1

0

1

1

0

0

A

S

Meio-subtrator

B

T

Subtrator Incompleto - Projeto

A

B

S

T

0

0

0

0

0

1

1

1

1

0

1

0

1

1

0

0

Subtrator Completo

Subtrator Completo: é um circuito combinacional que realiza a subtração

aritmética de dois bits de entrada (A e B) e o bit de empréstimo de entrada (Tin),

gerando como saída um bit de subtração (S) e um bit de empréstimo de saída

(Tout).

A

B

Tin

Exemplo:

Subtrator

Completo

S

Tout

A

B

Tin

S

Tout

0

0

0

0

0

0

0

1

1

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

Subtrator Completo - Projeto

A

B

Tin

S

Tout

0

0

0

0

0

0

0

1

1

1

0

1

0

1

1

0

1

1

0

1

1

0

0

1

0

1

0

1

0

0

1

1

0

0

0

1

1

1

1

1

Projeto Subtrator para N bits: Subtrator Paralelo

Subtrator Paralelo: é um circuito combinacional que realiza a subtração aritmética

de dois números binários de entrada (A e B), que considera um empréstimo de

entrada (Tin) e gera uma subtração (S) de saída, com o mesmo número de bits dos

operandos, e um bit de empréstimo de saída final (Tout).

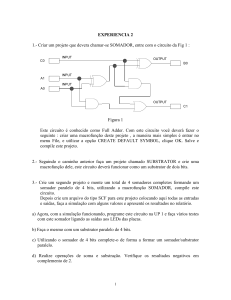

8 – Numa lanchonete, os possíveis combos

combinam refrigerante e pastel, nos tamanhos

pequeno e grande. Deseja-se implementar um

equipamento para realizar o pedido do usuário,

através da seguinte interface, com quatro botões:

Combo

Rp+Pp

Rp+Pg

Rg+Pp

Rg+Pg

No. do Pedido

1

2

3

4

O equipamento deve dar prioridade para o produto

de tamanho maior, caso o usuário aperte os dois

tamanhos e priorizar o tamanho pequeno, para o

caso do usuário não escolher o tamanho do

produto. Além disso, o equipamento deve

apresentar na cozinha um número de 1 a 4, em um

display, para indicar o pedido realizado pelo

usuário. Caso não seja feito pedido, o display deve

permanecer apagado.

Rg

Rp

Pg

Pp

C

B

A

0

0

0

0

0

0

0

0

0

0

1

0

0

1

0

0

1

0

0

1

0

0

0

1

1

0

1

0

0

1

0

0

0

0

1

0

1

0

1

0

0

1

0

1

1

0

0

1

0

0

1

1

1

0

1

0

1

0

0

0

0

1

1

1

0

0

1

0

1

1

1

0

1

0

1

0

0

1

0

1

1

1

0

0

1

1

0

0

0

1

1

1

1

0

1

0

1

1

1

1

1

0

1

0

0

1

1

1

1

1

0

0

A

00 01 11 10

Rg

Rp

Pg

Pp

C

B

A

0

0

0

0

0

0

0

00

0

0

0

1

0

0

1

01

1

1

A = /Pg.Pp + Rg./Pg + Rp./Pg

0

0

1

0

0

1

0

11

1

1

A = /Pg.(Pp+Rg+Rp)

0

0

1

1

0

1

0

10

1

1

0

1

0

0

0

0

1

0

1

0

1

0

0

1

B

00 01 11 10

0

1

1

0

0

1

0

00

1

1

0

1

1

1

0

1

0

01

1

1

1

0

0

0

0

1

1

11

1

1

1

0

0

1

0

1

1

10

1

1

1

0

1

0

1

0

0

1

0

1

1

1

0

0

C

00 01 11 10

1

1

0

0

0

1

1

00

1

1

0

1

0

1

1

01

1

1

1

0

1

0

0

11

1

1

1

1

1

1

1

0

0

10

1

1

1

B = /Rg.Pg + Rg./Pg

B = Rg

Pg

C = Rg.Pg