UNIVERSIDADE FEDERAL DE SÃO CARLOS

CENTRO DE CIÊNCIAS EXATAS E DE TECNOLOGIA

DEPARTAMENTO DE COMPUTAÇÃO

NOME:_____________________________________ NUMERO: _______________

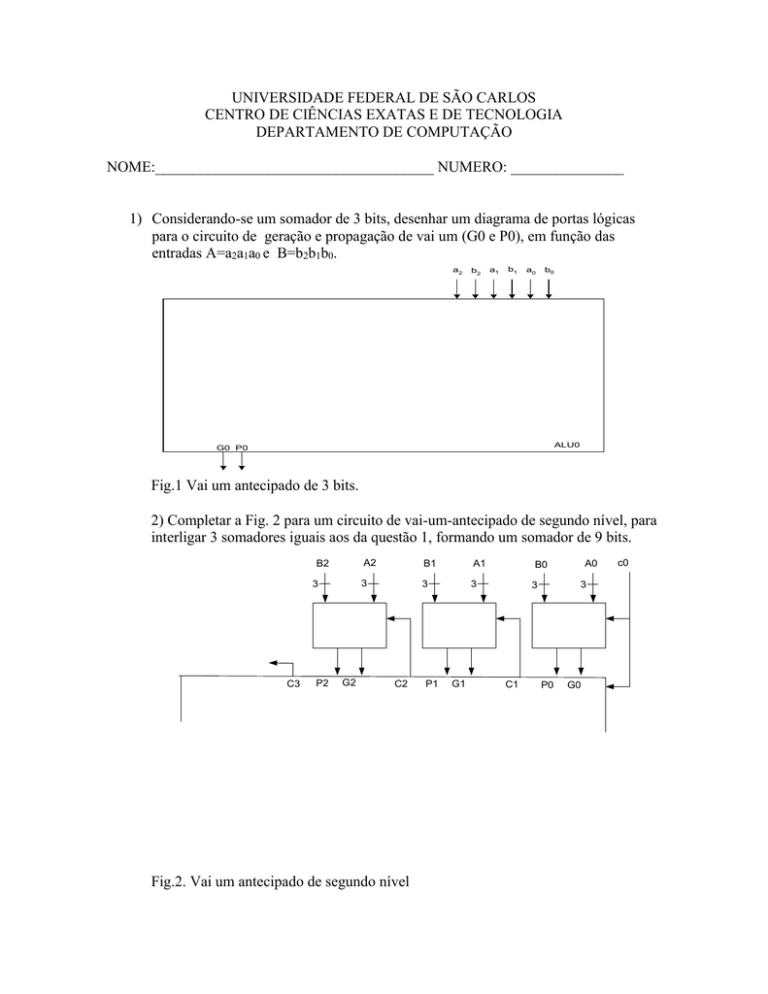

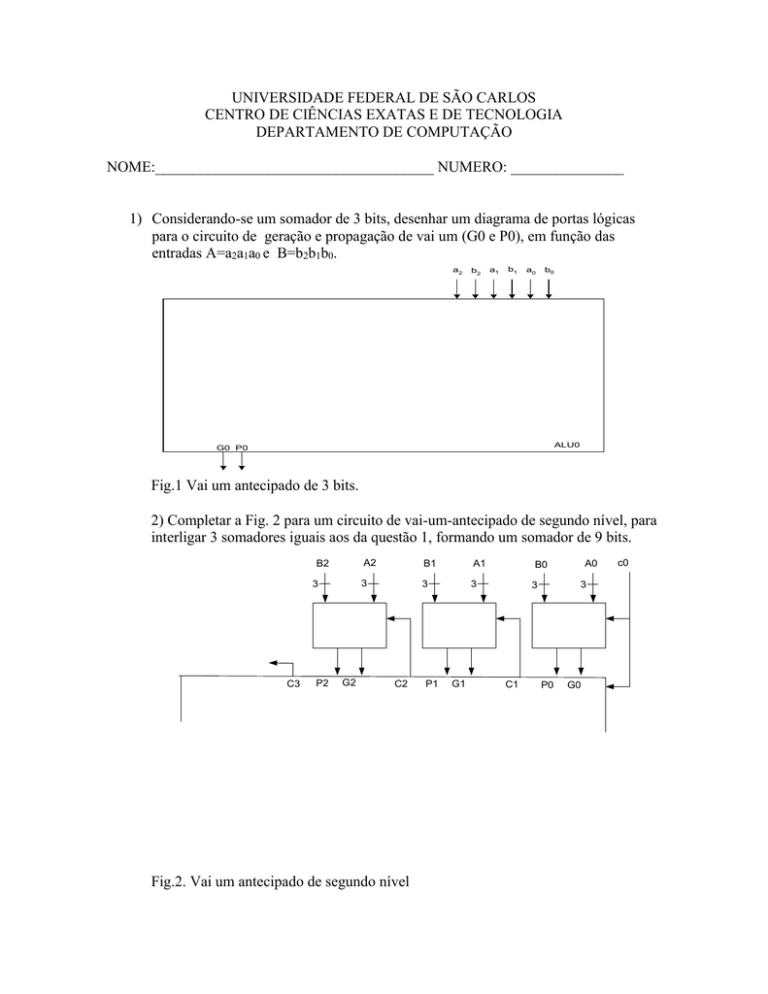

1) Considerando-se um somador de 3 bits, desenhar um diagrama de portas lógicas

para o circuito de geração e propagação de vai um (G0 e P0), em função das

entradas A=a2a1a0 e B=b2b1b0.

a2

b2

a1

b1

a0

b0

ALU0

G0 P0

Fig.1 Vai um antecipado de 3 bits.

2) Completar a Fig. 2 para um circuito de vai-um-antecipado de segundo nível, para

interligar 3 somadores iguais aos da questão 1, formando um somador de 9 bits.

B2

3

C3

P2

G2

A2

B1

A1

3

3

3

C2

Fig.2. Vai um antecipado de segundo nível

P1

G1

A0

B0

3

3

C1

P0

G0

c0

3) Mostrar os valores do produto na multiplicação de

10101 por 10011, no final de cada iteração:

Algoritmo:

0) início

1) testar bit 0 do produto – se bit 0

= 0 vai para o passo 3;

2) somar o multiplicando na

metade esquerda do produto;

3) deslocar o produto, de um bit à

direita;

4) testar se chegou ao fim, caso

contrário voltar para o passo 1;

5) fim.

multiplicando

ALU

shift

teste

write

produto

bit 0

PRODUTO

início = 0000010011

iterações 1=

2=

3=

4=

5=

4) Executar a mesma multiplicação usando o circuito paralelo, preenchendo os valores dos

multiplicandos deslocados Wi, e das saídas nos somadores CSA e CPA.

A

B

010101

010011

gerador de multiplicandos deslocados

5

4

3

2

CSA1

1

CSA2

4

3

1

CSA3

4

1

CSA4

1

CPA

AxB

5) Completar a tabela calculando os valores de E, 2E, M, e valor representado, dos números

em ponto flutuante de 8 bits, anotando se o número é (de)normalizado, infinito ou NaN.

binário

decimal

a) Normalizado,

E

b) Denormalizado,

Número sinal exp

frac

E

2

M

Valor

ponto

representado c) Infinito ou

d) NaN

flutuante

00000000

0

000

0000

10000001

1

000

0001

00010000

0

001

0000

00010010

0

001

0010

00010011

0

001

0011

11110000

1

111

0000

01110010

0

111

0010