Circuitos Aritméticos

Notas:

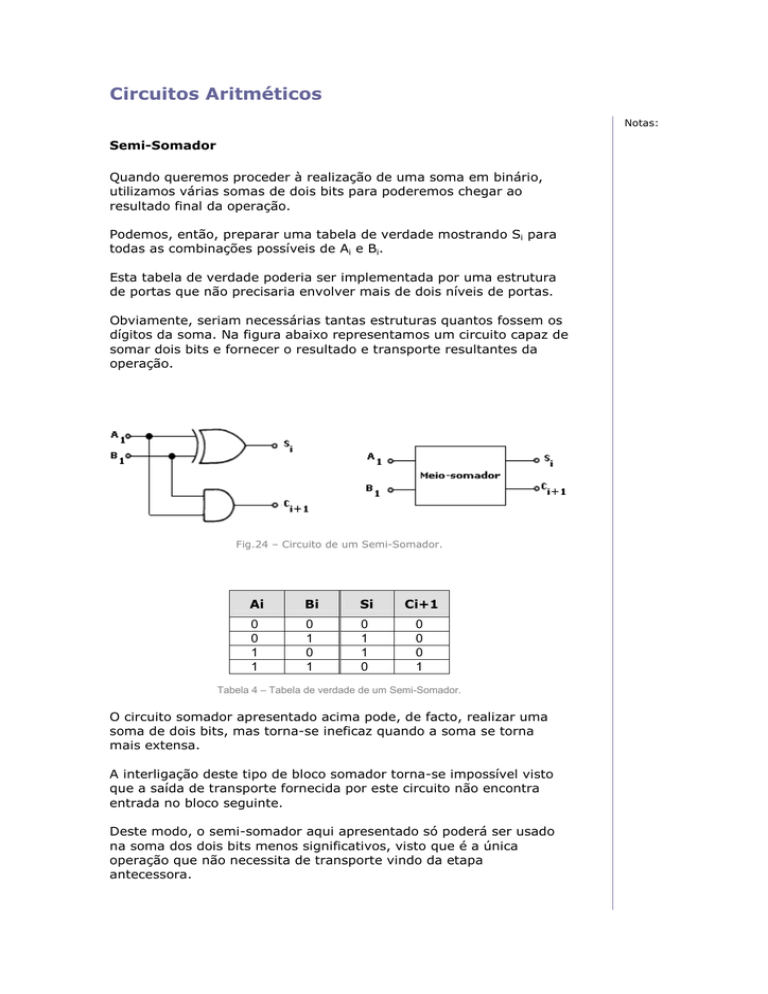

Semi-Somador

Quando queremos proceder à realização de uma soma em binário,

utilizamos várias somas de dois bits para poderemos chegar ao

resultado final da operação.

Podemos, então, preparar uma tabela de verdade mostrando Si para

todas as combinações possíveis de Ai e Bi.

Esta tabela de verdade poderia ser implementada por uma estrutura

de portas que não precisaria envolver mais de dois níveis de portas.

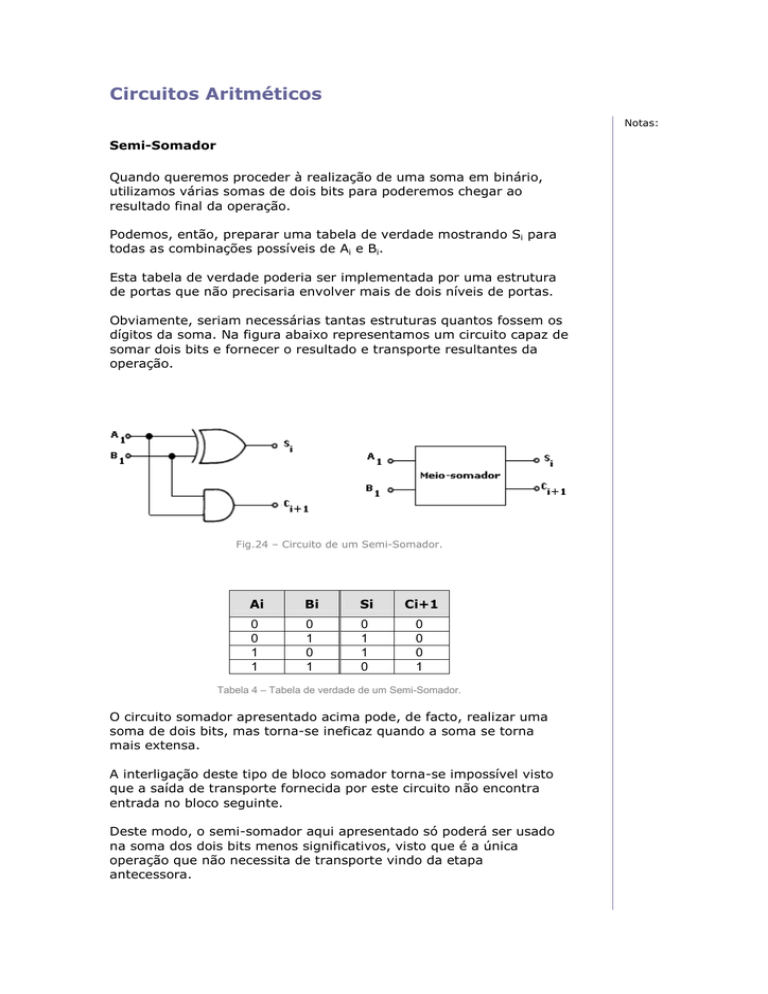

Obviamente, seriam necessárias tantas estruturas quantos fossem os

dígitos da soma. Na figura abaixo representamos um circuito capaz de

somar dois bits e fornecer o resultado e transporte resultantes da

operação.

Fig.24 – Circuito de um Semi-Somador.

Ai

Bi

Si

Ci+1

0

0

1

1

0

1

0

1

0

1

1

0

0

0

0

1

Tabela 4 – Tabela de verdade de um Semi-Somador.

O circuito somador apresentado acima pode, de facto, realizar uma

soma de dois bits, mas torna-se ineficaz quando a soma se torna

mais extensa.

A interligação deste tipo de bloco somador torna-se impossível visto

que a saída de transporte fornecida por este circuito não encontra

entrada no bloco seguinte.

Deste modo, o semi-somador aqui apresentado só poderá ser usado

na soma dos dois bits menos significativos, visto que é a única

operação que não necessita de transporte vindo da etapa

antecessora.

Somador Completo

Numa soma de dois números binários de n bits, realizada coluna a

coluna, os dígitos menos significativos A0 e B0 são somados em

primeiro lugar, gerando um bit de soma S0 e um bit de transporte C1.

Para realizar esta operação, seria adequado apenas um

semi-somador. Na próxima posição, todavia, devemos combinar três

dígitos: os bits A1 e B1 e o bit de transporte C1 da coluna anterior.

São necessárias somas similares de três bits nas colunas seguintes.

Tal como na soma de dois dígitos, na de três dígitos Ai, Bi e o

transporte Ci geram um resultado da soma Si e um transporte Ci+1

(Co).

De seguida, pode observar um circuito somador completo (Fig.25) e

uma tabela de verdade para Si e Ci+1 (Tabela 5).

Fig.25 – Circuito Somador Completo.

Ai

0

0

0

0

1

1

1

1

Bi

0

0

1

1

0

0

1

1

Ci

0

1

0

1

0

1

0

1

Si

0

1

1

0

1

0

0

1

Ci+1

0

0

0

1

0

1

1

1

Tabela 5 – Tabela de verdade de um Somador Completo.

A soma em paralelo usa um número de blocos somadores completos

de acordo com os bits dos números a serem somados.

Em princípio, o primeiro somador usado para A0 e B0 poderia ser um

semi-somador. Se for usado um somador completo, a entrada de

transporte do primeiro somador deve ser 0.

O primeiro somador combina, então, A0 e B0 para obter um bit de

soma S0 e um bit de transporte C1.

Notas:

Este bit de transporte é combinado no somador seguinte com os bits

A1 e B1 para gerar S1 e C2, e assim por diante.

Notas:

Fig.26 – Circuito Somador Combinado.

Subtracção usando o Complemento a 2

Sabemos que podemos realizar operações de subtracção usando uma

soma, se calcularmos o complemento a dois do segundo operando: Z

= A – B = A + (– B).

Sabemos também que o complemento a dois de um número envolve

uma operação de negação e outra de adição: –B = (NOT B) + 1.

Podemos então expressar a operação apenas com operações de

adição: Z = A + (NOT B) + 1.

Na figura abaixo podemos verificar a realização prática deste tipo de

subtractor.

O complemento a 1 do subtractor é realizado por portas inversoras,

enquanto que a soma de uma unidade realiza-se colocando a entrada

de transporte da primeira etapa somadora a um nível lógico 1.

Fig.27 – Circuito Subtractor.

Comparador

Notas:

Como o nome indica, os comparadores digitais são utilizados para

comparar dois números escritos em binário, indicando nas suas saídas

se um número é maior, menor ou igual a outro.

Os números a comparar podem ter um comprimento ou número de

bits que em princípio depende apenas da aplicação em vista.

O comparador mais simples será o que compara dois números A e B

de apenas 1 bit, tendo 3 saídas M, m e l.

Fig.28 – Circuito Comparador.

Se quisermos, no entanto, comparar mais do que um bit, teremos que

ligar módulos comparadores de 1 bit em cascata, de modo que a

informação se vá transmitindo de uns para outros, como se mostra na

figura abaixo.

Fig.29 – Circuito comparador múltiplo.

Repare-se que o módulo das entradas A7, B7 é igual ao que vimos

atrás, mas os módulos seguintes, além das entradas de dados, têm

mais três entradas adicionais a que chamamos M’, m’, I’ e que

indicam se nos módulos à sua esquerda os números parciais A e B

correspondem a A>B, A<B ou A=B.

Como se pode observar na Figura 29, os módulos de maior peso são

ligados aos de menor peso, visto que a comparação de dois números

se realiza a partir dos bits mais significativos.

Se durante a comparação de dois bits se verificar uma igualdade, o

próximo módulo irá comparar os dois bits seguintes.

No entanto, se durante a comparação se verificar uma diferença nos

bits comparados, determina-se imediatamente o resultado global da

comparação.

Na Figura 30 encontra-se o circuito interno de um comparador capaz

de aceitar o resultado de uma comparação anterior.

Fig.30 – Circuito para aceitação de uma comparação.

Notas: