6.1 – ADIÇÃO BINÁRIA

0+0+0=0

0+0+1=1

0 + 1 + 1 = 10

1 + 1 + 1 = 11

Exemplos de soma binária

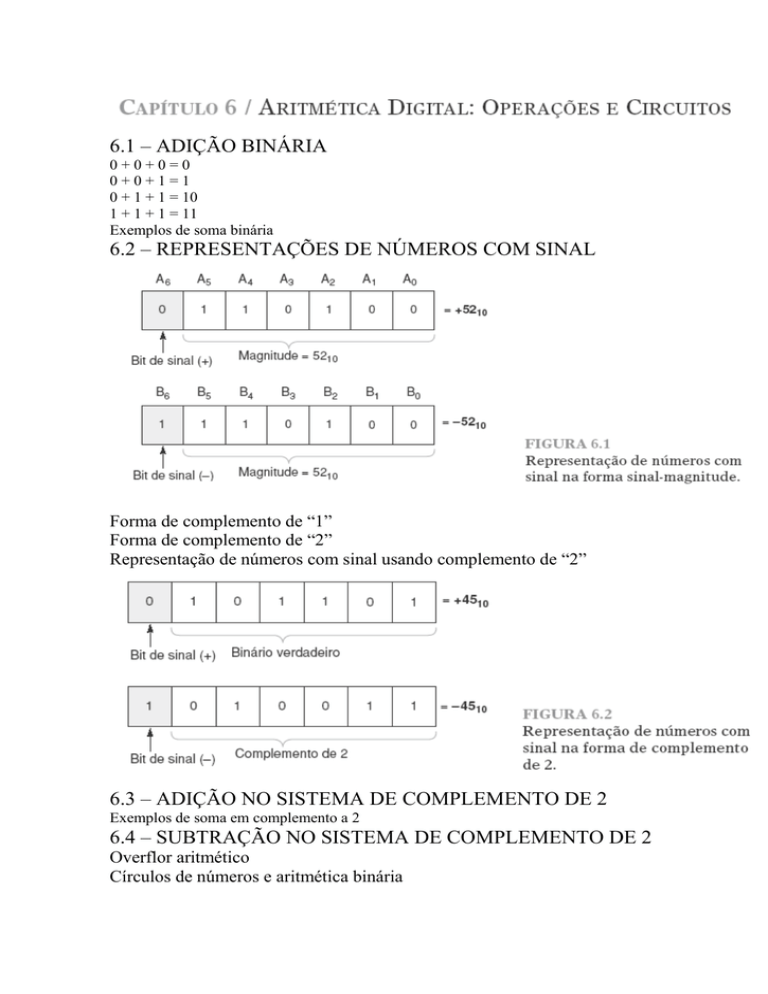

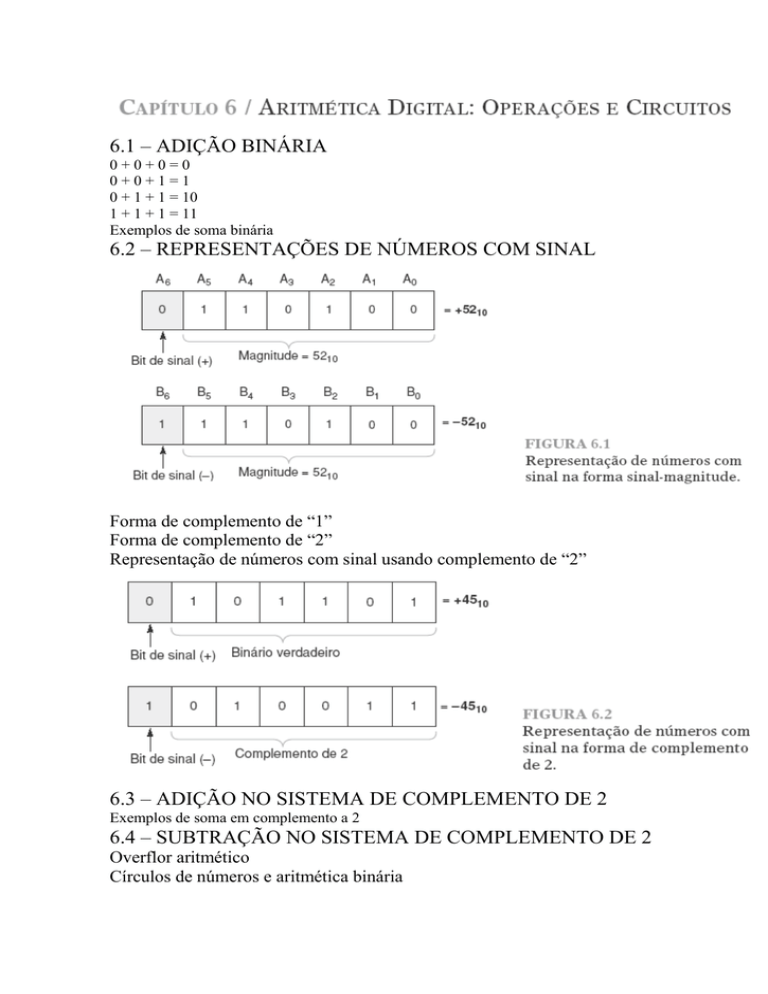

6.2 – REPRESENTAÇÕES DE NÚMEROS COM SINAL

Forma de complemento de “1”

Forma de complemento de “2”

Representação de números com sinal usando complemento de “2”

6.3 – ADIÇÃO NO SISTEMA DE COMPLEMENTO DE 2

Exemplos de soma em complemento a 2

6.4 – SUBTRAÇÃO NO SISTEMA DE COMPLEMENTO DE 2

Overflor aritmético

Círculos de números e aritmética binária

6.5 – MULTIPLICAÇÃO DE NÚMEROS BINÁRIOS

6.6 – DIVISÃO BINÁRIA (NÃO VISTA EM ELEO515 – CIRCUITOS

LÓGICOS)

6.7 – ADIÇÃO BCD ( Binary Coded Decimal )

Capítulo 2 – 2.4 – CÓDIGO BCD

Soma menor ou igual a 9

Soma maior que 9

Exemplos

6.8 – ARITMÉTICA HEXADECIMAL

Exemplos

Subtração hexadecimal

6.9 – CIRCUITOS ARITMÉTICOS (vista à frente )

Unidade Lógica e Aritmética (ALU)

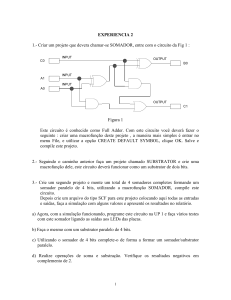

6.10 – SOMADOR BINÁRIO PARALELO

6.11 – PROJETO DE UM SOMADOR COMPLETO

S = A’B’Cin + A’BCin’+ AB’Cin’ +ABCin

S = A’(B’Cin + BCin’) + A(B’Cin’ + BCin)

S = A’ ( B Θ Cin ) + A ( B Θ Cin )’

Se fizermos X = B Θ Cin, a expressão poderá ser escrita como segue:

S = A’ X + A X’ = A Θ X

S = A Θ [ B Θ Cin ]

Cout = B Cin + A Cin + A B

6.12 – SOMADOR PARALELO COMPLETO COM

REGISTRADORES

6.13 – PROPAGAÇÃO DO CARRY

6.14 – SOMADOR PARALELO EM CIRCUITO INTEGRADO

Conexão em cascata de somadores paralelos

6.15 – SISTEMA DE COMPLEMENTO DE 2

Adição e subtração combinadas

Figura 6.14 – Somador/subtrator paralelo usando o sistema de

complemento de 2.

6.16 – CIRCUITOS INTEGRADOS ALU

A ALU 74LS328/HC328

Expandindo a ALU

6.17 – ESTUDO DE CASO NA ANÁLISE DE DEFEITOS

(NÃO VISTO EM ELE0515 - CIRCUITOS LÓGICOS)

6.18 – USANDO FUNÇÕES DE BIBLIOTECA TTL NO

ALTERA

(NÃO VISTO EM ELE0515 - CIRCUITOS LÓGICOS)

6.19 – OPERAÇÕES LÓGICAS EM MATRIZES DE BITS

ENTITY bitwise_and IS

PORT ( d, g : IN BIT_VECTOR (3 DOWNTO 0);

Y : OUT BIT_VECTOR (3 DOWNTO 0));

END bitwise_and;

ARCHITECTURE a OF bitwise_and IS

BEGIN

y <= a AND b;

END a;

Obs.

y3 = a3 AND b3

y2 = a2 AND b2

y1 = a1 AND b1

y0 = a0 AND b0

6.20 – SOMADORES EM HDL

FIGURA 6.19 Somador paralelo de quatro bits.

SOMADOR DE QUATRO BITS EM VHDL

6.21 – EXPANDINDO A CAPACIDADE EM BITS DE UM

CIRCUITO

Constantes são simplesmente números fixos representados por um nome ( símbolo ).

Se podemos definir um símbolo no topo do código fonte ao qual é atribuído o valor para

o número total de bits e então usar esse símbolo ao longo de todo o código, é muito

mais fácil modificar o circuito.

SOMADOR/SUBTRATOR EM VHDL

As constantes precisam ser incluídas em um PACKAGE

Comando GENERATE em VHDL – NÃO VISTO EM ELE0515 - CIRCUITOS

LÓGICOS

O comando GENERATE permite-nos repetir uma instanciação de um componente n

vezes, aumentando o número de índice em 1 para cada instância até n

Na linha 27 da Figura 6.26, a palavra chave GENERATE é usada em um loop iterativo (

loop FOR), o que significa que um conjunto de ações descritiva (PORT MAP) será

repetido um certo número de vezes.