Universidade Federal de Itajubá

IESTI - Instituto de Engenharia de Sistemas e Tecnologia da Informação

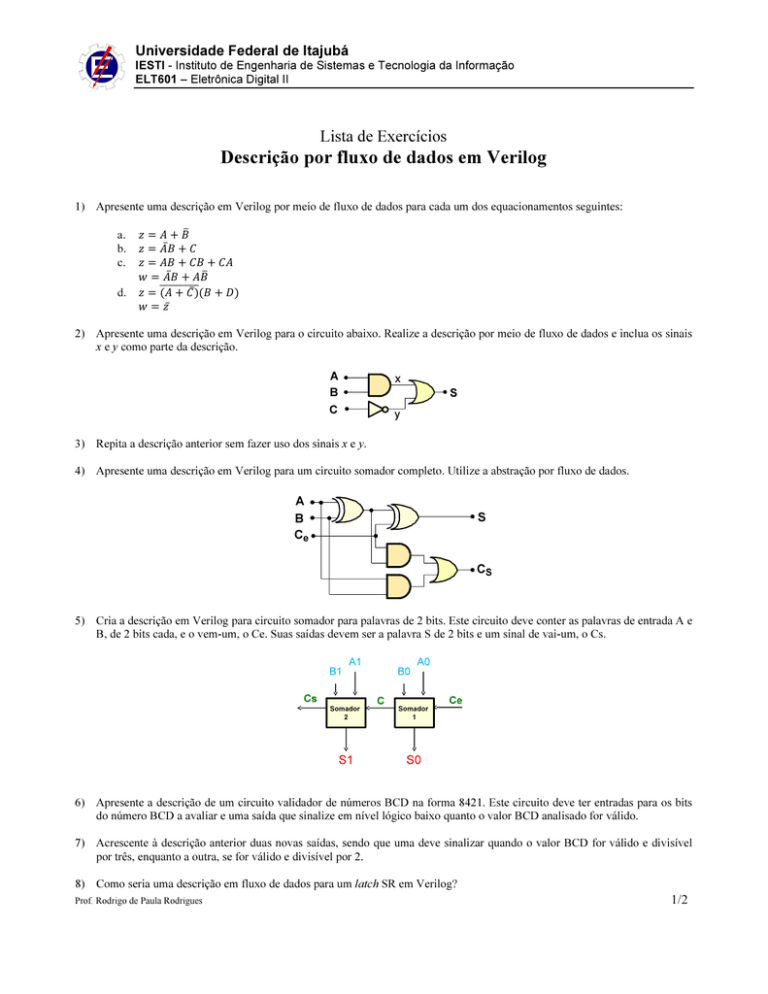

ELT601 – Eletrônica Digital II

Lista de Exercícios

Descrição por fluxo de dados em Verilog

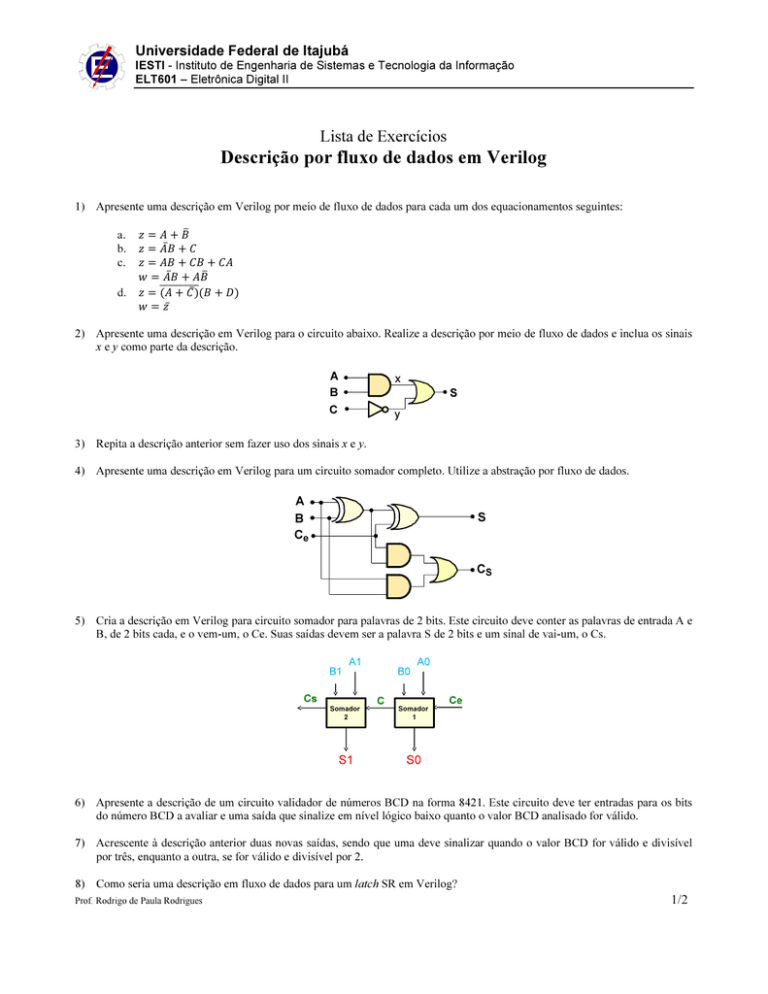

1) Apresente uma descrição em Verilog por meio de fluxo de dados para cada um dos equacionamentos seguintes:

a.

b.

c.

d.

= + = ̅ + = + + = ̅ + = ( + ̅ )( + )

= ̅

2) Apresente uma descrição em Verilog para o circuito abaixo. Realize a descrição por meio de fluxo de dados e inclua os sinais

x e y como parte da descrição.

A

B

C

x

S

y

3) Repita a descrição anterior sem fazer uso dos sinais x e y.

4) Apresente uma descrição em Verilog para um circuito somador completo. Utilize a abstração por fluxo de dados.

A

B

Ce

S

CS

5) Cria a descrição em Verilog para circuito somador para palavras de 2 bits. Este circuito deve conter as palavras de entrada A e

B, de 2 bits cada, e o vem-um, o Ce. Suas saídas devem ser a palavra S de 2 bits e um sinal de vai-um, o Cs.

A1

A0

B1

Cs

B0

Ce

C

Somador

2

Somador

1

S1

S0

6) Apresente a descrição de um circuito validador de números BCD na forma 8421. Este circuito deve ter entradas para os bits

do número BCD a avaliar e uma saída que sinalize em nível lógico baixo quanto o valor BCD analisado for válido.

7) Acrescente à descrição anterior duas novas saídas, sendo que uma deve sinalizar quando o valor BCD for válido e divisível

por três, enquanto a outra, se for válido e divisível por 2.

8) Como seria uma descrição em fluxo de dados para um latch SR em Verilog?

Prof. Rodrigo de Paula Rodrigues

1/2

9) Apresente a descrição de um circuito que receba um número binário de 2 bits e então gere o complemento de dois deste

número.

10) Apresente uma descrição em Verilog de um circuito que receba dois números binários de 3 bits cada e então coloque em sua

saída o maior número entre os recebidos.

11) Abaixo é apresentado um circuito deslocador de dados. Levante sua forma de operação e o implemente por meio de uma

descrição por fluxo de dados em Verilog. As entradas D e as saídas S devem ser declaradas como vetores.

Prof. Rodrigo de Paula Rodrigues

2/2