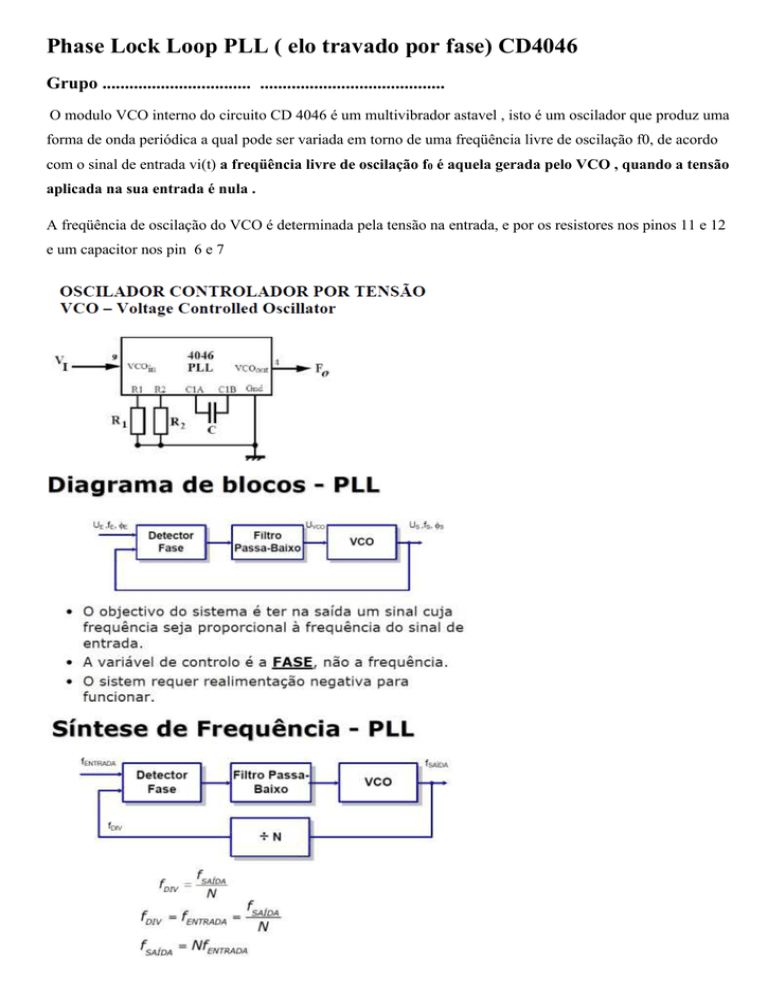

Phase Lock Loop PLL ( elo travado por fase) CD4046

Grupo ................................. .........................................

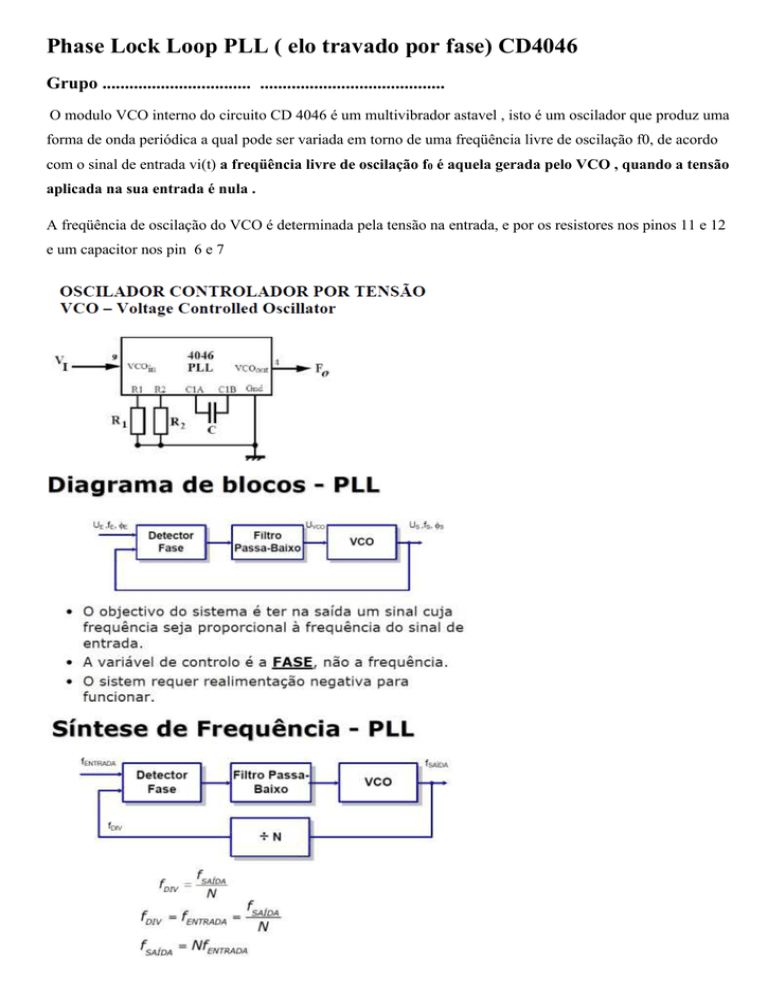

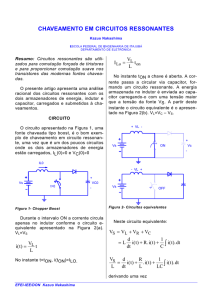

O modulo VCO interno do circuito CD 4046 é um multivibrador astavel , isto é um oscilador que produz uma

forma de onda periódica a qual pode ser variada em torno de uma freqüência livre de oscilação f0, de acordo

com o sinal de entrada vi(t) a freqüência livre de oscilação f0 é aquela gerada pelo VCO , quando a tensão

aplicada na sua entrada é nula .

A freqüência de oscilação do VCO é determinada pela tensão na entrada, e por os resistores nos pinos 11 e 12

e um capacitor nos pin 6 e 7

Experiencia I Modulador de FM

O Vco se constitui no circuito básico na cosntrução de um PLL. Neste experimento analisaremos apenas o

funcionamento deste circuito como modulador FM

+VCC

+VCC

14

3

4

6

7

11

12

5

C6

10n

R28

10k

0

SIG_INDEMO_OUT

COMP_IN

VCO_OUT

C1 COMP1_OUT

C2 COMP2_OUT

R1

PH_PULSE

R2

VCO_IN

INH

VSS*

0

0

10

2

13

1

9

R35

1k

V

0

R29

100k

CD4046

8

R33

100k

0

ZENER

VDD*

R38

10k

15

U3

16

R32

1k

C7

100n

0

0

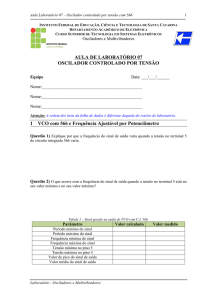

Experiencia I

1.- Com pin 9 a terra indique as formas de onda

nos pins 2,13,1,4,3. (2ptos)

2.- Obtenha a frequencia livre f0 para uma entrada

Com :

nula em pin9 (1pto)

R1= 10K

3.- Obtenha a frequencia maxima do VCO com pin

R2=100K

9 a +VCC (1pto)

C1=1nF

3.-Obtenha um a sinal FM com uma senoide de

Potenciômetro de 10k ou 100k

60Hz com off set de 5V em pin 9 (1pto)

Determine a freqüência livre de oscilação f0

Experiência II

Ensaiar e analisar o funcionamento do PLL 4046 verificar a obtenção do sincronismo e sua aplicação como

sintetizador de freqüências

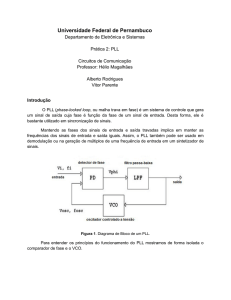

Esta experiência se divide em duas partes. A primeira consiste na montagem do PLL na situação descrita

pela figura 1, onde o VCO do PLL é diretamente conectado ao detector de fase. Nesta condição o PLL (o

VCO) tentará se sincronizar com a freqüência externa aplicada na sua entrada (pino 14).

Na segunda parte, é introduzido um contador divisor por 100 entre o VCO e o circuito comparador de fase.

Neste caso, como o PLL tentará se sincronizar com uma freqüência dividida por 100, o VCO irá então oscilar

em uma freqüência 100 vezes maior que a freqüência de entrada. Temos assim um sintetizador de freqüências.

+VCC

+VCC

14

3

4

6

7

11

12

5

C6

10n

R28

10k

0

SIG_INDEMO_OUT

COMP_IN

VCO_OUT

C1 COMP1_OUT

C2 COMP2_OUT

R1

PH_PULSE

R2

VCO_IN

INH

VSS*

0

8

R33

100k

0

ZENER

VDD*

R38

10k

15

U3

16

R32

1k

0

10

R35

1k

2

13

1

9

V

0

R29

100k

CD4046

C7

100n

0

0

Configuração 1:

a) Montar o PLL no circuito da figura 1 - configuração (1), com os valores: R1=10k, R2=100kK,

R3=100k, R4=100K, C1=1nF, C2=100nF (poliester).

b) Aplicar a alimentação de 10Vcc ao circuito.

Obs. Nunca aplique nenhum sinal à entrada dos CIs CMOS antes de ligar a alimentação a eles.

c) Fora do circuito, ajustar o gerador de sinais em onda quadrada, na freqüência de 10 KHz a 100KHz,

para 5V pico a pico (real, medido no osciloscópio). Inserir um offset para deslocar o sinal para cima,

de maneira a fazer com que o sinal varie efetivamente entre 0V e 5V.

d) Aplicar o gerador de sinais previamente ajustado na entrada do PLL (pino 14). Conectar o canal 1 do

osciloscópio no pino 14 e o canal 2 na saída do VCO (pino 4). Sincronizar a varredura do osciloscópio

pelo sinal do canal 1. Verificar o que ocorre com a freqüência do sinal no canal 2. Variar a freqüência

do sinal de entrada (pino 14) para valores maiores. Verificar em que freqüência começa a ocorrer o

sincronismo. Verificar até que freqüência ocorrerá o sincronismo. Medir a faixa de captura e a faixa

de retenção.com puntera CH-1 no sinal de entrada pin 14 e ch-2 no pin 3 ou 4

Configuração 2:

a) Montar o circuito divisor por 100, utilizando o CI 4518, conforme o circuito da figura 2, conectado ao

PLL, conforme o circuito da figura 1 - configuração (2).

b) Aplicar o sinal do gerador de sinais previamente ajusta de um 1KHz , na entrada do PLL (pino 14).

Conectar o canal 1 do osciloscópio no pino 14 e o canal 2 na saída do VCO (pino 4). Verificar o que

ocorre com a freqüência do sinal no canal 2. Aplicar o canal 2 do osciloscópio ao pino 3 do PLL

(segunda entrada do comparador de fase). Verificar o que ocorre com a freqüência do sinal no canal 2.

c) Retornar o canal 2 do osciloscópio à saída do VCO (pino 4). Variar a freqüência do sinal na entrada

do PLL (pino 14) e verificar o que ocorre com a freqüência do VCO.

Material

1/CD4046

1/Cmos 45 18

1/10k

2/ 100k

1/1nF Cap

1/100nF

Relatório

1-Faça uma simulação e apresente as formas de onda das situações descritas da parte experimental I do item 3 (2pto)

𝑓

−𝑓𝑚𝑖𝑛

2.- Determine a característica linear do VCO K =𝑉𝑚𝑎𝑥−𝑣

𝑑𝑑

0𝑚𝑖𝑛

(1pto)

3.- Faça a simulação e das formas de onda nos pin 14-2-13-1-9-3 para uma onda quadrada de 1Khz com e sem divisor

de freqüência (2ptos)