Universidade Federal de Pernambuco

Departamento de Eletrônica e Sistemas

Prática 2: PLL

Circuitos de Comunicação

Professor: Hélio Magalhães

Alberto Rodrigues

Vitor Parente

Introdução

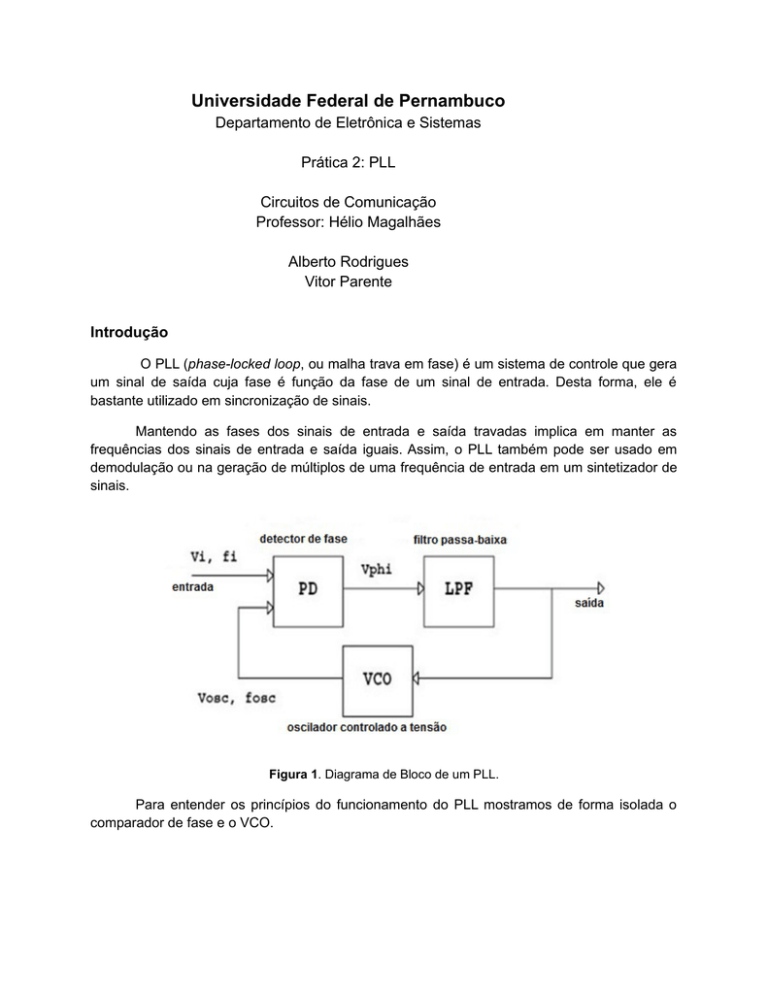

O PLL (phase-locked loop, ou malha trava em fase) é um sistema de controle que gera

um sinal de saída cuja fase é função da fase de um sinal de entrada. Desta forma, ele é

bastante utilizado em sincronização de sinais.

Mantendo as fases dos sinais de entrada e saída travadas implica em manter as

frequências dos sinais de entrada e saída iguais. Assim, o PLL também pode ser usado em

demodulação ou na geração de múltiplos de uma frequência de entrada em um sintetizador de

sinais.

Figura 1. Diagrama de Bloco de um PLL.

Para entender os princípios do funcionamento do PLL mostramos de forma isolada o

comparador de fase e o VCO.

O comparador de fase é um dispositivo de duas entradas e uma única saída: se na

entrada são aplicados sinais de mesma frequência nominal, porém não sincronizados, é gerada

uma tensão de saída que depende da diferença de fase entre as entradas. Procura–se obter

uma tensão proporcional a esta diferença de fase

Figura 2. Comparador de fase.

Da Figura 2, a diferença de fase é definida como ψ(t):= θ1(t)- θ2(t).

Após o multiplicador temos:

Após o filtro:

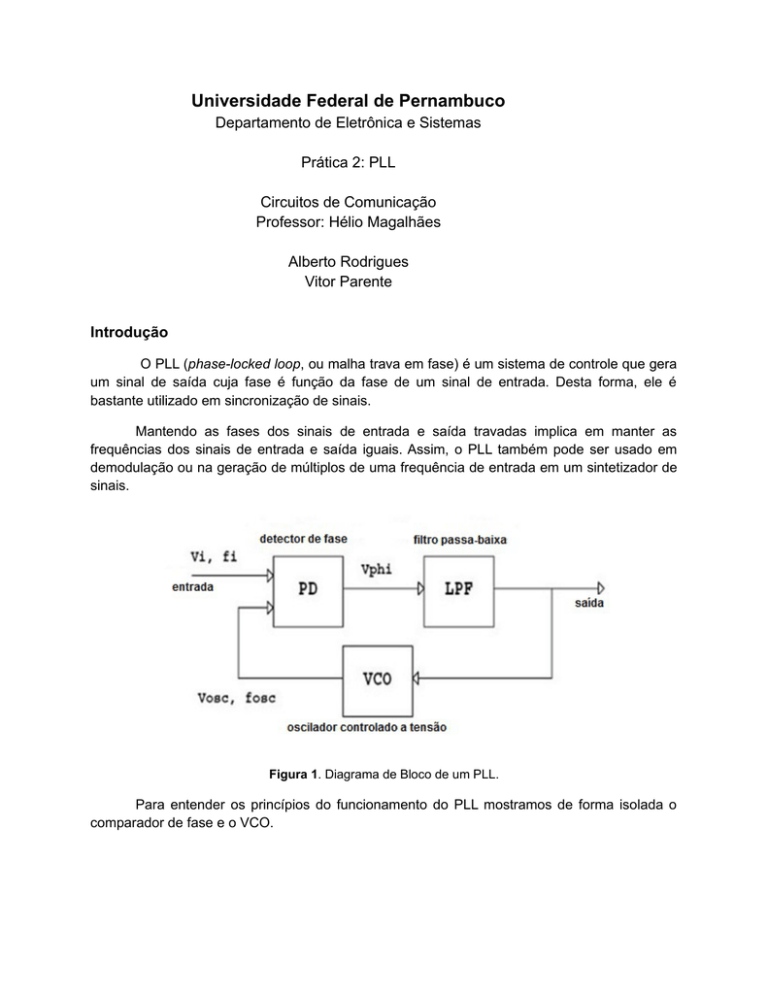

O oscilador Controlado à tensão (VCO) é um oscilador cuja frequência de oscilação é

determinada por uma tensão de controle a ele aplicado. Qualquer modulador FM serve como

VCO, sendo que na pratica o método direto é em geral utilizado.

A função do VCO é basicamente gerar uma variação na frequência do sinal da

portadora (frequência livre do VCO:= W0) de acordo com a variação da tensão do sinal da voz

(Sinal de entrada do VCO).

O VCO requer um capacitor C1 externo e um ou dois resistores externos (R1 ou R1 e

R2). O resistor R1 e o capacitor C1 determinam a faixa de frequência do VCO e o resistor R2

possibilita o VCO ter uma frequência offset se necessário.

Figura 3. Bloco do VCO.

Aplicações:

- modulação e demodulação FM;

- síntese e multiplicação de frequência;

- discriminador de frequência;

- sincronização de dados;

- conversão tensão-frequência;

- FSK-Modems

- transmissão digital em linhas telefônicas.

Procedimento Experimental

O circuito de um PLL em ~70 kHz representado pelo esquemático da Figura 1 foi

montado na protoboard, como mostrado na Figura 2.

Figura 4. Esquemático do circuito do PLL.

Figura 5. Circuito montado na protoboard.

Testamos o circuito conectando um osciloscópio à sua saída (B) e vimos uma onda

quadrada de frequência 72,36 kHz, como desejado. Conectamos, então, à sua entrada (A) um

gerador de onda quadrada com frequência de nível de alto de 5 V e nível de baixo de 0 V,

variamos sua frequência no intervalo de 50 kHz a 100 kHz e verificamos que o PLL permanecia

sincronizado. Assim, concluímos que o PLL estava funcionando corretamente.

Medição da faixa de retenção

Sem sinal de entrada, observamos o valor de frequencia f 0 da saída (B) na Figura 6 e

medimos com um multímetro a tensão de controle VE (D). Os valores foram:

f0 = 72,36kHz

VE = 2,16V

Figura 6. Saída do PLL sem sinal de entrada.

Conectando na entrada do PLL o sinal do gerador de onda quadrada, com frequência

de 72 kHz, nível de alto de 5 V e nível de baixo de 0 V, observamos a saída na Figura 7.

Observamos que o atraso entre os sinais é de 180º ou π/2 radianos, como esperado.

Figura 7. Saída do PLL(CH1) e sinal de entrada(CH2).

Com o PLL sincronizado, diminuindo a frequência do sinal de entrada, observamos

através do multímetro a diminuição da tensão de controle, até o PLL perder o sincronismo.

Neste momento, a tensão de controle aumenta repentinamente. Na Figura 8 temos o menor

valor de frequência para o qual ainda há sincronismo, enquanto na Figura 9 esse limite é

ultrapassado e o PLL perde a sincronia.

Figura 8. Limite inferior do PLL.

Figura 9. Abaixo do limite inferior do PLL.

Medimos os valores de tensão de controle e frequência:

f1 = 45 kHz

VE = 1,2 V

Repetindo o procedimento anterior aumentando a frequência do sinal de entrada,

observamos a frequência limite para a qual ainda existia sincronismo, representada na Figura

10.

Figura 10. Limite superior do PLL.

Na Figura 11 temos a frequência superior para o qual o PLL perde o sincronismo.

Figura 11. Acima do limite superior do PLL.

Medimos então os valores:

f4 = 117 kHz

VE = 3,5 V

Calcula-se assim a faixa de retenção, 2ΔfL, utilizando a equação:

2ΔfL = f4 – f1

2ΔfL = 117 kHz – 45 kHz

2ΔfL = 72 kHz

Medição da faixa de captura

Ajustando o gerador de onda quadrada para um valor de frequência inferior ao valor de

f1 e em seguida aumentando o valor de frequência até que ocorra uma repentina redução na

tensão de controle do VCO, conseguimos os valores:

f2 = 45 kHz

VE = 1,2 V

Repetindo o procedimento anterior para a frequência superior, obtivemos:

f3 = 117 kHz

VE = 3,5 V

Calculamos a faixa total de captura, 2Δfc, utilizando a equação:

2Δfc = f3 – f2

2Δfc = 117 kHz – 45 kHz

2Δfc = 72 kHz

Substituímos o capacitor de 1,2 nF do filtro de atraso por um filtro de atraso-avanço,

constituído por um capacitor de 18 nF em série com um resistor de 1,2 kΩ. Repetindo as

medições para a faixa de captura, medimos para a frequência inferior:

f2 = 55 kHz

VE = 1,48 V

Para a frequência superior:

f3 = 107 kHz

VE = 3,21 V

E assim, calculamos novamente o valor da faixa total de captura:

2Δfc = f3 – f2

2Δfc = 107 kHz – 55 kHz

2Δfc = 52 kHz

Observamos que esse valor é menor do que com o filtro de atraso.

Conclusão

Nesta prática, tivemos a oportunidade de montar um circuito de extrema importância em

diversas aplicações de telecomunicações, em particular na demodulação FM, multiplicação de

frequências, sincronização entre relógios e discriminação de frequências. Entendemos como o

circuito do PLL é projetado em função de seus parâmetros e especificações, e pudemos

estudar as limitações de operação do circuito.

Referências

[1] SANTOS, E. J. P. Eletrônica Analógica Integrada e Aplicada. Editora Livraria da

Física, São Paulo, 2011.

[2] OLIVEIRA, H. M. Engenharia de Telecomunicações. 1ª Ed. Recife, 2012.

![1. [5] Um circuito integrado precisa de uma tensão de alimentação](http://s1.studylibpt.com/store/data/000892095_1-927da8bea174b016f37ec8deb83e76f0-300x300.png)