LABORATÓRIO DE ELETRÔNICA BÁSICA I – EE531

QUARTA EXPERIÊNCIA

ALUNOS:

Douglas Pagani Pereira

Kauê Tebaldi Mirada

Otavio Mateus Bernardi

RA 090954

RA 097650

RA 097650

Turma W

Turma W

Turma W

Data: 11/06/2012

1.

RESULTADOS DO EXERCÍCIO PREPARATÓRIO DA QUARTA

EXPERIÊNCIA

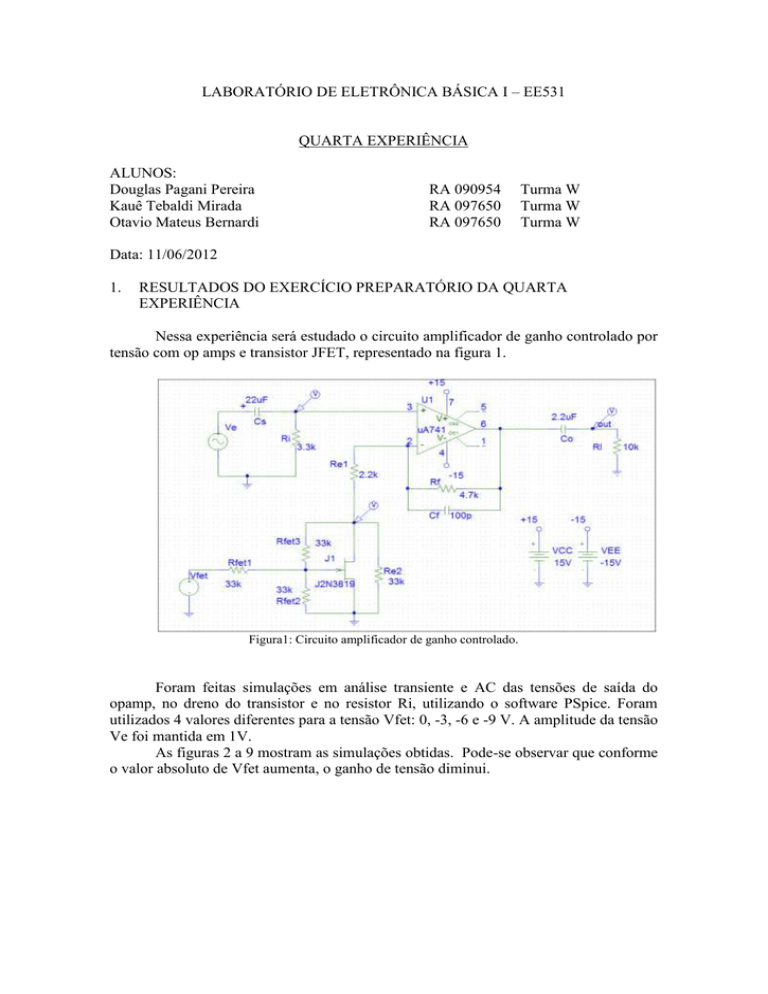

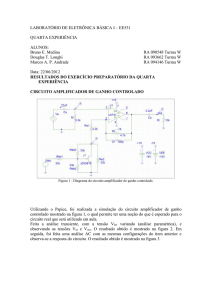

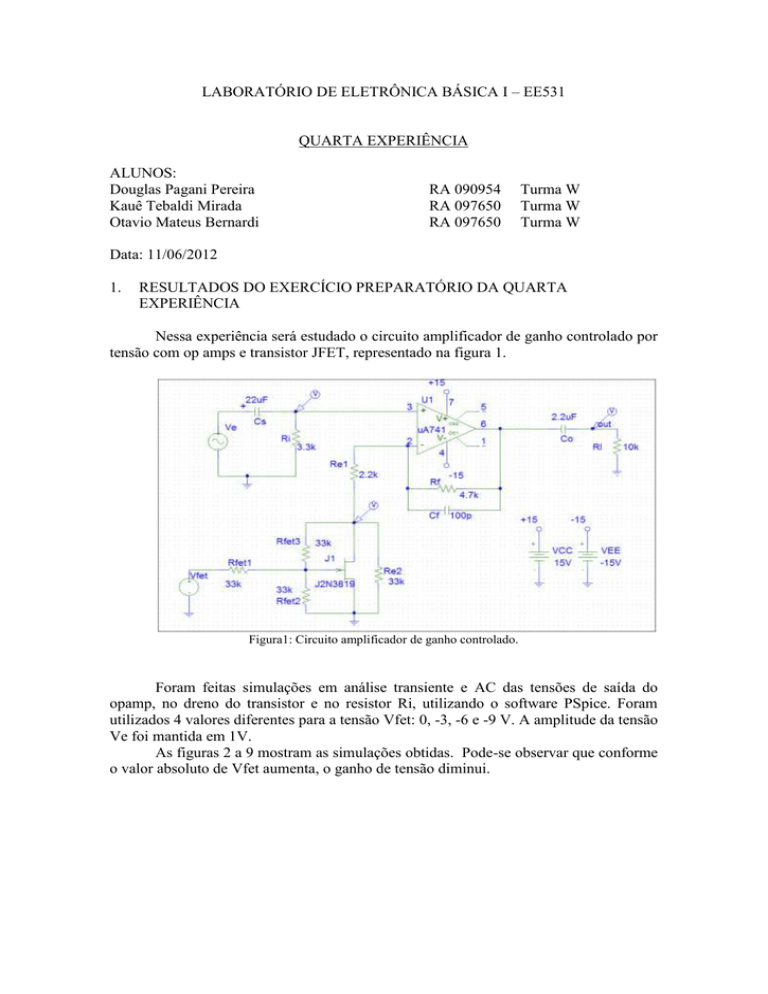

Nessa experiência será estudado o circuito amplificador de ganho controlado por

tensão com op amps e transistor JFET, representado na figura 1.

Figura1: Circuito amplificador de ganho controlado.

Foram feitas simulações em análise transiente e AC das tensões de saída do

opamp, no dreno do transistor e no resistor Ri, utilizando o software PSpice. Foram

utilizados 4 valores diferentes para a tensão Vfet: 0, -3, -6 e -9 V. A amplitude da tensão

Ve foi mantida em 1V.

As figuras 2 a 9 mostram as simulações obtidas. Pode-se observar que conforme

o valor absoluto de Vfet aumenta, o ganho de tensão diminui.

Figura 2: Análise Transiente para Vef = 0.

Figura 3: Análise AC para Vef = 0.

Figura 4: Análise Transiente para Vef = -3 V.

Figura 5: Análise AC para Vef = -3 V.

Figura 6: Análise Transiente para Vef = -6 V.

Figura 7: Análise AC para Vef = -6 V.

Figura 8: Análise Transiente para Vef = -9 V.

Figura 9: Análise AC para Vef = -9 V.

2.

RELATÓRIO DA QUARTA EXPERIÊNCIA

2.1 INTRODUÇÃO

Neste relatório será analisado o controlador de ganho do amplificador e um

retificador e detector de envoltória.

Mantendo a frequência fixa e alterando a diferença de potencial podemos observar

como o ganho no amplificador se comporta com o aumento da ddp e também como o

retificador funciona para altas e baixas entradas.

Além das varreduras, utilizou-se também para análise as imagens de onda retiradas

do osciloscópio, através destas imagens é possível observar um pouco mais de como o

sinal se comporta ao passar pelo amplificador e pelo retificador e observar as alterações

causadas pelo ganho e a limitação de sinais muito altos.

2.2 CIRCUITO AMPLIFICADOR DE GANHO CONTROLADO

Para este experimento estudou-se o funcionamento de um amplificador de ganho

controlado construído a partir do uso de transistores JFET. Um circuito como esse tem

como objetivo impedir que o som de saída de um amplificador se torne muito forte em

alguns momentos, gerando o efeito de “quebrar o som” que ocorre em altas distorções

ou muito fraco, a ponto de não ser ouvido.

O funcionamento do circuito se resume a alterar o ganho dado pelo amplificador

ao sinal de entrada de acordo sua intensidade, ou seja, para sinais muito fortes o circuito

reduz o ganho enquanto para sinais fracos o circuito amplia o ganho do amplificador.

Este circuito de ganho controlado permite que evitemos distorções do sinal de

entrada devido a um pico elevado de tensão, assim evitando a saturação do

amplificador. Para isto será usado um transistor JFET que opera como se fosse um

resistor variável não linear entre a fonte e o dreno.

O ganho é dado por:

G = 1 + 4,7k / (2,2k + Rn)

Onde Rn é a resistência variável em função da tensão no JFET.

2.2.1 Resultados Experimentais

Com o jumper, foi feita a varredura em tensão com um sinal de 1Khz,

apresentada na Figura 1 abaixo.

Figura 10: Varredura em Tensão para um sinal de 1kHz – Com Jumper

Pela análise do gráfico, verifica-se que o ganho gira em torno de 3, conforme era

esperado.

Sem o jumper, foi feita a Varredura 2 abaixo. Quando o circuito está sem

jumper, ou seja, a tensão Vfet no gate do JFET é variável, então a resistência entre o

dreno e a fonte do transistor será variável e não-linear. Com o aumento da tensão, a

resistência entre dreno e fonte aumentará, como podemos observar no comportamento

decrescente do gráfico acima e portanto o ganho diminui.

Figura 11: Varredura em Tensão para um sinal de 1kHz – Sem Jumper

Na figura 12, está representada uma forma de onda obtida com o ganho sendo

controlado. Podemos ver na forma de onda que o amplificador segura o ganho máximo.

A semi onda negativa tem amplitude maior que a semi onda positiva.

Figura 12: Amplificação do sinal de entrada

2.3 CIRCUITO RETIFICADOR E DETECTOR DE ENVOLTÓRIA

Quando a tensão de entrada é positiva a corrente não irá fluir pelo diodo D1 e

estando os dois terminais do amplificador aterrados, o circuito emitirá um sinal de saída

equivalente ao sinal de entrada invertido. Já quando o sinal de entrada é negativo, a

corrente que irá fluir por D1 fará com que o diodo D2 seja polarizado, quando isso

ocorre, a tensão de saída será anulada, desta forma, o sinal será retido para entradas de

tensão negativa.

O funcionamento como detector de envoltório é realizado graças ao capacitor

acoplado ao retificador. Quando o sinal passa pelo retificador ele irá carregar

rapidamente o capacitor, porém quando o sinal decai, o capacitor irá descarregar mais

lentamente que o sinal, impedindo uma queda muito brusca da onda.

2.2.1 Simulações e Resultados Experimentais

Para que fosse possível ver a retificação de meia onda, aplicamos um sinal

senoidal na entrada e verificamos o sinal de saída no ponto do circuito acima do

capacitor C13. Fizemos uma análise para baixa freqüência (10Hz) e alta freqüência

(5kHz).

Abaixo estão as formas de onda obtidas com auxílio do osciloscópio.

Figura 13: Retificação do sinal de entrada para baixas frequências.

Figura 14: Retificação do sinal de entrada para altas frequências.

Para baixas frequencias observa-se que o sinal de entrada (em verde) é retificado

e invertido (curva amarela), conforme esperado.

Para alta freqüência (5kHz) o capacitor não tem tempo suficiente para manter-se

carregado. Devido a isto, a forma de onda se assemelha a uma reta, ou seja, o sinal de

entrada é retificado.Este sinal retificado é usado para variar a resistência entre fonte e

dreno do JFET, de forma a controlar o ganho do sinal.

Em seguida fizemos uma varredura em tensão para verificar a relação existente

entre o sinal de entrada e o sinal de saída do circuito retificador.

Obtivemos o seguinte gráfico para esta varredura:

Figura 15: Varredura em tensão para sinal verificado na saída do Retificador

Podemos ver que a tensão de saída do circuito retificador varia linearmente com

relação à tensão de entrada, pois o circuito apenas retifica o sinal.

2.4 CONCLUSÕES

Apesar de pequenas variações o ganho no amplificador controlado, explicitado na

primeira varredura, corresponde ao ganho no circuito com jumper teorico. Já na analise

do circuito retificador pudemos notar que com freqüências baixas o capacitor não tem

influencia no circuito fazendo com que a onda seja retificada e invertida. Já para altas

freqüências o circuito se comparta como um detector de envelope.

3.

NOTIFICAÇÃO DE PROBLEMAS COM O KIT UTILIZADO

Não foram observados problemas.