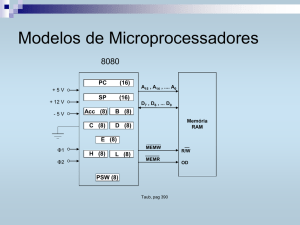

Microprocessadores

Família “x86” - Hardware do i8086

António M. Gonçalves Pinheiro

Departamento de Física

Universidade da Beira Interior

Covilhã - Portugal

[email protected]

Microprocessadores

Ligações do i8086

Sinais Comuns

Nome

AD15-AD0

Função

Barramento de

Endereços/Dados

A19/S6-A16/S3 Barramento de

Endereços/Estado

BHE/S7

BUS HIGH ENABLE/

Estado

MN/MX

Controlo Mínimo/Máximo

RD

Controlo de Leitura

TEST

Controlo de Espera de Teste

READY

Controlo de Estado de Espera

NMI

Non-Maskable Interrupt Rqst

INR

Interrupt Request

CLK

Relógio do Sistema

Vcc

+5 Volts

GND

Tensão de Referência

Tipo

3 Estados/

Bidireccional

3 Estados/Saída

3 Estados/Saída

Entrada

3 Estados/Saída

Entrada

Entrada

Entrada

Entrada

Entrada

Entrada

Entrada

GND

Vcc

AD14

AD15

AD13

A16/S3

AD12

A17/S4

AD11

A18/S5

AD10

A19/S6

AD9

BHE/S7

AD8

MN/MX

AD7

AD6

RD

CPU

8086

HOLD

RQ/GT0

HLDA

RQ/GT1

AD4

WR

LOCK

AD3

M/IO

S2

AD2

DT/R

S1

AD1

DEN

S0

AD0

ALE

QS0

NMI

INTA

QS1

INTR

TEST

AD5

CLK

READY

GND

RESET

Universidade da Beira Interior

Microprocessadores

Ligações do i8086

Sinais do Modo Mínimo (MN/MX=1)

Nome

HOLD

HLDA

WR

M/IO

DT/R

DEN

ALE

INTA

Função

Hold Request

Hold Acknowledgemnet

Controlo de Escrita

Controlo de Memória/IO

Transmissão/Recepção de dados

Data Enable

Address Latch Enable

Acknowledge de Interrupção

Tipo

Entrada

Saída

3 Estados/Saída

3 Estados/Saída

3 Estados/Saída

3 Estados/Saída

Saída

Saída

GND

Vcc

AD14

AD15

AD13

A16/S3

AD12

A17/S4

AD11

A18/S5

AD10

A19/S6

AD9

BHE/S7

AD8

MN/MX

AD7

AD6

RD

CPU

8086

HOLD

RQ/GT0

HLDA

RQ/GT1

AD4

WR

LOCK

AD3

M/IO

S2

AD2

DT/R

S1

AD1

DEN

S0

AD0

ALE

QS0

NMI

INTA

QS1

INTR

TEST

AD5

CLK

READY

GND

RESET

Universidade da Beira Interior

Microprocessadores

Ligações do i8086

Sinais do Modo Máximo (MN/MX=0)

Nome

Função

RQ/GT1, 0 Request/Grant de

Controlo de Barramento

LOCK

Controlo de Prioridade

do Barramento

S2-S0

Estado do Ciclo do Barramento

QS1-QS0 Estado da Fila de Instrucções

Tipo

Bidireccional

GND

Vcc

AD14

AD15

AD13

A16/S3

AD12

A17/S4

AD11

A18/S5

AD10

A19/S6

AD9

BHE/S7

AD8

MN/MX

AD7

3 Estados/Saída

3 Estados/Saída

Saída

AD6

RD

CPU

8086

HOLD

RQ/GT0

HLDA

RQ/GT1

AD4

WR

LOCK

AD3

M/IO

S2

AD2

DT/R

S1

AD1

DEN

S0

AD0

ALE

QS0

NMI

INTA

QS1

INTR

TEST

AD5

CLK

READY

GND

RESET

Universidade da Beira Interior

Microprocessadores

Ligações do i8086

Diagrama de Blocos do Modo Mínimo

INTR

Interface das

Interrupções

A0-A15

A16/S3-A19/S6

INTA

TEST

NMI

RESET

D0-D15

ALE

BHE/S7

M/IO

Interface da HOLD

DMA HLDA

DT/R

RD

Controlo de

Memória e

Entrada/Saída

WR

DEN

MN/MX

Barramento

de Dados e

Endereço

READY

Universidade da Beira Interior

Microprocessadores

Ligações do i8086

Sinais de Estado

S4

0

0

1

1

S3

0

1

0

1

Registo de Segmento

Extra

Stack

Código/Nenhum

Dados

S5 = IF (Flag de Interrupção)

S6=0

Modo Máximo

S2

0

0

0

0

1

1

1

1

S1

0

0

1

1

0

0

1

1

S0

0

1

0

1

0

1

0

1

Ciclo de CPU

Interrupt Acknowledge

Leitura de Porto

Escrita de Porto

Halt

Busca de Instrucção

Leitura de Memória

Escrita de Memória

Passivo

Universidade da Beira Interior

Comando

INTA

IORC

IOWC,AIOWC

MRDC

MRDC

MWTC,AMWC

Microprocessadores

Ligações do i8086

Acesso à Memória

BHE

A19-A1

FFFFF

FFFFD

A0

FFFFE

FFFFC

00005

00003

00001

00004

00002

00000

D15-D8

D7-D0

FFFFF

BHE

A19-A1

FFFFF

BHE

A19-A1

FFFFE

A0

BHE

X+3

X+1

FFFFE

A0

X+2

X

00005

00003

00001

00004

00002

00000

D15-D8

D7-D0

FFFFF

FFFFE

A0

X+1

X

X+3

X+1

00005

00003

00001

00004

00002

00000

00005

00003

00001

00004

00002

00000

D15-D8

D7-D0

D15-D8

D7-D0

Endereço Alinhado

A19-A1

Endereço Desalinhado

Universidade da Beira Interior

X+2

X

Microprocessadores

Ligações do i8086

Ciclos de Leitura e Escrita de Memória

Ciclo de BUS

T1

T2

Ciclo de BUS

T3

T4

CLK

A19/S6-A16/S3

BHE/S7

AD15-AD0

T1

T2

T3

T4

CLK

Endereço/BHE

Endereço

Estado

Dados

A19/S6-A16/S3

BHE/S7

AD15-AD0

ALE

ALE

M/IO

M/IO

RD

WR

DT/R

DT/R

DEN

DEN

Ciclo de Leitura de Memória

Endereço/BHE

Estado

Endereço

Dados

Ciclo de Escrita de Memória

Universidade da Beira Interior

Microprocessadores

Ligações do i8086

Ciclos de Leitura e Escrita de I/O

Ciclo de BUS

T1

T2

Ciclo de BUS

T3

T4

CLK

A19/S6-A16/S3

BHE/S7

AD15-AD0

T1

T2

T3

T4

CLK

Endereço/BHE

Endereço

Estado

Dados

A19/S6-A16/S3

BHE/S7

AD15-AD0

ALE

ALE

M/IO

M/IO

RD

WR

DT/R

DT/R

DEN

DEN

Ciclo de Leitura de Porto

Endereço/BHE

Estado

Endereço

Dados

Ciclo de Escrita de Porto

Universidade da Beira Interior

Microprocessadores

Ligações do i8086

Interrupções

End. Mem

3FE

3FC

Entrada Tbl Def. Vector

CS 255

Vector 255 Disponível ao Utilizador

IP 255

...

82

80

7E

7C

CS 32

IP 32

CS 31

IP 31

Vector 32

Disponível ao Utilizador

Vector 31

Reservado

Vector 5

Reservado

Vector 4

Overflow

Vector 3

Breakpoint

Vector 2

NMI

Vector 1

Single-Step

Vector 0

Divide Error

...

16

14

12

10

0E

0C

0A

08

06

04

02

00

CS 5

IP 5

CS 4

IP 4

CS 3

IP 3

CS 2

IP 2

CS 1

IP 1

CS 0

IP 0

Universidade da Beira Interior

Microprocessadores

Ligações do i8086

“Ciclo de Acknowledgment” de Interrupção

1 º Ciclo de BUS

T1

T2

2 º Ciclo de BUS

T3

T4

T1

T2

T3

CLK

ALE

LOCK

INTA

AD7-AD0

Tipo de Vector

Universidade da Beira Interior

T4