UNIVERSIDADE FEDERAL DO RIO GRANDE DO NORTE

CENTRO DE TECNOLOGIA

CURSO DE ENGENHARIA DE COMPUTAÇÃO

DISCIPLINA: Circuitos Lógicos Combinacionais

PROFESSOR: Pablo Javier Alsina

3O LISTA DE EXERCÍCIOS

1) Projete um circuito lógico combinacional que receba como entrada um número

binário de 3 bits e gere uma saída que é o quadrado do número.

2) Projete um subtrator rápido de 4 bits com “empresta-um” antecipado.

3) Projete uma ULA com as seguintes características:

-

Entradas: duas palavras de 4 bits (A3A2A1A0 e B3B2B1B0), saídas: uma palavra de 4 bits

(F3F2F1F0).

Entradas de seleção (S2S1S0), correspondente às funções A, A’, A.B, A+B, A mais B, A menos

B, A mais 1, A menos 1.

Entradas e saídas adicionais C0 (Carry de entrada), C4 (Carry de saída).

Saídas de STATUS (Z = resultado zero, N = resultado negativo, P = resultado positivo).

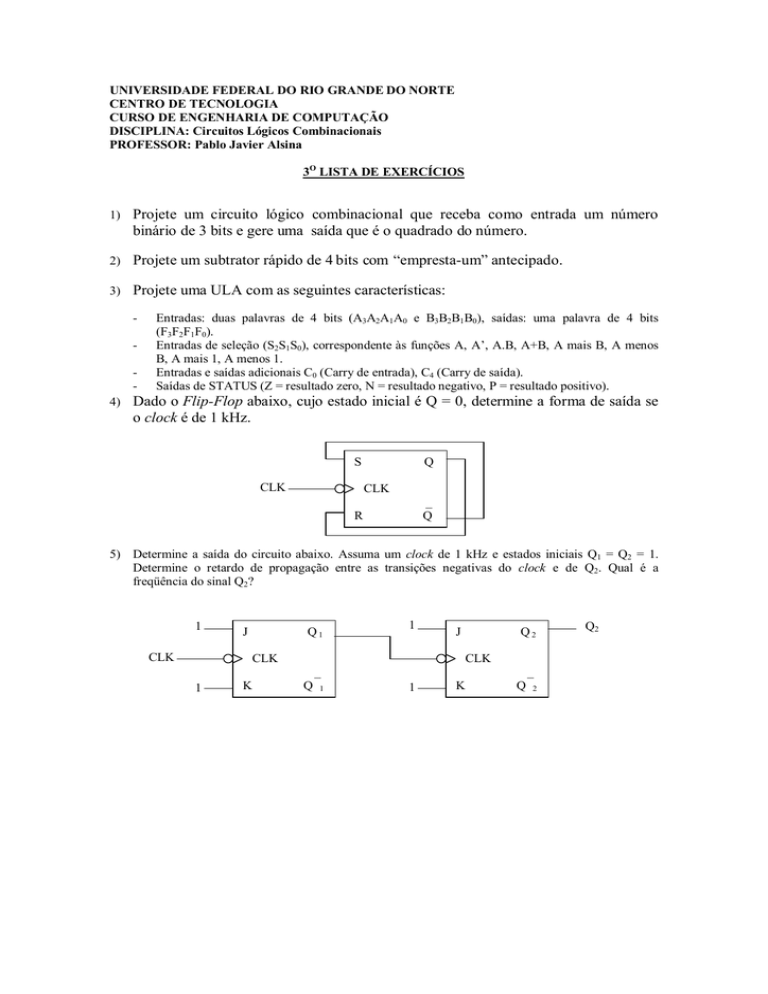

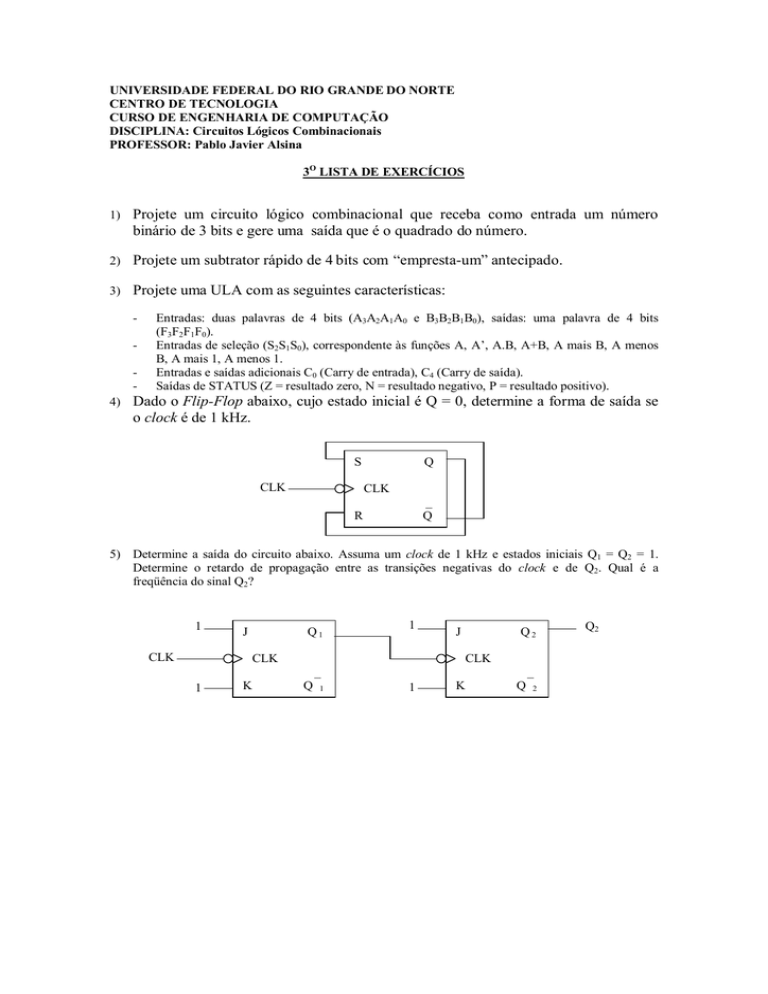

4) Dado o Flip-Flop abaixo, cujo estado inicial é Q = 0, determine a forma de saída se

o clock é de 1 kHz.

S

CLK

Q

CLK

_

Q

R

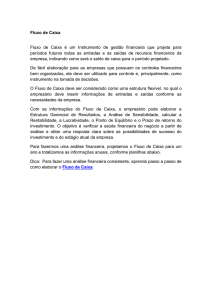

5) Determine a saída do circuito abaixo. Assuma um clock de 1 kHz e estados iniciais Q1 = Q2 = 1.

Determine o retardo de propagação entre as transições negativas do clock e de Q2. Qual é a

freqüência do sinal Q2?

1

J

CLK

Q1

1

J

CLK

Q2

CLK

_

1

K

Q

1

_

1

K

Q

2

Q2