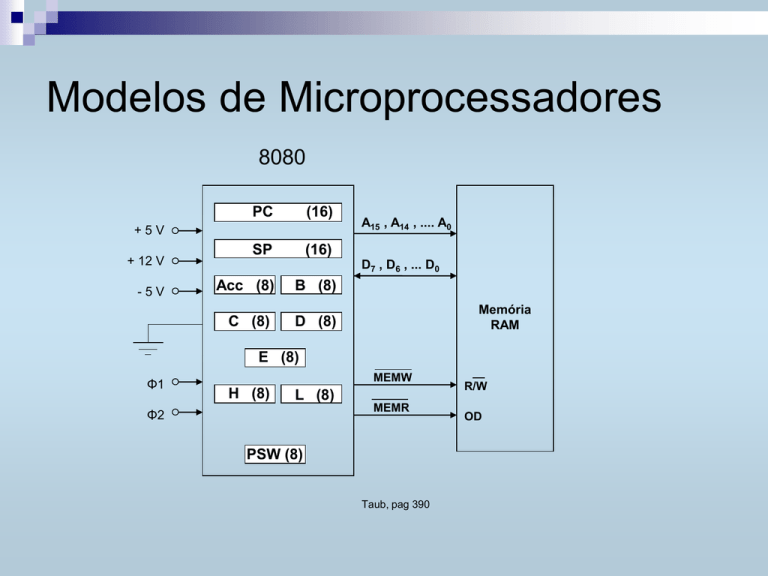

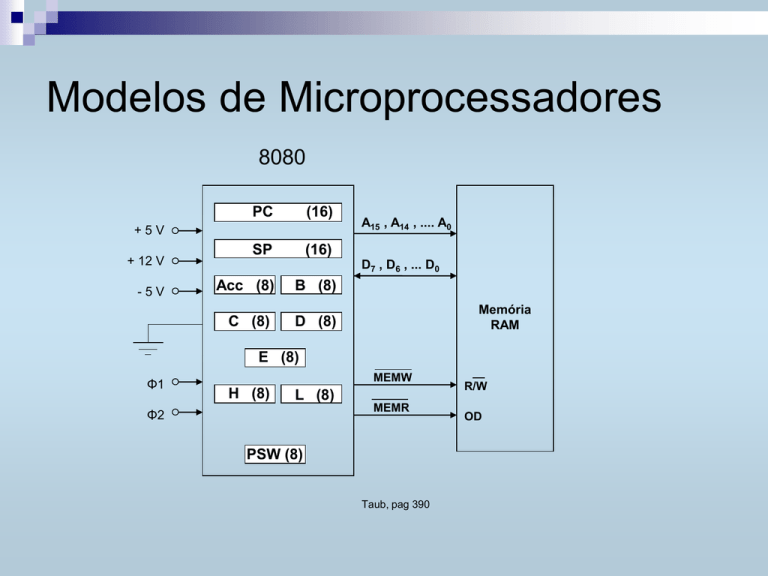

Modelos de Microprocessadores

8080

PC

(16)

SP

(16)

+5V

+ 12 V

-5V

A15 , A14 , .... A0

D7 , D6 , ... D0

Acc (8)

B (8)

C (8)

D (8)

Memória

RAM

E (8)

Φ1

MEMW

H (8)

L (8)

Φ2

MEMR

PSW (8)

Taub, pag 390

R/W

OD

Modelos de Microprocessadores

6800

+5V

Acc A (8)

A15 , A14 , .... A0

Acc B (8)

D7 , D6 , ... D0

PC

SP

(16)

Φ1

Φ2

Memória

RAM

(16)

R/W

Index Reg

(16)

R/W

OD

PSW (8)

Taub, pag 420

Modelos de Microprocessadores

Barramento externo

(dados, endereços, controle)

8086 / 8088

Lógica de controle

de barramento

Somador

CS

DS

SS

ES

IP

Unidade de

execução

Fila de

instruç

ões de

8/6

bytes

Unidade

de

Controle

AX

AH

BX

CX

DX

BH

CH

DH

AL

BL

CL

DL

SP

BP

DI

SI

Linhas

de

Controle

Barramento interno

Unidade de interface

de barramento

Registradores

temporários

ALU

Flags

Monteiro,

pag 375

Modelos de Microprocessadores

Barramentos

internos

Registradores de

uso Geral

Registradores de

segmento

Tabela

páginas

Deslocamento

Registradores

descritores

Cálculo

endereço

página

ALU

Cálculo

endereço

segmento

Unidade de

paginação

Multiplica

/ Divide

Unidade de

inteiros

Controle

de Ponto

Flutuante

Registradores de

Ponto

Flutuante

Unidade de

ponto flutuante

80486

Unidade

Controle de cache

do Cache

Cache

(8 kB)

Inter face

Barramentos:

Dados

.

de

Unidade de

Segmentação

Endereço

Barra Controle .

mento

Linhas

de

Controle

Memória

de

Controle

Prébusca

Decodificador

Unidade de Controle

Fila de

pré-busca

Unidade de

pré-busca

Modelos de Microprocessadores

Registradores do 80386, 80486 e do Pentium (lembrete)

16 bits

16 bits

AH (AX) AL

EAX

BH (BX) BL

EBX

CH (CX) CL

ECX

DH (DX) DL

EDX

ESI

EDI

EBP

ESP

ESP: Extended Stack pointer

EBP: Extended Base Pointer

EDI: Extended Destino (String)

ESI: Extended Source (origem; String)

CS

CS: Segmentação, Código (programa)

SS

DS: Segmentação, Dados

DS

ES: Segmentação, “Extra”

ES

FS: Segmentação, adicional

FS

GS: Segmentação, adicional

GS

SS: Segmentação, “Stack” (Pilha)

EIP

EIP: Extended Instruction Pointer = PC

EFLAG

EFLAG: Extended Flag

Modelos de Microprocessadores

Pentium

Cache de

código

Decisão de

predição

Buffer

Pre-fetch

Barramento

de dados

(64 bits)

Interface de

barramento

(64 bits)

ALU de

inteiros

ALU de

inteiros

Controle de

Ponto Flutuante

Soma

Produto

Registradores

gerais

Cache de

dados

Divisão

Zelenovsky, Mendonça, pag 83

Interfaceamento com barramento

8088 em “Modo Máximo”

Pinagem

IBM PC Bus

Gerador

relógio

8284A

OSC

CLK

RESET

CLK RESET

A19 .. A0

20

8088

D7 .. D0

8

INT

3

S0,S1,S2

Latch

74LS373

(3 x)

OE

A19 .. A0

Transcep

Barram.

74LS245

DIR DE

D7 .. D0

ALE

MEMR

Control.

Barram.

8288

MEMW

IOR

IOW

AEN

READY NMI

Control.

de

Interrup.

8259A

IO CH CKK

IO CH RDY

8

IRQ2 .. IRQ7

Control.

DMA

8237A

DRG1 .. DRG3

DACK0 .. DACK3

T/C

+5V -5V -12V -12V

GND

GND

A14

A13

A12

A11

A10

A9

A8

AD7

AD6

AD5

AD4

AD3

AD2

AD1

AD0

NMI

INTR

CLK

GND

s2

0

0

0

0

1

1

1

1

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

22

21

VCC

A15

A16/S3

A17/S4

A18/S5

A19/S6

BHE

MN/MX

RD

RQ/GT0

RQ/GT1

LOCK

S2

S1

S0

QS0

QS1

TEST

READY

RESET

s1 s0 Função

0 0 Interrupt acknowledge

0 1 I/O port read

1 0 I/O port write

1 1 Halt

0 0 Code access

0 1 Memory read

1 0 Memory write

1 1 Release bus