2.8 Paralelismo Temporal e Espacial

Acima do paralelismo no nível de bit, como aquele presente em uma ALU de

mais de um bit, temos o Paralelismo no Nível Instrução (Instruction Level

Paralelism – ILP). Existem dois tipos básicos de ILP: temporal e espacial.

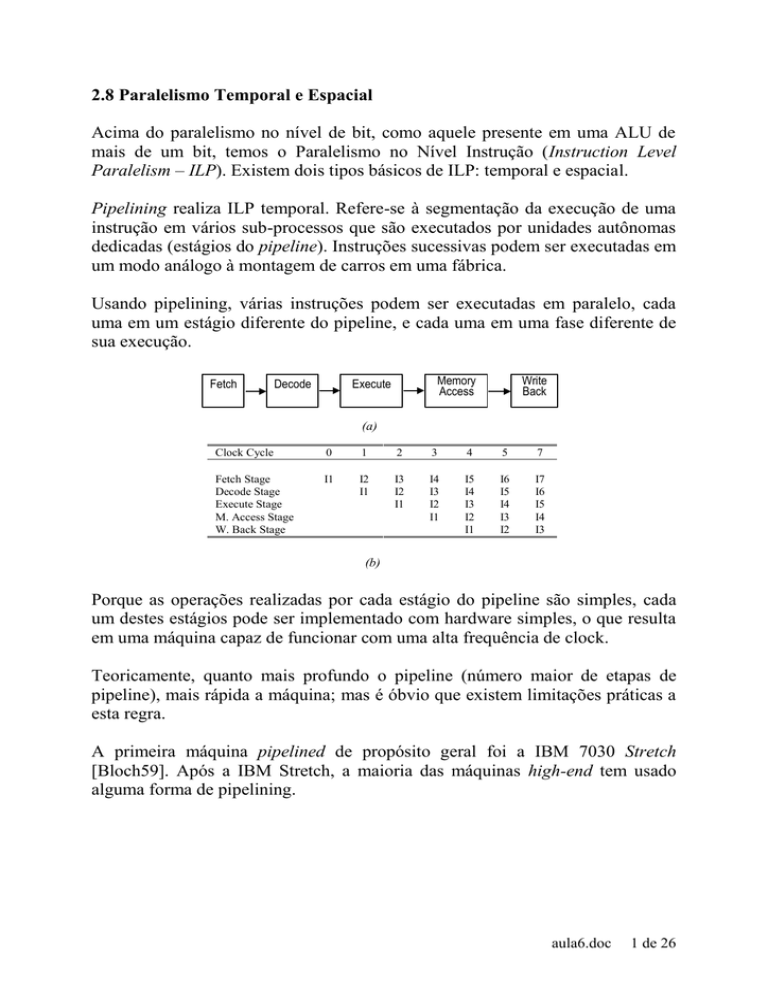

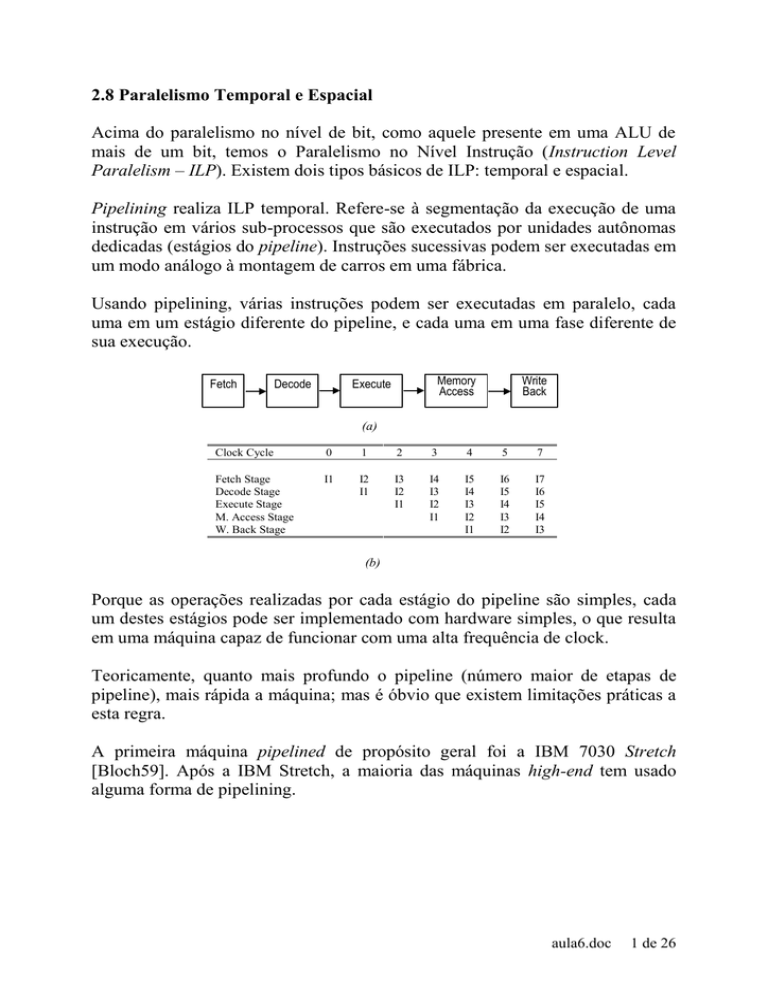

Pipelining realiza ILP temporal. Refere-se à segmentação da execução de uma

instrução em vários sub-processos que são executados por unidades autônomas

dedicadas (estágios do pipeline). Instruções sucessivas podem ser executadas em

um modo análogo à montagem de carros em uma fábrica.

Usando pipelining, várias instruções podem ser executadas em paralelo, cada

uma em um estágio diferente do pipeline, e cada uma em uma fase diferente de

sua execução.

Fetch

Decode

Memory

Access

Execute

Write

Back

(a)

Clock Cycle

0

1

2

3

4

5

7

Fetch Stage

Decode Stage

Execute Stage

M. Access Stage

W. Back Stage

I1

I2

I1

I3

I2

I1

I4

I3

I2

I1

I5

I4

I3

I2

I1

I6

I5

I4

I3

I2

I7

I6

I5

I4

I3

(b)

Porque as operações realizadas por cada estágio do pipeline são simples, cada

um destes estágios pode ser implementado com hardware simples, o que resulta

em uma máquina capaz de funcionar com uma alta frequência de clock.

Teoricamente, quanto mais profundo o pipeline (número maior de etapas de

pipeline), mais rápida a máquina; mas é óbvio que existem limitações práticas a

esta regra.

A primeira máquina pipelined de propósito geral foi a IBM 7030 Stretch

[Bloch59]. Após a IBM Stretch, a maioria das máquinas high-end tem usado

alguma forma de pipelining.

aula6.doc

1 de 26

ILP espacial é aquele presente em processadores com múltiplas unidades

funcionais. Refere-se à execução de mais de uma instrução simultaneamente em

diferentes unidades funcionais do processador.

Paralelismo temporal e espacial podem estar presentes ao mesmo tempo em uma

máquina. Na verdade, poucos anos após a IBM 7030 Stretch ter sido construída,

a CDC6600 foi produzida com pipelining e várias unidades funcionais que

podiam funcionar em paralelo.

Look-Ahead

Hardware

FU

Instruction Memory

Fetch

Decode Hardware

Decode

Dispatch Hardware

Dispatch

IW & Issue Hardware

Issue

FU

FU

FU

FU

Execute

Write Back

Result Buses

Data Memory

(b)

(a)

aula6.doc

2 de 26

2.9 Pipelining

A figura abaixo mostra uma versão simplificada de uma possível implementação

de um processador MIPS de 64 bits. Nesta implementação, todas as instruções

executam em um ciclo de clock.

Instruction

Fetch

Instr. Decode

Reg. Fetch

Execute

Addr. Calc

Adder

4

Next SEQ PC

Zero?

RS1

L

M

D

MUX

Data

Memory

ALU

Imm

MUX MUX

RD

Reg File

Memory

Address

RS2

Write

Back

MUX

Next PC

Memory

Access

Sign

Extend

WB Data

A ISA MIPS 64 possui um conjunto de instruções um pouco maior que a ISA

MIPS 32. Isso explica o controle do MUX que define o próximo valor de PC na

figura acima.

aula6.doc

3 de 26

Na figura abaixo á apresentado conjunto de instruções da MIPS 64.

aula6.doc

4 de 26

A arquitetura anterior pode ser implementada usando pipelining como abaixo.

Execute

Addr. Calc

Instr. Decode

Reg. Fetch

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

EX/MEM

ALU

MUX MUX

ID/EX

Imm

Reg File

IF/ID

Memory

Address

RS2

Write

Back

MUX

Next PC

Memory

Access

WB Data

Instruction

Fetch

Sign

Extend

RD

RD

RD

Com a implementação acima, a cada ciclo de clock, as instruções avançam de

um dos registradores em verde para o outro.

1. Inicialmente, no primeiro estágio, temos apenas o endereço da instrução

(Address) em PC.

2. No estágio seguinte, temos a instrução e seu endereço no registrador IF/ID

– este registrador demarca a saída do estágio de Fetch e a entrada do

estágio de Decode do pipeline.

3. No terceiro estágio, a instrução, seu endereço e os registradores que ela

endereça são escritos no registrador ID/EX - note que, mesmo que a

instrução não precise ler os registradores, ainda assim eles são lidos para

simplificar o hardware.

4. No quarto estágio, a operação que a instrução demandar da ALU é

realizada e:

a. Se a instrução for de desvio, o PC é atualizado e a instrução

terminada (é enviado um código “não faça nada” para o próximo

estágio).

b. Se a instrução for de outro tipo, ela e o resultado da operação

realizada pela ALU são transferidos para o próximo estágio.

5. No quinto estágio, se a instrução apenas envolver uma operação da ALU,

seu resultado é escrito no banco de registradores. Caso contrário, a

instrução é de acesso à memória e este acesso é feito. Caso a instrução

seja de leitura na memória, o dado lido é escrito no banco de registradores

aula6.doc

5 de 26

A Figura abaixo ajuda a visualizar melhor a evolução da execução das

instruções no pipeline. Na figura, a execução de uma sequencia de instruções

(no lado direito) pode ser analisada a cada ciclo de clock (colunas); isto é,

podemos visualizar onde cada instrução estará no pipeline a partir do ciclo onde

a primeira entra no pipeline (cycle 1). Quando o pipeline está cheio, 5 instruções

estão sendo executadas em paralelo.

Time (clock cycles)

O

r

d

e

r

Reg

DMem

Reg

DMem

Reg

ALU

Ifetch

DMem

ALU

Reg

Ifetch

ALU

I

n

s

t

r.

ALU

Cycle 1 Cycle 2 Cycle 3 Cycle 4 Cycle 5 Cycle 6 Cycle 7

Ifetch

Ifetch

Reg

Reg

Reg

DMem

Reg

A cada ciclo todas as instruções no pipeline se movem, avançando de um estágio

do pipeline. A figura abaixo mostra a execução de uma sequencia de instruções

no pipeline.

Time (clock cycles)

and r7,r8,r9

or r10,r11,r12

Xor r13,r14,r15

Ifetch

DMem

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

ALU

sub r4,r5,r6

Reg

ALU

Ifetch

ALU

O

r

d

e

r

add r1,r2,r3

WB

ALU

I

n

s

t

r.

MEM

ALU

IF ID/RF EX

Reg

Reg

Reg

Reg

DMem

aula6.doc

Reg

6 de 26

Na figura acima, não há dependências entre as instruções, mas elas podem

ocorrer, como no caso abaixo.

Ifetch

and r6,r1,r7

or

r8,r1,r9

xor r10,r1,r11

DMem

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

ALU

sub r4,r1,r3

Reg

ALU

Ifetch

ALU

O

r

d

e

r

add r1,r2,r3

WB

ALU

I

n

s

t

r.

MEM

ALU

IF ID/RF EX

Reg

Reg

Reg

Reg

Reg

DMem

Na figura acima, três instruções têm sua execução afetada pela necessidade do

dado produzido pela primeira (r1). Ou seja, elas possuem dependência de dados

com a primeira.

Existem três tipos de dependência de dados: dependência verdadeira (read after

write – RAW), anti dependência (write after read – WAR), e dependência de

saída (write after write – WAW). Outro tipo de dependência importante é a

dependência de controle. Estes quatro tipos de dependência são ilustrados na

tabela abaixo.

I: add r1,r2,r3

J: sub r4,r1,r3

I: sub r4,r1,r3

J: add r1,r2,r3

K: mul r6,r1,r7

Dependência Verdadeira (RAW)

Anti Dependência (WAR)

I: sub r1,r4,r3

J: add r1,r2,r3

K: mul r6,r1,r7

Dependência de Saída (WAW)

10: beq r1,r3,36

14: and r2,r3,r5

18: or

r6,r1,r7

22: add r8,r1,r9

36: xor r10,r1,r11

Dependência de Controle

aula6.doc

7 de 26

No exemplo de dependência verdadeira de dados, as instruções I e J não podem

ser executadas em paralelo nem fora de ordem, já que a instrução J precisa do

conteúdo de r1, que será produzido pela instrução I. No exemplo de anti

dependência, dependendo do hardware I e J podem até ser executadas em

paralelo (se os dados forem lidos no início do ciclo e escritos no final), mas não

fora de ordem. No exemplo de dependência de saída, I e J não podem ser

executadas em paralelo ou fora de ordem.

No exemplo de dependência de controle, vemos que as instruções de número 14,

18 e 22 só devem ser executadas se o desvio (beq) não for tomado: elas

possuem, então, dependência de controle com relação à instrução 10 (beq).

Em máquinas pipeline como as apresentadas, anti dependências e dependências

de saída não causam problemas, mas dependências verdadeiras e dependências

de controle precisam ser tratadas.

Na figura abaixo, o dado produzido pela primeira instrução precisa ser, de algum

modo, comunicado para as instruções que precisam dele em estágios anteriores

do pipeline.

or

r8,r1,r9

xor r10,r1,r11

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

ALU

and r6,r1,r7

Ifetch

DMem

ALU

sub r2,r1,r3

Reg

ALU

O

r

d

e

r

add r1,r2,r3 Ifetch

ALU

I

n

s

t

r.

ALU

Time (clock cycles)

Reg

Reg

Reg

Reg

DMem

aula6.doc

Reg

8 de 26

Uma técnica conhecida como forwarding pode ser empregada para resolver o

problema de dependências verdadeiras dentro de pipeline. A figura abaixo

ilustra como a técnica forwarding resolve o problema de dependências de dados

verdadeiras dentro do pipeline.

NextPC

mux

MEM/WR

EX/MEM

ALU

mux

ID/EX

Registers

Data

Memory

mux

Immediate

O circuito de forwarding envia os dados necessários para cada estágio do

pipeline conforme necessário. A figura abaixo mostra exemplos, inclusive um de

um lw com um sw.

or

r8,r6,r9

xor r10,r9,r11

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

ALU

sw r4,12(r1)

Ifetch

DMem

ALU

lw r4, 0(r1)

Reg

ALU

O

r

d

e

r

add r1,r2,r3 Ifetch

ALU

I

n

s

t

r.

ALU

Time (clock cycles)

Reg

Reg

Reg

Reg

DMem

aula6.doc

Reg

9 de 26

Contudo, há casos como o abaixo que não tem solução e uma “bolha” tem que

ser inserida no pipeline.

and r6,r1,r7

or

DMem

Ifetch

Reg

DMem

Reg

Ifetch

Reg

DMem

Reg

Ifetch

r8,r1,r9

Reg

ALU

O

r

d

e

r

sub r4,r1,r6

Reg

ALU

lw r1, 0(r2) Ifetch

ALU

I

n

s

t

r.

ALU

Time (clock cycles)

Reg

DMem

Reg

Na figura acima, o dado do lw só é produzido muito tarde para ser forwarded

(não pode haver forwarding para traz...). A figura abaixo mostra a bolha.

and r6,r1,r7

or r8,r1,r9

Reg

DMem

Ifetch

Reg

Bubble

Ifetch

Bubble

Reg

Bubble

Ifetch

Reg

DMem

Reg

Reg

DMem

ALU

sub r4,r1,r6

Ifetch

ALU

O

r

d

e

r

lw r1, 0(r2)

ALU

I

n

s

t

r.

ALU

Time (clock cycles)

aula6.doc

Reg

DMem

10 de 26

As figuras a seguir mostram a execução de uma sequencia de instruções sem

dependência de dados:

Determinou o

endereço de A

A

06 - add r1,r2,r3

05 - xor r11,r12,r13

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

MUX MUX

Imm

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

02 - and r2,r3,r4

Zero?

RS1

RS2

03 - or r5,r6,r7

MUX

Next PC

04 - sub r8,r9,r10

WB Data

Ciclo 6

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

1

Determinou o

endereço de A

A

07 - and r2,r3,r4

06 - add r1,r2,r3

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

03 - or r5,r6,r7

Zero?

RS1

RS2

04 - sub r8,r9,r10

MUX

Next PC

05 - xor r11,r12,r13

WB Data

Ciclo 7

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

2

aula6.doc

11 de 26

Determinou o

endereço de A

A

08 - or r5,r6,r7

07 - and r2,r3,r4

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

ALU

Imm

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

05 - xor r11,r12,r13 04 - sub r8,r9,r10

MUX

Next PC

06 - add r1,r2,r3

WB Data

Ciclo 8

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

3

Determinou o

endereço de A

A

08 - or r5,r6,r7

09 - sub r8,r9,r10

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

Imm

ALU

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

06 - add r1,r2,r3 05 - xor r11,r12,r13

MUX

Next PC

07 - and r2,r3,r4

WB Data

Ciclo 9

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

4

aula6.doc

12 de 26

Determinou o

endereço de A

A

09 - sub r8,r9,r10

10 - xor r11,r12,r13

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

06 - add r1,r2,r3

Zero?

RS1

RS2

07 - and r2,r3,r4

MUX

Next PC

08 - or r5,r6,r7

WB Data

Ciclo 10

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

5

aula6.doc

13 de 26

As figuras a seguir mostram a execução de uma sequencia de instruções com

dependência de dados e sem forwarding:

Determinou o

endereço de A

Com dependência de dados

06 - add r1,r2,r3

05 - xor r11,r12,r13

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

MUX MUX

Imm

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

02 - and r2,r3,r4

Zero?

RS1

RS2

03 - or r5,r6,r7

MUX

Next PC

04 - sub r8,r9,r10

WB Data

A

Ciclo 6

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

6

Determinou o

endereço de A

A

07 - and r2,r1,r4

06 - add r1,r2,r3

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

03 - or r5,r6,r7

Zero?

RS1

RS2

04 - sub r8,r9,r10

MUX

Next PC

05 - xor r11,r12,r13

WB Data

Ciclo 7

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

7

aula6.doc

14 de 26

Determinou o

endereço de A

A

08 - or r5,r6,r7

07 - and r2,r1,r4

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

ALU

Imm

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

05 - xor r11,r12,r13 04 - sub r8,r9,r10

MUX

Next PC

06 - add r1,r2,r3

WB Data

Ciclo 8

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

8

Determinou o

endereço de A

A

08 - or r5,r6,r7

bolha

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

Imm

ALU

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

06 - add r1,r2,r3 05 - xor r11,r12,r13

MUX

Next PC

07 - and r2,r1,r4

WB Data

Ciclo 9

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

9

aula6.doc

15 de 26

Determinou o

endereço de A

A

08 - or r5,r6,r7

bolha

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

ALU

Imm

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

06 - add r1,r2,r3

bolha

MUX

Next PC

07 - and r2,r1,r4

WB Data

Ciclo 10

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

10

Determinou o

endereço de A

A

08 - or r5,r6,r7

bolha

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

bolha

Zero?

RS1

RS2

bolha

MUX

Next PC

07 - and r2,r1,r4

WB Data

Ciclo 11

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

11

aula6.doc

16 de 26

Determinou o

endereço de A

A

08 - or r5,r6,r7

09 - sub r8,r9,r10

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

MUX MUX

Imm

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

bolha

Zero?

RS1

RS2

bolha

MUX

Next PC

07 - and r2,r1,r4

WB Data

Ciclo 12

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

12

Determinou o

endereço de A

A

09 - sub r8,r9,r10

10 - xor r11,r12,r13

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

bolha

Zero?

RS1

RS2

07 - and r2,r3,r4

MUX

Next PC

08 - or r5,r6,r7

WB Data

Ciclo 13

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

13

aula6.doc

17 de 26

As figuras a seguir mostram a execução de uma sequencia de instruções com

dependência de dados e com forwarding:

Determinou o

endereço de A

Com forwarding

06 - add r1,r2,r3

05 - xor r11,r12,r13

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

MUX MUX

Imm

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

02 - and r2,r3,r4

Zero?

RS1

RS2

03 - or r5,r6,r7

MUX

Next PC

04 - sub r8,r9,r10

WB Data

A

Ciclo 6

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r1,r7

Instr. 09 – sub r8,r1,r10

Instr. 10 – xor r11,r1,r13

CS252-s06, Lec 02-intro

15

Determinou o

endereço de A

A

07 - and r2,r1,r4

06 - add r1,r2,r3

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

03 - or r5,r6,r7

Zero?

RS1

RS2

04 - sub r8,r9,r10

MUX

Next PC

05 - xor r11,r12,r13

WB Data

Ciclo 7

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r1,r7

Instr. 09 – sub r8,r1,r10

Instr. 10 – xor r11,r1,r13

CS252-s06, Lec 02-intro

16

aula6.doc

18 de 26

Vai ler o valor

errado no fim

do ciclo

Ciclo 8

08 - or r5,r1,r7

Determinou o

endereço de A

07 - and r2,r1,r4

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

ALU

Imm

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

05 - xor r11,r12,r13 04 - sub r8,r9,r10

MUX

Next PC

06 - add r1,r2,r3

WB Data

A

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r1,r7

Instr. 09 – sub r8,r1,r10

CS252-s06, Lec 02-intro

Vai ler o valor

errado no fim

do ciclo

A

Ciclo 9

Usa o valor

correto via

forwarding

08 - or r5,r1,r7

09 - sub r8,r1,r10

07 - and r2,r1,r4

Next SEQ PC

Zero?

RS1

MUX

MEM/WB

Data

Memory

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

Imm

ALU

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

06 - add r1,r2,r3 05 - xor r11,r12,r13

Next SEQ PC

Adder

4

Determinou o

endereço de A

MUX

Next PC

17

WB Data

Instr. 10 – xor r11,r1,r13

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r1,r7

Instr. 09 – sub r8,r1,r10

Instr. 10 – xor r11,r1,r13

CS252-s06, Lec 02-intro

18

aula6.doc

19 de 26

Vai ler o valor

certo no fim

do ciclo

Ciclo 10

Usa o valor

correto via

forwarding

08 - or r5,r1,r7

09 - sub r8,r1,r10

10 - xor r11,r1,r13

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

06 - add r1,r2,r3

Zero?

RS1

RS2

07 - and r2,r1,r4

MUX

Next PC

Determinou o

endereço de A

WB Data

A

Sign

Extend

RD

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r1,r7

Instr. 09 – sub r8,r1,r10

Instr. 10 – xor r11,r1,r13

Registradores feitos

com FFs tipo D

acionados por nívelCS252-s06,

Lec 02-intro

19

aula6.doc

20 de 26

As figuras a seguir mostram que, mesmo com forwarding, há casos que não é

possível evitar bolhas no pipeline:

08 - or r5,r6,r7

07 - and r2,r1,r4

06 - lw r1,0(r3)

Next SEQ PC

Next SEQ PC

Adder

Zero?

RS1

MUX

MEM/WB

Data

Memory

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

ALU

Imm

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

05 - xor r11,r12,r13 04 - sub r8,r9,r10

MUX

Next PC

4

Determinou o

endereço de A

Dependência verdadeira - LW

WB Data

A

Ciclo 8

RD

RD

Instr. 06 – lw r1,0(r3)

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

20

Determinou o

endereço de A

A

08 - or r5,r6,r7

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

05 - xor r11,r12,r13

Zero?

RS1

RS2

06 - lw r1,0(r3)

bolha

MUX

Next PC

07 - and r2,r1,r4

WB Data

Ciclo 9

Sign

Extend

RD

RD

RD

Instr. 06 – lw r1,0(r3)

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

21

aula6.doc

21 de 26

Determinou o

endereço de A

A

09 - sub r8,r1,r10

08 - or r5,r6,r7

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

Imm

ALU

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

06 - lw r1,0(r3)

bolha

MUX

Next PC

07 - and r2,r1,r4

WB Data

Ciclo 10

Sign

Extend

RD

RD

RD

Instr. 06 – lw r1,0(r3)

Instr. 07 – and r2,r1,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

22

aula6.doc

22 de 26

Ifetch

14: and r2,r3,r5

18: or

de

DMem

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

DMem

Ifetch

Reg

Reg

Ifetch

r6,r1,r7

dependência

ALU

10: beq r1,r3,36

uma

ALU

ilustra

ALU

abaixo

ALU

figura

ALU

A

22: add r8,r1,r9

controle.

Reg

36: xor r10,r1,r11

Reg

Reg

Reg

DMem

Reg

Dependências de controle provocam bolhas para trás (squash de instruções).

Desvios condicionais – bolhas para trás

06 - beqz r1, i10

05 - xor r11,r12,r13

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

Instr. 05 – xor r11,r12,r13

ALU

Instr. 04 – sub r8,r9,r10

Imm

MUX MUX

Instr. 03 – or r5,r6,r7

ID/EX

Instr. 02 – and r2,r3,r4

Reg File

IF/ID

Memory

Address

Instr. 01 – add r1,r2,r3

02 - and r2,r3,r4

Zero?

RS1

RS2

03 - or r5,r6,r7

MUX

Next PC

04 - sub r8,r9,r10

Determinou o

endereço de A

WB Data

A

Ciclo 6

Sign

Extend

RD

RD

RD

Instr. 06 – beqz r1, i10

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

23

aula6.doc

23 de 26

Determinou o

endereço de A

A

07 - and r2,r3,r4

05 - xor r11,r12,r13

06 - beqz r1, i10

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Sign

Extend

RD

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

ALU

Imm

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

03 - or r5,r6,r7

MUX

Next PC

04 - sub r8,r9,r10

WB Data

Ciclo 7

RD

RD

Instr. 06 – add r1,r2,r3

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

24

Determinou o

endereço de A

A

08 - or r5,r6,r7

07 - and r2,r3,r4

Next SEQ PC

Next SEQ PC

Adder

4

Zero?

RS1

MUX

MEM/WB

Data

Memory

Instr. 05 – xor r11,r12,r13

EX/MEM

Instr. 04 – sub r8,r9,r10

Imm

ALU

Instr. 03 – or r5,r6,r7

MUX MUX

Instr. 02 – and r2,r3,r4

ID/EX

Instr. 01 – add r1,r2,r3

Reg File

IF/ID

Memory

Address

RS2

05 - xor r11,r12,r13 04 - sub r8,r9,r10

MUX

Next PC

06 - beqz r1, i10

WB Data

Ciclo 8

Sign

Extend

RD

RD

RD

Instr. 06 – beqz r1, i10

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

25

aula6.doc

24 de 26

Determinou o

endereço de A

A

10 - xor r11,r12,r13

07 - and

r2,r3,r4

anulada

Next SEQ PC

Next SEQ PC

Adder

4

MUX

MEM/WB

Data

Memory

EX/MEM

ALU

Imm

MUX MUX

Instr. 01 – add r1,r2,r3

ID/EX

Reg File

IF/ID

Memory

Address

RS2

Instr. 03 – or r5,r6,r7

05 - xor r11,r12,r13

Zero?

RS1

Instr. 02 – and r2,r3,r4

06 - beqz r1, i10

MUX

Next PC

08 - or

r5,r6,r7

anulada

WB Data

Ciclo 9

Sign

Extend

Instr. 04 – sub r8,r9,r10

RD

Instr. 05 – xor r11,r12,r13

RD

RD

Instr. 06 – beqz r1, i10

Instr. 07 – and r2,r3,r4

Instr. 08 – or r5,r6,r7

Instr. 09 – sub r8,r9,r10

Instr. 10 – xor r11,r12,r13

CS252-s06, Lec 02-intro

26

Note que, se não aproveitarmos os dados disponíveis no estágio de execução

(linhas em vermelho) para determinar o próximo PC, teremos que anular 3

instruções.

A arquitetura abaixo pode reduzir o número de instruções anuladas no caso de

desvios tomados para apenas uma:

Pipeline melhorado

Instruction

Fetch

Memory

Access

Write

Back

Adder

Adder

MUX

Next

SEQ PC

Next PC

Zero?

RS1

MUX

MEM/WB

Data

Memory

EX/MEM

ALU

MUX

ID/EX

Imm

Reg File

IF/ID

Memory

Address

RS2

WB Data

4

Execute

Addr. Calc

Instr. Decode

Reg. Fetch

Sign

Extend

RD

RD

RD

• Perda de apenas um ciclo se o desvio for tomado

CS252-s06, Lec 02-intro

27

aula6.doc

25 de 26

Dependências de controle podem ser tratadas em máquinas pipelined

basicamente de quatro formas diferentes:

1. Parando (stall) o pipeline até que a direção do desvio seja conhecida

2. Predizendo que o desvio não vai ser tomado

3. Predizendo que o desvio vai ser tomado

4. Incluindo o conceito de desvio atrasado (delayed branch) na ISA

Escalonando Branch Delay Slots

A. From before branch

add $1,$2,$3

if $2=0 then

delay slot

becomes

B. From branch target

sub $4,$5,$6

add $1,$2,$3

if $1=0 then

delay slot

becomes

if $2=0 then

add $1,$2,$3

add $1,$2,$3

if $1=0 then

sub $4,$5,$6

C. From fall through

add $1,$2,$3

if $1=0 then

delay slot

sub $4,$5,$6

becomes

add $1,$2,$3

if $1=0 then

sub $4,$5,$6

• A é a melhor escolha, pois enche o slot e reduz a contagem de instruções

(CI)

• Em B, a instrução sub pode precisar ser copiada, aumentando a CI

• Em B e C, não pode haver problemas em executar a sub quando o desvio

não é tomado

CS252-s06, Lec 02-intro

30

aula6.doc

26 de 26