Sistemas Operacionais

Revisando alguns

Conceitos de Hardware

Sumário

●

Hardware

– Processador

– Memória principal

– Cache

– Memória secundária

– Dispositivos de E/S e barramento

– Pipelining

– Arquiteturas RISC e CISC

Hardware

●

Sistema computacional = 3 Unidades

funcionais (subsistemas)

Processador / UCP

Unidade Lóg ica

e Aritmética

Unidade de

Controle

M emória

Principal

Reg istradores

Dispositivos

de E/S

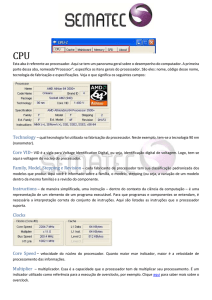

Processador

• Unidade Central de Processamento (CPU) - gerencia

todo o sistema computacional (unidades funcionais).

• Principal função é controlar e executar instruções

presentes na memória principal (soma, subtração,

comparação e movimentação de dados).

É composta por:

Unicade de Controle (UC)

Unidade Lógica e Aritmética (ULA)

Clock

Registradores

Processador

●

●

Unicade de Controle (UC) - Gerencia as

atividades de todos os componentes do

sistema, como a gravação de dados em

discos ou busca de instruções na memória.

Unidade Lógica e Aritmética (ULA)

Realização de operações lógicas (testes e

comparações) e aritméticas (somas e

subtrações).

Processador

●

●

Clock - Sincroniza todas as funções do

processador através do sinal de clock. Pulso

gerado ciclicamente a partir de um cristal de

quartzo polarizado.

Registradores - Armazenam dados

temporariamente.

–

Contador de instruções: CI ou Program Counter:

PC contém o endereço da próxima instrução a ser

executada. Toda vez que o processador busca

nova instrução, CI é atualizado com o endereço

de memória da instrução seguinte.

Processador

●

Registradores

- Apontador da pilha AP ou Stack pointer SP:

Contem o endereço de memória do topo da

pilha, que é a estrutura de dados onde o

sistema mantém informações sobre os

programas que estão sendo executados e

foram interrompidos.

–

Registrador de status ou program status word:

PSW armazena informações sobre a execução de

instruções, como overflow.

Memória Principal

●

●

●

●

●

Memória principal, primária ou real é o local

onde são armazenadas instruções e dados.

É composta por unidades de acesso

chamadas de células de tamanho n bits

Acesso ao conteúdo de uma célula através de

um endereço único.

Especificação do endereço é feita com o MAR

– memory address register.

O memory buffer register MBR guarda o

conteúdo de uma ou mais células.

Memória Principal

Memória principal com 64 Kbytes

0

instrução ou dado

1

2

endereços

●

16

2 -1

célula = 8 bits

Memória Principal

Operação de leitura

✔

UCP armazena no MAR o endereço da

célula a ser lida.

✔

UCP gera sinal de controle para a memória

principal, indicando que uma operação de

leitura deve ser realizada

✔

Conteudo da célula identificada pelo

endereço contido no MAR é transferido para

o MBR.

✔

O conteúdo do MBR é transferido para um

registrador da UCP.

Memória Principal

Operação de Gravação

✔

UCP armazena no MAR o endereço da célula que será

gravada.

✔

UCP armazena no MBR a informação que deverá ser

gravada.

✔

UCP gera sinal de controle para a memória principal,

indicando que uma operação de gravação deve ser

realizada.

✔

O conteúdo do MBR é transferido para uma célula de

memória endereçada pelo MAR.

Memória

Classificação de acordo com a sua volatilidade:

➔

RAM (random access memory) são voláteis.

➔

ROM (read only memory) e

➔

EPROM (erasable programable ROM) são

memórias não-voláteis.

Memória Cache

●

●

●

●

●

●

Volátil

Alta velocidade

Pequena capacidade de armazenamento

Alto custo

Cache hit (processador encontra o dado no

cache) não há necessidade de acesso a

memoria principal

Cache miss obriga o acesso a memória

principal.

Memória Secundária

●

Rel. dispositivos de armazenamento

Registradores

M emória Cache

maior

capacidade de

armazenamento

M emória Principal

M emória Secundária

maior custo e

velocidade

de acesso

Dispositivos de E/S

●

●

Utilizados para permitir a comunicação entre o sistema

computacional e o mundo externo. Podem ser utilizados

como:

Memória secundária

–

–

●

Discos

Fitas magnéticas

Interface usuário-máquina

–

–

–

–

Teclados

Monitores

Impressoras

Plotters

Barramento

Meio físico de comunicação entre unidades

funcionais. Podem ser UCP-memória ou E/S

(mais lentos).

M emória

Principal

U CP

Barramento processador-memória

A daptador

Barramento de E/S

A daptador

Barramento de E/S

●

Pipelining

●

●

Permite ao processador executar múltiplas

instruções paralelamente em estágios

diferentes.

Uma tarefa é dividida em uma subsequencia

de tarefas (busca da instrução, execução e

armazenamento dos resultados).

Pipelining

●

Pipeline em quatro estágios

P1

P2

P3

P4

Unidade de

busca da

instrução

Analisador

da

instrução

Unidade de

busca dos

dados

Unidade de

execução da

instrução

P1

Instr.1 Instr.2 Instr.3 Instr.4 Instr.5 Instr.6 Instr.7

P2

Instr.1 Instr.2 Instr.3 Instr.4 Instr.5 Instr.6

P3

Instr.1 Instr.2 Instr.3 Instr.4 Instr.5

P4

Instr.1 Instr.2 Instr.3 Instr.4

tempo

Arquiteturas RISC e CISC

●

●

●

Linguagem de máquina é a linguagem de

programação realmente entendida pelo

processador.

Cada processador possui um conjunto

definido de instruções de máquina.

Um programa em linguagem de máquina

pode ser executado diretamente pelo

processador para o qual foi escrito, porém

não pode ser executado em máquina de

arquitetura diferente.

Arquiteturas RISC e CISC

Processador RISC (Reduced Instruction Set

Computer:

✗

Possui poucas instruções de máquina

✗

Instruções simples e executadas diretamente

pelo hardware.

✗

Instruções não acessam memória principal e

trabalham com registradores em grande

numero.

✗

Facilta implementação de Pipelining.

Arquiteturas RISC e CISC

Processador CISC (Complex Instruction Set

Computer:

➢

Muitas instruções interpretadas por

microprogramas > microinstruções.

➢

Instruções complexas que podem referenciar

a memoria principal.

➢

Dificil implementação de Pipelining.

➢

Exemplos de processadores CISC:

• Intel Pentium

• Motorola 68xxx

Arquiteuras RISC e CISC

Microprogramação

Aplicativos

Utiltários

Sistema O peracional

Linguag em de M áquina

Arquitetura

RISC

●

M icroprogramação

Circuitos Eletrônicos