PROPOSTA PARA O DROP

Moraes - 20/dezembro

CIRCUITO DROP

Tem por função substituir um conjunto de n time-slots de um framer E1 (1≤n≤31). Os timeslots são gerados externamente e fornecidos a uma taxa exatamente n*64KHz. Trata-se de um

circuito modular, que pode ser cascateado, cuja interface é definida pelos sinais:

serv_in, serv_out: 5 bits in/out para indicar serviço no time-slot 0. O serv_in indica o novo

serviço, e o serv_out indica o serviço recebido pelo drop;

f2048MHz: freqüência de referência;

f4KHz: O drop gera uma freqüência de 4 KHz, a partir da freqüência de referência 2,048Mhz. O

circuito responsável por gerenciar o serviço (serv_in, serv_out) sincroniza-se pelo sinal f4KHz;

fin, fout: sinal que contém a informação dos time-slots(s) a ser(em) substituído(s),

entrando/saindo dados em formato binário (‘0’ ou ‘1’ sem nenhuma codificação);

nck: freqüência gerada pelo drop para amarrar os sinais fin, fout;

ss, n64: especificam respectivamente o endereço inicial e o número de time-slots a ser(em)

substituído(s) Acordou-se em estudar n64 variando entre 1 e 31. Se n64 igual a zero o circuito

drop funciona como um bypass. Se (ss+n64)>31 é gerado um sinal de erro de programação e o

circuito funciona como um bypass. A freqüência dos sinais fin, fout, que é múltipla de n64, deve

ser gerada a partir da freqüência de referência f2048MHz;

código: bit que especifica se será lido ou gerado HDB3 ou AMI;

erroP: sinalização de erro de programação;

erroFA: erro de alinhamento de frame;

erroMFA: erro de alinhamento de multiframe;

erroCRC: erro de CRC (somente ocorre se o drop for programado com cálculo de CRC);

erroHDB3: erro detectado na seqüência de sinais recebidos em DI+ e DI- (somente no formato

HDB3);

DI+,DI-: entrada dos frames E1;

DO+,DO-: saída dos frames E1.

1

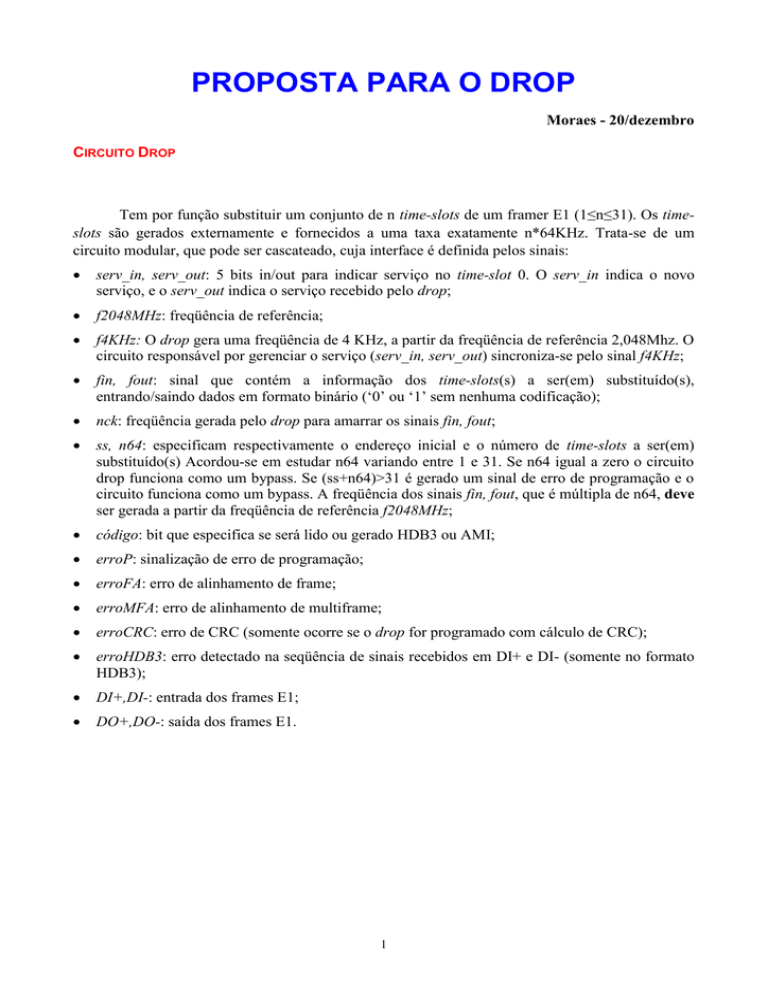

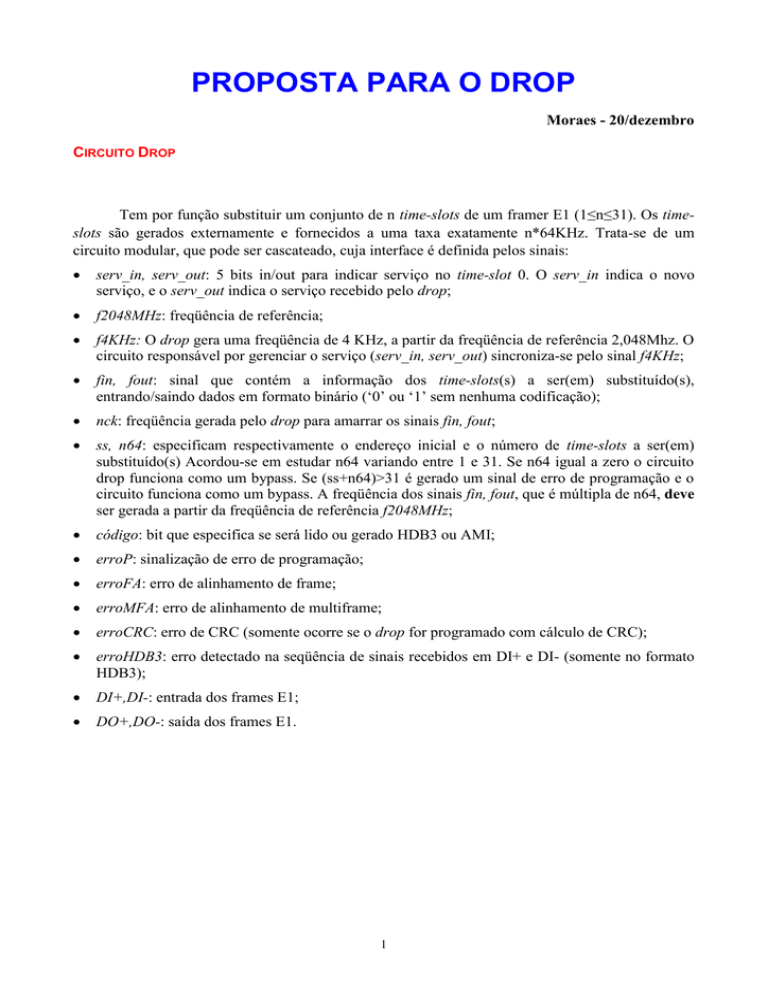

Esquema Básico:

f2048MHz

DO+

E1

Tr

DO -

f2048MHz

DO+

DI+

DO+

DI -

DO -

DI -

DO -

DROP

DROP

N64 ss

DROP

erroP

erroFA

erroMFA

erroCRC

erroHDB3

código

serv_in

serv_out

f4KHz

nck

erroP

erroFA

erroMFA

erroCRC

erroHDB3

código

serv_in

serv_out

f4KHz

fin fout

N64 ss

nck

fin fout

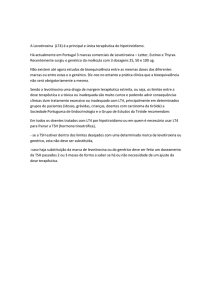

Esquema sem canal de serviço:

2,048 MHz

DI+

DI -

cálculo

de CRC

decodificador

f2048MHz

DI+

data

codificador

0

0

1

1

C2

C1

SYNC

2,048 MHz

DI+

DI -

C2

din

12

sync

bita

0

0

2048

read: endn64

write: end2048

read: end2048

write: endn64

247

fn64

geraf

247

x2

5

DATA OUT

DATA IN

fn64

n64

50M

Informações provenientes do bloco de sincronismo SYNC:

sync: indica se houve ou não sincronização com os dados de entrada

bita (bit address - 12 bits) indica o número do frame, número do time-slot dentro do

frame e o número do bit dentro do time-slot. A formação do bita é:

11

8

frame

7

3

time-slot

2

0

bit

enquanto houver sincronismo, o sinal bita é um contador de 12 bits. Caso haja perda de

sincronismo, deve-se sinalizar este erro, trancar o sistema, zerar bita e esperar um novo

sincronismo.

2

C1: condição para inserir dados provenientes do buffer de entrada (din)

c1 bita[7..3] ≥ ss and bita[7..3] < ss+n64 and sync = ’1’

Ou seja, quando o slot a ser substituído estiver no intervalo estipulado pela entrada ss (start slot)

a origem dos dados passa a ser do buffer de entrada (din), desde que a condição de sincronismo

esteja verdadeira. Caso não se consiga sincronismo o que vai sair é o próprio dado de entrada

(bypass).

A condição para carregar a fila de saída com o antigo valor do(s) slot(s) substituído(s) é dada

também pelo sinal c1.

C2: condição para inserir o CRC. Observando a especificação do multi-frame, observa-se que

apenas nos frames pares insere-se CRC, logo, C2 é bita[8].

O circuito de cálculo de CRC deve ter armazenado sempre os 4 bits anteriores de CRC. A

condição para armazenar estes 4 bits é no final de cada submultiframe, ou seja, quando

bita=7FF ou FFF.

Geração do endereço para leitura/escrita na freqüência de 2048. Sugestão de trecho de processo:

if

bita[7..3]=”00000” then

-- detecta slot zero

end2048 <= (others=>’0’)

elsif f2048’event and f2048=’0’ then

if

c1=’1’ then

end2048 <= end2048 + 1

end if

end if

Explicação: quando estivermos no slot 0 o endereço para leitura/escrita é zerado. Quando

estivermos no(s) time(s) slot(s) a serem substituídos (condição c1=1) o endereço é

incrementado.

Geração do endereço para leitura/escrita na freqüência de n64. Sugestão de trecho de processo:

if

bita[7..3]=LAST_FRAME and bita[2..0] = ”111” then

-- reseta o endn64 após o último bit n2048

endn64 <= (others=>’0’)

elsif fn64’event and fn64 =’0’ then

endn64 <= endn64 + 1

end if

Observação: funcionamento idêntico ao anterior. A vantagem deste código é que não

precisamos saber o tamanho da memória (filas) a ser preenchida. A cada

novo frame é gerado um reset no endereço. Para uma freqüência com n=1 (64K)

iremos escrever 8 posições na memória (ou ler 8 posições), para n=3 (192K)

iremos ler/escrever 24 bits.

3

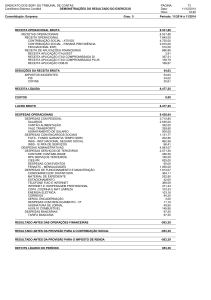

Solução alternativa, com filas de portas simples:

data

C1

x

x

escreve na freqüência

2048, sempre que c1=1

(substituição de slot).

0

0

leitura na freqüência

2048, sempre que c1=1

end2048 (substituição de slot).

end2048

leitura ININTERRUPTA endn64

na freqüência n64

endn64 escrita ININTERRUPTA

na freqüência n64

247

247

x

x

reset dos endereços ocorre no slot 0.

DATA OUT

DATA IN

A idéia é a seguinte: no frames pares escreve-se em uma fila e lê-se da outra. Nos frames

ímpares inverte-se. Com isto garante-se leitura/escrita na ordem correta dos dados, porém a um

custo adicional de bits de memória.

O controle de frames pares/ímpares é dado pelo bita[8], que seria o controle x na figura

acima.

4