Instituto Superior de Ciências do Trabalho e da Empresa

FUNDAMENTOS

DE

ELECTRÓNICA

ETIB1/ETIB2

Resolução da Frequência Tipo 01/02

I. Semicondutores

1.

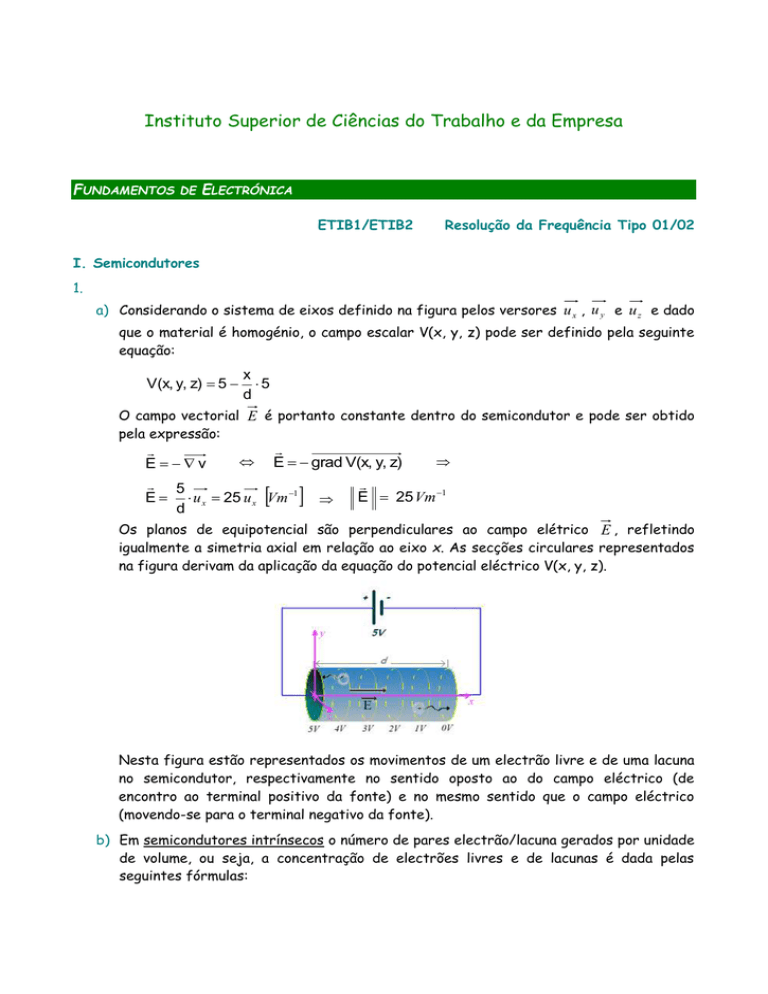

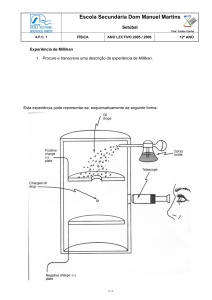

a) Considerando o sistema de eixos definido na figura pelos versores u x , u y e u z e dado

que o material é homogénio, o campo escalar V(x, y, z) pode ser definido pela seguinte

equação:

V(x, y, z) 5

x

5

d

O campo vectorial E é portanto constante dentro do semicondutor e pode ser obtido

pela expressão:

E grad V(x, y, z)

Ev

5

E 25 Vm 1

E u x 25 u x Vm 1

d

Os planos de equipotencial são perpendiculares ao campo elétrico E , refletindo

igualmente a simetria axial em relação ao eixo x. As secções circulares representados

na figura derivam da aplicação da equação do potencial eléctrico V(x, y, z).

Nesta figura estão representados os movimentos de um electrão livre e de uma lacuna

no semicondutor, respectivamente no sentido oposto ao do campo eléctrico (de

encontro ao terminal positivo da fonte) e no mesmo sentido que o campo eléctrico

(movendo-se para o terminal negativo da fonte).

b) Em semicondutores intrínsecos o número de pares electrão/lacuna gerados por unidade

de volume, ou seja, a concentração de electrões livres e de lacunas é dada pelas

seguintes fórmulas:

send

o

n p ni

np

ni B T

2

3

Eg

k T

cm

6

para o silício:

BSi 2.48 1031 K 3cm 6 e EgSi 1.1 eV

considerando

T 27º C 300.15 K

BT

3

Eg

k T

2.48 10 300.15

np

k 8.62 10-5 eV K 1

31

3

1.1

8.6210- 5 300.15

n p 1.5 1010 cm 3 = 1.5 1016 m 3

A condutividade num semicondutor intrínseco depende da concentração de carga móvel

e da sua mobilidade, sendo dada pelas seguintes expressões:

n 300K 1350 cm 2V 1s 1 ,

n n p p q

p 300K 480 cm 2V 1 s 1 ,

q 1.609 10-19 C

300K 1.5 1010 1350 1.5 1010 480 1.609 10-19

300K 4.417 10-6 1 cm 1 4.417 10-4 S m1

A diminuição da temperatura provoca a diminuição da concentração de portadores de

carga como facilmente se deduz a partir da fórmula da concentração intrínseca, dado

que diminui o número de pares electrão-lacuna gerados por agitação térmica. A

mobilidade da carga traduz a facilidade com que a carga se movimenta na estrutura

cristalina. Naturalmente a diminuição da temperatura reduz a agitação térmica e

consequentemente reduz o número de colisões entre a carga móvel e a estrutura do

semicondutor. Assim sendo, provoca um aumento na mobilidade.

c) A resistividade é o inverso da condutividade, pelo que:

1

n

1

n

p p q

300K 226.4 103 cm 2.264 103 m

A resistência do material é dada pela seguinte expressão em que l representa o

comprimento do condutor e A representa a área da sua secção:

R

l

A

R 300K 2.264 103

0.2

4.528 106

0.0001

Pela lei de Ohm pode facilmente calcular-se a corrente no semicondutor:

I

V

R

I300K

5

A 1.104 10-6 A 1.104 A

6

4.528 10

Dado que a corrente que atravessa uma superfície S é o fluxo do vector densidade de

corrente J através dessa superfície, podemos deduzir que:

I J .n s

S

I J 1 s J A

J

S

I

1.104 10 - 2 A m 2

A

Uma forma alternativa para o cálculo do vector densidade de corrente J é através da

seguinte fórmula:

J E

J 4.417 10-4 25 u x A m 2

J 1.104 10-2 u x A m 2

O vector J tem o mesmo sentido do campo eléctrico e da corrente, sendo igualmente

constante ao longo semicondutor, como é representado na seguinte figura:

2.

a) O grau de dopagem nos semicondutores é geralmente muito reduzido pelo que a

estrutura atómica no semicondutor dopado é pouco afectada pela inserção de

impurezas. Assim, os átomos impuros injectados na estrutura cristalina do

semicondutor intrínseco adaptam-se à estrutura existente, integrado-se como se de

átomos de silício se tratassem. Naturalmente, os átomos de fósforo têm cinco

electrões na camada de valência pelo que apenas quatro destes vão assegurar as

ligações covalentes aos átomos de silício vizinhos. Essas ligações são asseguradas por

quatro pares de electrões partilhados formando orbitais igualmente espaçadas como se

representa na figura seguinte. O electrão extra fica numa zona próxima do núcleo do

átomo de fósforo, assegurando assim que a carga é localmente neutra. Em média essa é

a disposição física de todas as impurezas inseridas na estrutura desde que não seja

aplicado nenhum campo eléctrico ao dispositivo. Naturalmente, a ligação destes

electrões quase livres ao núcleo é relativamente fraca e basta um ligeiro fornecimento

de energia (e.g. temperatura ambiente) ao semicondutor para que se tornem

efectivamente electrões livres. Resulta igualmente que o átomo de fósforo que perca

um electrão passe a ser um ião positivo. A figura seguinte representa a estrutura

atómica na vizinhança de um átomo dador.

Num semicondutor dopado a concentração de impurezas é muito superior à

concentração intrínseca, que é devida ao efeito da temperatura na geração de pares

electrão-lacuna. Assim, a carga móvel disponível para condução de electricidade é a que

resulta da existência de átomos dopantes, neste caso os átomos de fósforo são átomos

dadores de electrões, pelo que a carga móvel será maioritariamente do tipo n (i.e.

electrões livres). O sentido do movimento de um electrão livre é naturalmente oposto

ao do campo eléctrico aplicado, ou seja, de encontro ao borne positivo da fonte de

alimentação. Neste caso corresponde a deslocar-se da direita para a esquerda como se

representa na figura anterior.

b) O potencial eléctrico ao longo do semicondutor no sistema de eixos definido pelos

versores u x , u y e u z é dado pela seguinte fórmula:

V(x, y, z) 2

x

2

c

Consequentemente, o campo vectorial E é constante no semicondutor, tal como está

representado na figura anterior, e o seu valor resulta da seguinte expressão:

Ev

2

2

E ux

u x 200 u x Vm 1

c

0.01

A condutividade é dada pela seguinte fórmula, onde a concentração de lacunas p é

desprezável face à concentração de electrões livres n, tal como foi explicado na alínea

anterior.

n n p p q

então,

como

2 1 1

n >> p e n 1350 cm V s

,

q 1.609 10-19 C

n n q 1016 1350 1.609 10-19 2.172 S cm 1 2.172 102 S m 1

O valor da resistência eléctrica deste troço de semicondutor e a corrente que o

percorre são dados pelas seguintes equações:

l

R

A

I

V

R

I

R

1 l

1

A 2.172 10 2

0.01

0.0002

2

2

1.465 103

2

A 1.365 10-3 A 1.365 mA

3

1.465 10

O valor da densidade de corrente eléctrica é dado por:

J E

J 2.172 102 200 u x A m 2

J 4.345 104 u x A m 2

O vector J e a corrente I estão representados na figura anterior.

c) A velocidade média de um electrão (ou lacuna) dentro de um semicondutor é

proporcional ao campo eléctrico aplicado. A mobilidade é essa constante de

proporcionalidade e representa a facilidade com que esse electrão (ou lacuna) se

consegue movimentar no seu interior. Naturalmente, um electrão movimenta-se no

sentido oposto ao do campo eléctrico, pelo que a sua mobilidade tem sinal negativo,

apesar de normalmente se falar do seu módulo (e.g. fórmula da condutividade). Sendo

assim, podemos retirar a velocidade média do electrão da seguinte fórmula:

v n E 0.135 200 u x m s 1 27 u x m s 1

, pois

n 0.135 m 2 V 1s 1

O electrão desloca-se obviamente no sentido do terminal positivo da fonte, ou seja no

sentido oposto ao do versor u x . O tempo médio deriva da fórmula da velocidade média:

v

s

s

t

t

v

, e portanto

tmédio

c

3.7 10- 4 s

27

3. As ligações entre os diversos átomos de uma estrutura de semicondutor intrínseco (e.g.

silício) são asseguradas pelo estabelecimento de ligações covalentes entre átomos

vizinhos. Assim, cada um dos quatro electrões de valência de um átomo une-se a um

electrão de um átomo vizinho formando assim quatro pares de electrões partilhados. Cada

par de electrões forma uma orbital que liga os dois átomos a que pertencem. Este

processo de partilha permite que todos os átomos preencham a sua camada de valência,

formado assim uma estrutura cristalina pura (e.g. semelhante à do diamante).

O processo de geração de pares electrão-lacuna consiste na destruição de uma destas

ligações covalentes. A transferência de energia para um dos electrões numa destas

orbitais, quer pelo efeito fotoeléctrico, quer devido à agitação térmica causada pela

temperatura, é suficiente para que este possa sair da influência do campo eléctrico que o

prende ao(s) núcleo(s). Ao receber essa energia o electrão fica solto para se mover (i.e.

torna-se um electrão livre) sob o efeito de qualquer campo eléctrico aplicado ao

semicondutor. Paralelamente, a falta de um electrão (i.e. a lacuna) na orbital atingida,

originada pela libertação deste electrão, cria localmente um campo eléctrico positivo

devido ao desequilíbrio local de carga, que por sua vez, e em conjunção com o campo

eléctrico aplicado ao semicondutor, pode atrair um electrão de uma orbital vizinha.

A condução de corrente acontece quer pela movimentação de electrões livres no sentido

contrário ao do campo eléctrico aplicado ao semicondutor, quer pelo deslocamento das

lacunas no sentido desse campo. Isto porque a movimentação de carga corresponde à

passagem de uma corrente eléctrica. Daqui também advém o nome de carga móvel, por

oposição às cargas eléctricas fixas que estão rigidamente presas à estrutura, como é o

caso dos iões gerados pela ionização de átomos dadores ou aceitadores em semicondutores

dopados.

Naturalmente, o número destes pares de electrão-lacuna depende fortemente da

temperatura. Isto, aliás, também se depreende a partir da fórmula usada para os calcular,

que foi utilizada na alínea I.2.b). A temperatura de zero graus Kelvin, ou seja, de

-273.15ºC representa a temperatura mínima atingível, e corresponde à ausência total de

agitação térmica. Nessa situação limite, a probabilidade de destruição de uma das ligações

covalentes é nula, pois não há energia disponível para poder libertar um único electrão da

sua orbital. Assim, e na ausência de qualquer tipo de carga móvel, a estrutura torna-se um

isolador perfeito. Naturalmente para temperaturas elevadas a quantidade de carga

disponível é significativa e a condutividade do material semicondutor é relativamente

elevada.

II. Díodos

1.

a) O díodo está claramente polarizado na zona directa ou de condução, uma vez que o

sentido da corrente atravessa percorre o díodo da zona P para a zona N.

Aplicando o método de redução ao absurdo, i.e. partindo do princípio oposto ao que

julgamos/sabemos estar correcto, teríamos:

Hipótese: o díodo está ao corte!

sendo assim sabe-se que ID = 0, e como VR = R.ID então VR=0.

Portanto, VD = VDD - VR = 5V !!

Mas se VD > Vth então o díodo está em condução (o que contraria a hipótese!!)

A forma clássica de analise e cálculo do circuito é:

Hipótese: o díodo está a conduzir!

sendo assim sabe-se que VD Vth 0.6V, e como ID = VR/R:

VR = VDD - VD ID = (VDD - VD)/R 1.47mA

consequentemente ID > 0 o díodo está em condução (confirma a hipótese!!)

b) A seguinte figura representa a característica ID(VD) do díodo (comportamento

exponencial) e a recta de carga a que corresponde a equação da malha, que é dada por:

VVD

I D I S T 1 (característica I/V do díodo)

ID

VDD VD

(lei das malhas)

R

c) A equação não-linear que define o ponto de intersecção das duas equações anteriores

determina o ponto de funcionamento (PFR), ou seja, o ponto onde a recta de carga

intersecta a característica ID(VD) do díodo. Para determinar com precisão o valor

dessa tensão VD pode aplicar-se o seguinte método iterativo:

1ª iterada (hipótese VD0=0.6V)

I

VD1 VT ln D 0 1 0.700V

IS

em que I D0

VDD VD 0

1.46666mA

R

em que I D1

VDD VD1

1.43333mA

R

2ª iterada (hipótese VD1=0.700V)

I

VD 2 VT ln D1 1 0.69977V

IS

3ª iterada (hipótese VD2=0.6997756V)

I

VD 3 VT ln D 2 1 0.699777V

IS

em que I D2

VDD VD 2

1.43341mA

R

Assim, e dado que os valores da tensão VD e da corrente ID estabilizaram, pode

afirmar-se que os seguintes valores estão muito próximos dos valores finais:

VD0.69978V e ID1.4334mA.

d) A tensão de threshold é uma barreira de potencial do díodo, que corresponde à

diferença de potencial mínima aplicável aos seus terminais para que este entre em

condução. Ou seja, este limiar de tensão indica a tensão directa que é necessário

aplicar ao díodo para que este passe a ser um bom condutor eléctrico. Naturalmente,

para tensões inferiores a esta tensão de limiar, a resistência equivalente do díodo é

muito elevada, pelo que nesse caso pode ser considerado um circuito aberto.

Como regra geral, a temperatura influencia os dispositivos feitos com base em material

semicondutor. No caso do díodo, e tal como foi explicado anteriormente, o aumento da

temperatura provoca o aumento da quantidade de carga móvel – lacunas e electrões –

quer na zona de tipo n como na zona de tipo p, o que vai naturalmente melhorar a

condutividade do díodo. Assim, a característica ID (VD) afasta-se do eixo horizontal, o

que corresponde a diminuir a tensão de threshold. Ou seja, a tensão de threshold varia

inversamente com a temperatura.

e) O valor da condutância incremental do díodo é dado pela seguinte fórmula:

VVD

VD

VD

I S T 1

VT

VT

I

I

I D

gm

S

S

40 I D 58.8 mS

VD

VD

VT

25mV

O modelo incremental equivalente do díodo é simplesmente a resistência 1/gm, e o

modelo linear equivalente completo na zona de condução é o seguinte:

2. A seguinte tabela resume as zonas de funcionamento e circuito:

a)

VA

VB

DA

DB

0V

0V

corte

corte

0V

4.5V

corte

condução

5V

0V

condução

corte

5V

5V

condução

condução

b) A seguinte tabela resume os valores da corrente I e da tensão VO, para cada um dos

casos apresentados partindo do princípio que VD(ON)=0.7V.

VA

VB

I

Vo

Vo

0V

0V

0mA

0V

Low

0V

4.5V

3.8mA

3.8V

High

5V

0V

4.3mA

4.3V

High

5V

5V

4.3mA

4.3V

High

O circuito implementa a porta lógica OR.

III. Transístores de Junção Bipolar (TJBs)

1. A seguinte figura representa fisicamente um transístor de junção bipolar do tipo npn:

O transístor de junção bipolar npn é formado a partir da combinação de duas zonas n e

uma zona p, tal como está representado na figura. Assim a união destes materiais cria

duas zonas de junção: a junção base-emissor e a junção base-colector. A zona do emissor é

geralmente mais dopada que o colector, sendo também geralmente mais pequena. A zona

intermédia é designada como base, e é geralmente uma zona relativamente estreita. Em

termos de funcionamento, há quatro zonas distintas de funcionamento a que correspondem

quatro comportamentos distintos e tipos de polarização das zonas de junção. A tabela

seguinte resume estas zonas:

VBE

VBC

JunçãoBE

JunçãoBC

IC

VCE

Saturação

Vth

Vth

directa

directa

IC βF.IB

|VCE | 0.1 V

ZAD

Vth

Vth

directa

inversa

IC = βF.IB

VCE 0.1 V

ZAI

Vth

Vth

inversa

directa

IC = (βR-1).IB

VCE -0.1 V

Corte

Vth

Vth

inversa

inversa

IC IB 0

Uma das principais aplicações de um transístor bipolar é a de ser utilizado em montagens

de amplificação (e.g. amplificadores de audio). Neste tipo de aplicação a zona privilegiada

de utilização é a zona activa directa (ZAD).

Quando o transístor está na ZAD (situação representada na figura anterior) o princípio de

funcionamento deriva da injecção de electrões livres no emissor, que, devido à polarização

directa da junção de base-emissor, se deslocam para a base do transístor. Assim, o

aumento significativo de portadores de tipo n na base (tipo p) provoca que devido ao efeito

de difusão, a grande maioria deste electrões seja arrastado para o colector. Esta relação

traduz-se no coeficiente βF, que relaciona a corrente de colector com a corrente de base,

sendo válida a equação IC=βF.IB.

Na zona de saturação ambas as junções do transístor estão directamente polarizadas,

portanto a diferença de potencial entre o colector e o emissor é quase nula, isto porque

VCE=VCB+VBE e tanto VBE como VBC são aproximadamente iguais à tensão de threshold (e.g.

entre 0.6V e 0.7V). Como VBE é ligeiramente superior a VBC, VCE é geralmente inferior a

0.1V ou 0.2V. Nesta zona a quantidade de carga que é recolhida pelo colector é bastante

inferior e portanto IC βF.IB.

Na zona de corte ambas as junções do transístor estão inversamente polarizadas, pelo que

não há corrente no transístor. A diferença de potencial entre o colector e o emissor é

imposta pelo circuito exterior e pode ser positiva ou negativa.

A ZAI corresponde à utilização do npn com o emissor trocado com o colector, e é uma

zona de funcionamento muito pouco utilizada, essencialmente devido ao facto de o ganho

de corrente ser muito inferior ao que se obtém na ZAD. O princípio de funcionamento

nesta zona é relativamente análogo ao da zona activa directa, mas a injecção de electrões

livres acontece no colector, e a recolha é feita no emissor. A relação entre a corrente de

colector e a corrente de base, que é dada pelo coeficiente βR é muito inferior a βF (pelo

menos uma ordem de grandeza abaixo, i.e. pelo menos dez vezes menor).

2.

a) A determinação do ponto de funcionamento em repouso (PFR) corresponde ao cálculo

das correntes e tensões do transístor em regime estático (ou seja, em DC).

Sendo assim, basta calcular IC, IB, IE, VBE, VCE e VBC. Aplicando o teorema da

sobreposição, anulam-se todas as fontes de sinal e calculam-se os valores DC de todas

as correntes e tensões no dispositivo. Partindo da hipótese que o TJB está na ZAD, e

assumindo que F = 100 e VBE(ON) =Vth = 0.6V temos que:

IC F I B

IC F I B

I 2.4mA

3 VBE( ON ) C

V R I V

I

B

B

BE( ON )

I B 24 A

B

B

RB

VC RC I C VCE VCE 10V 3.6V 6.7V

I E I B I C 2.424mA

VBC VBE VCE 6.1V

Ambas as equações confirmam a hipótese de o TJB estar na ZAD.

b) O valor da transcondutância do TJB na ZAD é dado pela seguinte fórmula:

gm

I C

VBE

VBE

I S VT

VBE

VBE

I VT

IC

S

40 I C 96 mS

VT

25mV

O modelo incremental equivalente (modelo π) do transístor quando este é utilizado na

ZAD está representado na seguinte figura:

Substituindo o TJB pelo seu modelo equivalente na montagem de emissor comum

representada no enunciado, e anulando todas as fontes DC obtém-se o modelo

incremental da montagem representado na figura seguinte. Em que r = o/gm 1k.

O cálculo do ganho incremental de tensão deriva simplesmente da análise do circuito:

v

r

vi

r RB

iC g m v vo g m

r

v

vi RC o 1.426

r RB

vi

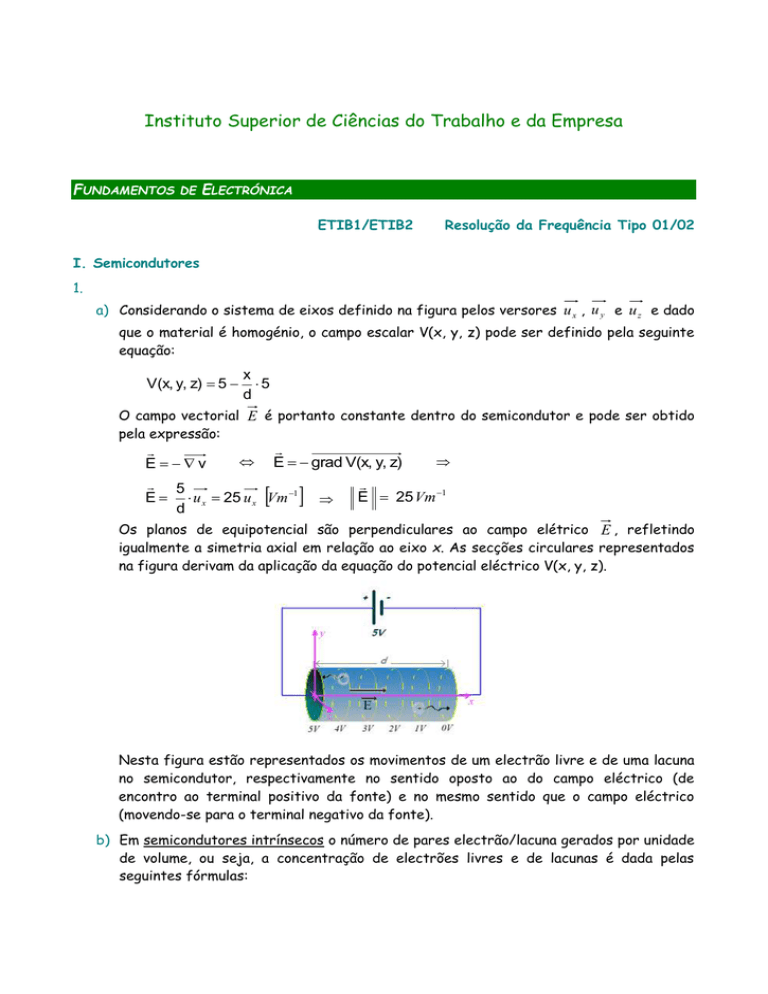

IV. Transístores de Efeito de Campo (MOSFETs)

1. Uma possível implementação física de um transístor de efeito de campo (TEC) do tipo

NMOS está representada na figura seguinte:

O princípio de funcionamento de um TEC consiste na formação ou não de um canal entre o

dreno e a source. A aplicação de uma tensão positiva entre a gate e a source do dispositivo

gera um campo eléctrico que atrai os electrões livres disponíveis na source e no dreno.

Assim, a partir de uma determinada tensão (tensão de limiar ou de threshold semelhante

ao valor usado para os TJBs), a concentração de carga móvel, neste caso de tipo n é

suficiente para assegurar uma conductividade elevada entre a source e o dreno. Ou seja,

pode considerar-se que o canal está formado. Para tensões inferiores a este limiar o canal

não está formado e o TEC apresenta uma conductividade nula entre dreno e source, nesta

situação considera-se que o transístor está cortado. A gate está electricamente separada

do canal por uma fina película de dióxido de silício (isolante), pelo que a corrente de gate é

sempre nula.

O TEC tem duas zonas de condução distintas, uma em que a secção vertical do canal é

aproximadamente rectangular, e que corresponde a ambas as polarizações VGS e VGD

estarem directamente polarizadas - zona linear ou de tríodo. Na outra zona, a tensão VGD é

inferior ao limiar de tensão Vth pelo que o canal estrangula do lado do dreno sendo a secção

do canal aproximadamente triangular – zona activa (ZA) ou zona de saturação. O seguinte

quadro resume as zonas de funcionamento do TEC (NMOS) e as equações válidas em cada

caso.

VGS

ID

VGD

VDS

Linear

(ou de tríodo)

Vth

Vth

2

VDS

W

I D k n VGS Vth VDS

VDS VGS Vth

L

2

ZA

(ou saturação)

Vth

Vth

ID

Corte

Vth

Vth

ID 0

kn W

2

VGS Vth

2 L

VDS VGS Vth

Este dispositivo é perfeitamente simétrico, i.e. não há distinção física entre o dreno e a

source. Assim a identificação do dreno e da source depende do circuito no qual está

inserido, ou seja, a corrente que entra pelo dreno (e que sai pela source) é sempre positiva.

Ou seja, na situação em que VGS Vth e VGD Vth o dreno e a source estão trocados e o TEC

está na mesma na zona activa (ZA), sendo o seu funcionamento exactamente análogo.

2. Num TEC-NMOS de enriquecimento é necessário aplicar uma tensão positiva entre a gate

e a source para que seja formado o canal, ou seja, o canal é criado pelo enriquecimento da

zona espacial sob a gate devido à atração de carga móvel na sua vizinhança (vinda da

source ou do dreno). Num TEC-NMOS de depleção, o canal já está formado mesmo para

VGS = 0, pelo que é necessário aplicar uma tensão negativa entre a gate e a source para que

o canal seja destruído. Ou seja, só a aplicação de um campo eléctrico negativo é que

permite que a carga móvel seja defletida e o transístor corte. As equações anteriores são

válidas em ambos os transístores, resultando apenas que num transístor NMOS de

enriquecimento a tensão de threshold é positiva (i.e. Vth 0), enquanto que num transístor

NMOS de depleção a tensão de threshold negativa (i.e. Vth 0).

3. Considerando a montagem de source comum apresentada no enunciado:

a) Dado que o transístor NMOS está na zona activa, o valor da tensão VGS deriva

directamente da seguinte equação:

ID

kn W

2

VGS Vth

2 L

VGS Vth

2 L

I D 2.014V

kn W

As tensões e correntes DC que estabelecem o PFR do TEC são:

I D I S 1 mA

, VGS 2.014V

, VDS VDD I D RD

, IG 0

O valor de VDS depende do valor de RD que for utilizado.

b) O valor da transcondutância do transístor neste circuito é dado pela seguinte equação:

gm

I D

VGS

k W

2

n VGS Vth

2 L

k W V V 1.414 mS

n

GS

th

VGS

L

c) A figura seguinte representa o modelo incremental do TEC.

O modelo incremental da montagem deriva facilmente deste, e está representado na

seguinte figura:

O cálculo do ganho incremental de tensão deriva simplesmente da análise do circuito:

iO g m v gs vO g m v gs RD

vO

g m RD

v gs

d) O valor de RD está limitado pelo facto de o transístor poder sair da zona activa se o

valor de RD for muito elevado. A equação que garante que o transístor não entra na

zona de tríodo é a seguinte:

VDS VGS Vth

V Vth VGS

VDD I D RD VGS Vth RD DD

ID

VDS VDD I D RD

RD

10.6 2.014

RD 7.986 k

0.001

Assim, o valor máximo de RD que pode ser usado sem que o TEC entre na zona de tríodo

é RD = 7.986k. Caso o TEC entre na zona de tríodo o valor de gm é fortemente

afectado, e o modelo incremental do transístor utilizado para calcular o ganho

incremental de tensão é alterado. Assim, tanto o gm como o ganho de tensão seriam

muito inferiores ao valor dado pela expressão da alínea anterior.

e) O valor máximo do ganho incremental de tensão é obtido exactamente na situação

limite, ou seja, para RD = 7.986k, como facilmente se deduz da expressão do ganho.

Neste caso, temos:

vO

g m RD 11.294

v gs

Neste caso, o valor DC da tensão de saída é dado por:

VDS VDD I D RD 10 0.001 7986 2.014V

Assim é de esperar que o osciloscópio apresente os seguintes sinais (atenção às

escalas):