UNIVERSIDADE FEDERAL DE CAMPINA GRANDE

CENTRO DE ENGENHARIA ELÉTRICA E INFORMÁTICA

DEPARTAMENTO DE ENGENHARIA ELÉTRICA

LABORATÓRIO DE DISPOSITIVOS ELETRÔNICOS

Experimento 5

Transistor MOSFET

LABORATÓRIO DE

DISPOSITIVOS ELETRÔNICOS

Guia de Experimentos

Experimento 5 – Características e Aplicações de Transistores

de Efeito de Campo (FET)

Objetivo

Os experimentos de laboratório aqui apresentados têm por objetivo

familiarizar-se com o estudo das características básicas do transistor de efeito de campo

(MOSFET) e iniciar a exploração de algumas de suas aplicações fundamentais

(amplificadores, portas lógicas).

Introdução Teórica

Transistor de Efeito de Campo

Um transistor bipolar de junção (TBJ) NPN ou PNP é um dispositivo de

corrente controlada no qual estão envolvidas correntes de elétrons e lacunas. O

transistor de efeito de campo (TEC) é unipolar. Ele opera como dispositivo de tensão

controlada com a corrente de elétrons no canal N ou a corrente de lacunas no canal P.

Os dispositivos TBJ ou TEC podem ser usados em um circuito amplificador (ou outros

circuitos semelhantes, desde que sejam adequadamente polarizados).

Existem dois tipos: o transistor de efeito de campo de junção

(abreviadamente TECJ ou JFET – Junction Field Effect Transistor) e o transistor de

efeito de campo de porta isolada (IGFET – Insulated Gate Field Effect Transistor),

mais comumente chamado transistor metal-óxido-semicondutor (TECMOS ou

MOSFET – Metal-Oxide Semiconductor Field Effect Transistor).

O transistor de efeito de campo difere do transistor de junção bipolar nas

seguintes características importantes:

1. É de fabricação simples e ocupa menos espaço. O MOSFET quando integrado

ocupa menos da área da pastilha ocupada pelo transistor bipolar. Desta maneira,

são amplamente utilizados para integração em larga escala (LSI).

2. Em uma parte da faixa de operação dos MOSFET, eles atuam como elementos

resistivos controlados por tensão e ocupam área muito menor que o resistor de

CI correspondente.

3. Apresenta alta impedância de entrada (até 1014Ω). Isto significa que a constante

de tempo do circuito de entrada é bastante grande para possibilitar que a carga

armazenada na pequena capacitância de entrada permaneça por tempo suficiente

para que o dispositivo seja utilizável como elemento de memória em circuitos

digitais.

4. Possui capacidade de dissipar potências elevadas e comutar grandes correntes

em alguns nanossegundos.

5. É menos ruidoso do que um transistor bipolar, e, portanto mais adequando para

estágios de entrada de amplificadores de baixo nível (é extensivamente usado

em receptores FM de alta fidelidade).

6. Os MOSFETS quando utilizados na configuração complementar CMOS, a

dissipação de potência quiescente é essencialmente nula em baixas freqüências.

As principais desvantagens do FET são apresentar uma relativamente pequena

banda de ganho em comparação com o TBJ e maior susceptibilidade a danos quando

manuseado. O uso de dielétrico de porta, normalmente dióxido de silício, apresenta uma

das grandes vantagens do MOSFET, conferindo lhe altíssima impedância de entrada,

comparada aos transistores BJTs. No entanto, este fato também traz uma grande

desvantagem. O dióxido de silício apresenta ruptura dielétrica para campos elétricos da

ordem de 2 x 107 V/cm. Assim, um transistor com espessura de óxido de porta de 10

nm, rompe com tensão da ordem de 20 V.

Característica de Transferência

A característica de transferência é um gráfico da corrente de dreno ID em função

da tensão porta-fonte, VGS, para um valor constante da tensão dreno-fonte, VDS. A

característica de transferência pode ser obtida diretamente a partir de medidas da

operação do dispositivo ou desenhada a partir das características de dreno.

Parâmetros do MOSFET

Os fabricantes especificam vários parâmetros para descrever o

dispositivo MOSFET e tornar possível a escolha entre várias unidades. Alguns dos

parâmetros mais úteis especificados são:

•

Cox – Capacitância do óxido

•

Vt - Tensão de corte (estrangulamento) porta-fonte. A tensão porta-fonte, abaixo

da qual, a corrente no canal dreno-fonte é nula. Nos catálogos dos fabricantes,

denotada por VGS(OFF) ou Vt.

•

gm - a transcondutância

O valor de gm diz quanto a corrente AC mudará quando se aplica uma tensão portafonte AC. gm é medido em Siemens (S).

Normalmente também são fornecidos pelos fabricantes vários outros

parâmetros relacionados com a capacitância do dispositivo, tensão de ruído, tempos

para ligar e desligar e potência de operação.

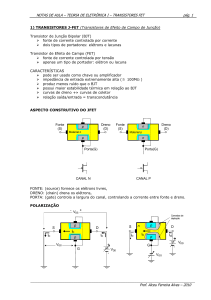

O FET de Metal-Óxido-Semicondutor (MOSFET)

A estrutura básica e o símbolo dos MOSFETs de canal N e canal P tipo

depleção são mostrados nas Figura 1a e 1b respectivamente. As Figuras 1c e 1d

mostram a estrutura básica e o símbolo dos MOSFETs de canal N e canal P tipo

acumulação.

Metal

Porta

Fonte

N

D

Dreno

N

N

Substrato tipo P

G

Óxido

isolante

S

(a)

Metal

Porta

Fonte

N

P

D

Dreno

N

Substrato tipo N

G

Óxido

isolante

S

(b)

Metal

Fonte

Porta

D

Dreno

Óxido

isolante

N

G

N

Substrato tipo P

S

(c)

Metal

Fonte

Porta

D

Dreno

Óxido

isolante

P

P

Substrato tipo N

G

S

(d)

Figura 1 – Diagrama esquemático e símbolo do MOSFET: (a) tipo depleção canal N;

(b) tipo depleção canal P; (c) tipo acumulação canal N; (d) tipo acumulação canal P.

A diferença básica entre os MOSFETs tipo acumulação e depleção está

no canal, ou seja, no modo acumulação para se formar o canal, deve-se aplicar uma

tensão de porta-fonte; no modo depleção o canal já é formado (fabricado), e a tensão

porta-fonte controla a largura do mesmo. A Figura 2 mostra as curvas de transferência

do JFET e dos MOSFET tipo depleção e acumulação.

ID

ID

ID

IDSS

ID,ON

IDSS

VGS

-VP

VGS

VT

VGS

VT

VGS,ON

(a)

(b)

(c)

Figura 2 – Características de transferência: (a) do JFET; (b) do MOSFET canal N modo

de depleção; (c) do MOSFET canal N modo de acumulação.

MOSFETs com Simetria Complementar (CMOS)

É bastante comum, principalmente em circuitos digitais, conectar

transistores MOS tipo P e tipo N internamente a um dispositivo complementar ou

CMOS. A Figura 3a mostra a conexão básica do CMOS. A entrada é conectada a ambas

as portas dos transistores MOS tipo P e tipo N. Uma entrada positiva desliga o MOS

tipo P, liga o tipo N, com a saída caindo para 0 V. Uma entrada de valor baixo ligará o

dispositivo MOS tipo P e desligará o tipo N, com a tensão de saída subindo até +VDD. A

Figura 3b mostra um gráfico da relação entre as tensões de entrada e saída.

O dispositivo CMOS é usado principalmente em circuitos digitais

operando para fornecer saídas de 0 V ou 5 V e requerendo muito pouca potência da

fonte. A maior parte dos circuitos integrados de baixa potência é construída com o

emprego de chaves CMOS.

VDD(+5 V)

Vsaída

+V

Entrada

Saída

Ventrada

(a)

(b)

Figura 3 – Chave CMOS: (a) Conexão de CMOS básica; (b) Relação entrada-saída.

Circuitos Digitais com MOSFET

As mais comuns aplicações de dispositivos MOS são digitais, como por

exemplo, portas lógicas e registradores ou conjuntos de memórias. Devido às

capacitâncias parasitas localizadas de porta para dreno, porta para fonte e substrato, os

circuitos MOSFET são mais lentos que os circuitos bipolares correspondentes. Contudo,

a baixa dissipação de potência e a alta densificação na fabricação tornam os dispositivos

MOS muito convenientes e econômicos para muitas aplicações em baixa velocidade.

Os circuitos digitais com MOSFET consistem somente em FETs e

nenhum outro componente, tais como diodos, resistores ou capacitores. Por exemplo,

consideremos o inversor com MOSFET da Figura 4. O dispositivo Q1 é o FET de

entrada, enquanto Q2 atua como uma resistência de carga e é chamado carga FET.

VDD

Q2

VO

Q1

VI

V I VO

0 VDD

VDD 0

VO = VI

Figura 4 – Circuito inversor com MOSFET, sua tabela verdade e função lógica.

O Circuito Integrado 4007

1

14

P

P

2

13

3

12

VDD

P

4

11

N

5

N

6

VSS

7

10

9

N

8

Figura 5 – Circuito Integrado 4007.

Os substratos dos dispositivos canal N estão conectados a VSS e dos

dispositivos canal P a VDD. Desta maneira, VDD deve ser conectado ao potencial mais

positivo e VSS ao potencial mais negativo do circuito.

PARTE EXPERIMENTAL

Curva Característica

1. Monte o circuito da Figura 1.

2. Varie a tensão VDD de 0-20V. Meça a tensão VGS. Preencha a Tabela I.

3. A partir dos valores medidos determine os parâmetros K e Vt.

Figura 1

VDD

VGS

ID

0,5V

1,0V

1,5V

2,0V

3,0V

4,0V

5,0V

6,0V

VDD

VGS

ID

8,0V

10,0V

12,0V

14,0V

16,0V

18,0V

19,0V

20,0V

7,0V

Tabela I

Amplificador Linear

4. Monte o circuito da Figura 2.

5. Meça as tensões de polarização VG, VD, VS e VGS. A partir dos valores

medidos determine (calcule) a corrente de polarização de dreno ID.

6. Escreva a expressão da reta de carga.

7. Aplique um sinal na entrada e meça o ganho do amplificador.

8. Determine a transcondutância gm, a impedância de entrada e a freqüência

de corte.

Figura 2

Porta Lógica Inversora

9. Monte o circuito da Figura 3.

10. Meça a tensão VDS para VGS = 0V e VGS = 12V.

11. Construa a Tabela da Verdade para este circuito.

Figura 3

Porta Lógica Inversora CMOS

12. Monte o circuito da Figura 4.

13. Meça a tensão VDS para VGS = 0V e VGS = 12V.

14. Construa a Tabela da Verdade para este circuito.

Figura 4

Regiões de operação do MOSFET

A operação de um MOSFET pode ocorrer em três diferentes regiões, dependendo das

tensões aplicadas sobre seus terminais. Para o transistor NMOS os modos são:

REGIÃO DE CORTE: quando VGS < VT

VGS é a tensão entre a porta (gate) e a fonte (source) e VT é a tensão de threshold

(limiar) de condução do dispositivo

Nesta região o transístor permanece desligado e não há condução entre o dreno e

a fonte.

REGIÃO DE TRIODO (ou região linear):

Quando VGS > VT

fonte.

e

VDS < VGS – VT

onde VDS é a tensão entre dreno e

O transistor é ligado, e o canal que é criado permite o fluxo de corrente entre o

dreno e fonte. O MOSFET opera como um resistor, controlado pela tensão na

porta. A corrente do dreno para a fonte é,

Resistência Linear

2

Se VDS for suficientemente pequeno para desprezar o termo VDS

temos uma

relação linear entre a corrente e a tensão VDS constituindo-se, portanto em um

resistor linear com valor controlado pela tensão na porta VGS.

REGIÃO DE SATURAÇÃO: quando VGS > VT e

VDS > VGS – VT

O transístor fica ligado e um canal é criado permitindo o fluxo de corrente entre

o dreno e a fonte. A corrente de dreno é agora relativamente independente da

tensão de dreno e é controlada somente pela tensão da porta de tal forma que,

VGS = VT +

ID

K

AMPLIFICADOR DE ALTO GANHO

Observando-se a curva Vi xVo, do circuito inversor, verifica-se que na

realidade, podemos ter um amplificador de ganho muito elevado, para tensões

de entrada em torno de VDD/2. Com esta característica é possível, portanto, se

construir um amplificador de alto ganho para pequenos sinais, calculando-se

os resistores R1 e R2 de forma que o amplificador fique polarizado em VDD/2,

ou seja, muito próximo do ponto onde ocorre a transição na saída.