Aula 02

Dissipação de Potência

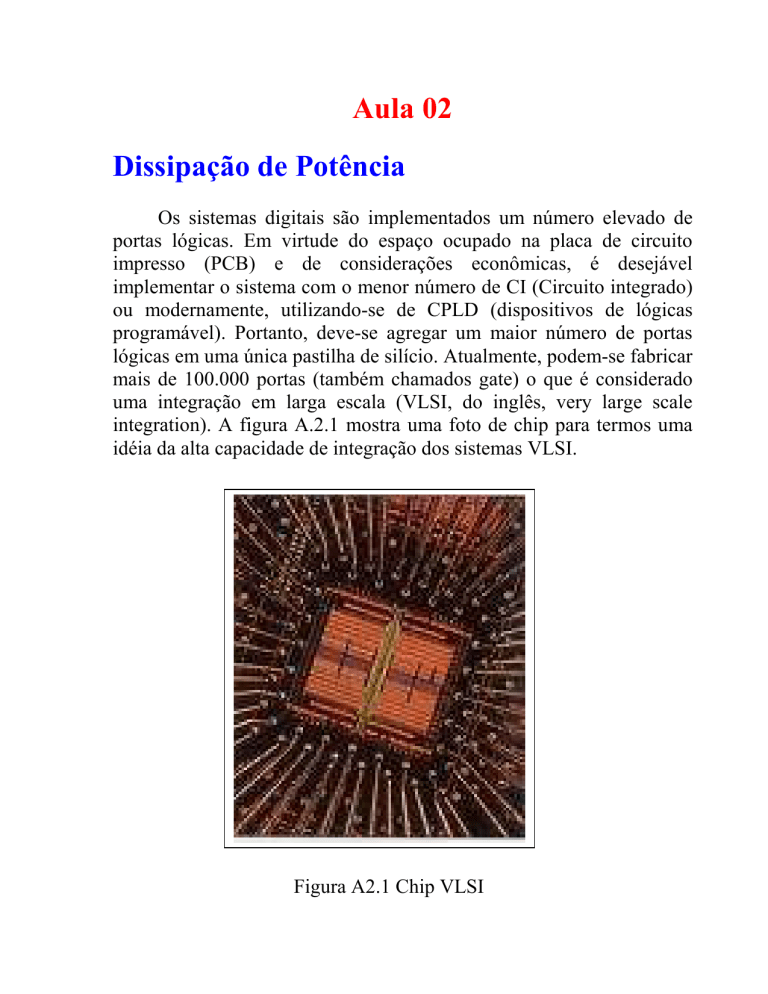

Os sistemas digitais são implementados um número elevado de

portas lógicas. Em virtude do espaço ocupado na placa de circuito

impresso (PCB) e de considerações econômicas, é desejável

implementar o sistema com o menor número de CI (Circuito integrado)

ou modernamente, utilizando-se de CPLD (dispositivos de lógicas

programável). Portanto, deve-se agregar um maior número de portas

lógicas em uma única pastilha de silício. Atualmente, podem-se fabricar

mais de 100.000 portas (também chamados gate) o que é considerado

uma integração em larga escala (VLSI, do inglês, very large scale

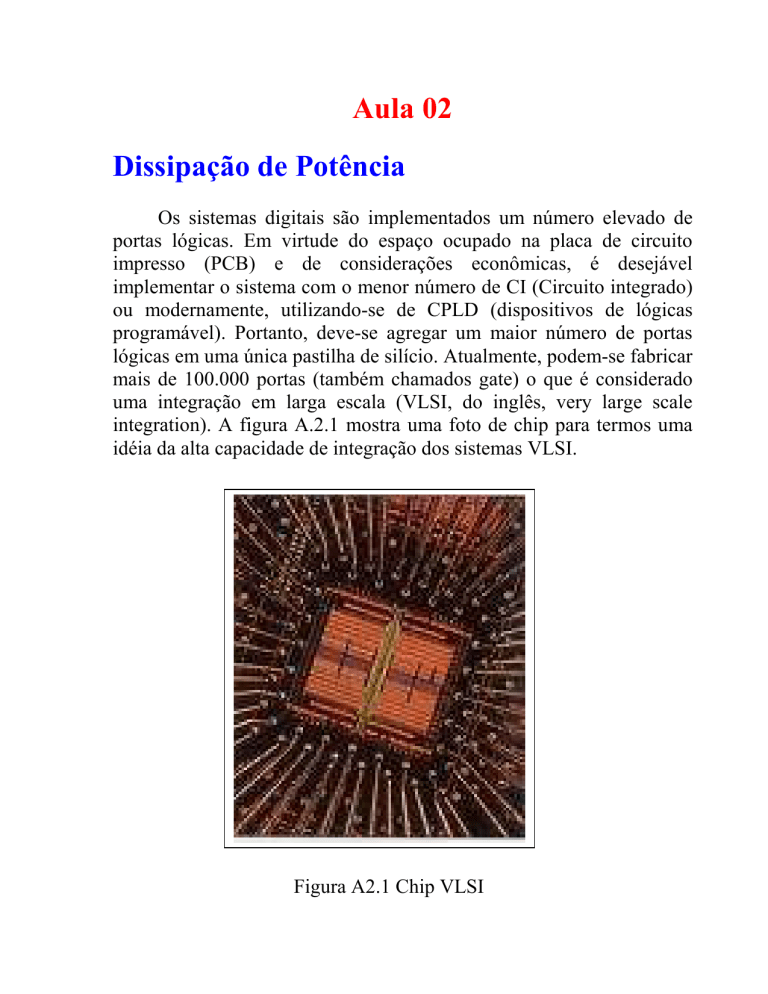

integration). A figura A.2.1 mostra uma foto de chip para termos uma

idéia da alta capacidade de integração dos sistemas VLSI.

Figura A2.1 Chip VLSI

Para manter a dissipação de potência na pastilha dentro de limites

aceitáveis (impostos por questões térmica), a dissipação de potência por

porta deve ser mantida no mínimo. Por essa razão, uma medida de

desempenho muito importante para um inversor lógico é a quantidade

de potência que ele dissipa.

O inversor da figura A.2.2 a) obviamente não dissipa potência

quando vI é baixo e a chave esta aberta. No outro estado, porém, a

potência dissipada é aproximadamente V2DD/R e pode ser significativa.

Esta dissipação de potência ocorre mesmo que o inversor não esteja

chaveando (mudando de estado) e, portanto, é conhecida como

dissipação de potência estática.

Figura A.2.2 a) Um inversor utilizando uma chave. b) circuito

equivalente quando vI é baixo. c) circuito equivalente quando vI é alto.

O inversor da figura A.2.3 não apresenta dissipação de potência

estática e, assim, possui uma vantagem significativa. Infelizmente outro

componente de dissipação de potência aparece com uma capacitância

existe entre o nó de saída do inversor e o terra. Este é sempre o caso

real, três motivos:

• Os dispositivos que implementam as chaves possuem

capacitâncias internas;

• Os fios que interconectam a saída do circuito inversor a

outros circuitos possuem capacitâncias associadas e;

• As próprias entradas dos outros circuitos possuem

capacitâncias internas.

•

Figura A.2.3a) Um inversor mais elaborado com duas chaves. b)

circuito equivalente quando vI é baixo. c) circuito equivalente quando vI

é alto.

Assim, quando o inversor chaveia de um estado para outro,

correntes precisam fluir através das chaves para carregar e descarregar

as capacitâncias de carga. Essas correntes dão origem à dissipação de

potências nas chaves, chamada dissipação de potência dinâmica. Mas

adiante quando estudarmos o inversor CMOS mostraremos que um

inversor chaveado a uma freqüência de f Hz gera uma dissipação de

potência dinâmica dada por

Pdinâmica = f C V2DD

(A.2.1)

Onde C é a capacitância entre o nó de saída e o terra e VDD é a tensão de

alimentação. Essa expressão aplica-se aproximadamente a todos os

circuitos inversores.

Produto atraso-potência

Uma figura de mérito ou uma medida da qualidade da tecnologia

de fabricação do circuito corresponde ao produto atraso-potência (DP

– delay-power product), que é dado por

DP = PDTP

(A.2.2)

O produto atraso-potência tende a ser constante para uma

particular tecnologia de fabricação de circuitos digitais e pode ser

utilizado para comparar diferentes tecnologias. Obviamente, quanto

menor o valor de DP, melhor a tecnologia do ponto de vista de maior

velocidade e menor consumo de potência.

A figura A.2.4 mostra um gráfico de PD em função de TP para a

maioria das tecnologias.

PD

Hipérbole

TP

Figura A.2.4 Gráfico da dissipação de potência dinâmica versus tempo

de propagação para a maioria das tecnologias.

O produto atraso-potência tem a unidade de joules e é

efetivamente uma medida da energia dissipada por ciclo de operação.

Portanto, para uma do tipo CMOS, por exemplo, em que a maior parte

da dissipação é dinâmica, podemos tomar DP como simplesmente CV2.

Exercício: Considere que um inversor da figura A.2.3 é alimentado

por uma tensão de 10 V e tenha uma capacitância de carga de 15 pF.

Obtenha a dissipação de potência dinâmica que resulta quando o

inversor é chaveado em uma freqüência de 2 MHz.

Fan-in Fan-out

O Fan-in de uma porta é o número de entrada que ela

possui. Logo, uma porta OR de quarto entrada tem um fan-in

igual 4.

O Fan-out é o número máximo de porta similares que uma

porta pode acionar ou alimentar enquanto permanece dentro de

suas especificações.

Família CMOS, NMOS e BiCMOS

Antes de apresentarmos esta família vamos fazer uma

breva revisão do transistor de efeito de campo MOS.

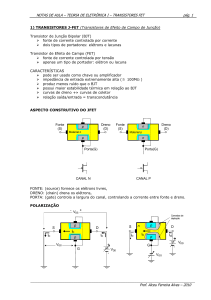

• Revisão do transistor MOSFET

Estrutura do dispositivo.

O transistor MOSFET tipo enriquecimento é o tipo de

transistor de efeito de campo mais utilizado

A figura A.2.5 mostra a estrutura física do MOSFET tipo

enriquecimento canal N. O transistor é fabricado sobre um

substrato do tipo P. Duas regiões fortemente dopadas do tipo N,

indicadas na figura como fonte e dreno n+, são difundida no

substrato. Uma camada fina de dióxido de silício(SiO2) de

espesssura tOX (da ordem de 2-50 nm) é crescido sobre a

superfície do substrato, cobrindo a área entre as regiões da

fonte e do dreno. Um metal é depositado por cima da camada

de óxido para formar o eletrodo de porta do transistor. São

feitos contatos de metal para as regiões da fonte, do dreno e do

substrato, esse último também conhecido como corpo.

Agora fica claro que o nome do dispositivo(MOSFET:

transistor de efeito de campo metal-óxido-semicondutor)

origina-se da sua estrutura física.

Observe que o substrato forma uma junção pn com as

regiões de fonte e de dreno. Na operação normal, essas junções

são mantidas reversamente polarizada o tempo todo.

Como o dreno terá uma tensão positiva em relação a fonte,

as duas junções podem estar efetivamente em corte

simplesmente conectando-se o terminal o substrato ao terminal

da fonte. Portanto, aqui, o substrato será considerado como não

tendo efeito sob a operação do transistor e o MOSFET será

tratado como um dispositivo de três terminais.

a)

b)

Figura A.2.5 a) A estrutura física do NMOS tipo

enriquecimento a) vista em perspectiva b) secção transversa

Finalmente, observe que o MOSFET é um dispositivo

simétrico; portanto, sua fonte e seu dreno podem ser trocados

sem alterações não características do dispositivo.

Operação física do dispositivo.

Considere a situação representada na figura A.2.6. sem

nenhuma tensão aplicada, a dois diodos face a face em série

entre a fonte e dreno. Um diodo é formado pela junção pn entre

a região n+ do dreno e o substrato p e o outro é constituído pela

junção pn entre o substrato p e a região n+ da fonte. Esses

diodos impedem a passagem de corrente entre a fonte e o dreno

quando for aplicada uma tensão vDS.

Quando uma tensão positiva de porta vGS for aplicada ao

dispositivo as lacunas livres em um primeiro instante serão

repelidas da região do substrato sob a porta. Alem disso a

tensão positiva de porta atrairá elétrons para esta mesma região.

Quando for acumulado um número suficiente de elétrons

próximo à superfície do substrato sob a porta, uma região n é

criada, conectando as regiões de fonte e dreno. Agora se uma

tensão for aplicada entre o dreno e a fonte, uma corrente

circulará por essa região n induzida chamada de canal.

Correspondentemente, o MOSFET é chamado de MOSFET

canal n ou, de forma alternativa, um transistor NMOS.

O valor vGS para qual há formação do canal é chamda de

tensão de limiar (threshold voltage) e é representado por VT.

O transistor NMOS com tensão aplicada positiva à porta

O transistor NMOS com vGS > VT e com um pequeno vDS

Característica iD - vDS do MOSFET quando vDS é pequeno.

1

W

iDS = k n' (vGS − VTn )vDS − vDS2

2

L n

para vDS ≅ 0

W

iDS ≅ k n' (vGS − VTn )vDS

L n

Operação para maiores vDS

1 W

2

iDS = k n' (vGS − VTn )

2 L n

A corrente de dreno iD quando vGS > VT

Aumentar vDS após vGS - VT tem pequeno efeito no sobre a

forma do canal

A corrente para região triodo.

iD = kn'

W

1 2

(

)

v

V

v

vDS

−

−

GS

T

DS

L

2

A corrente para região de saturação

iD = kn'

[

W

(vGS − VT )2

L

]

Símbolos para MOSFET

Um MOSFET tipo enriquecimento canal n

Característica iD – vGS do MOSFET

vDS ≥ vGS − VT → vGS =v DS +VT

1 W

1 W

2

2

iDS = k n' (vGS − VTn ) = k n' (vDS )

2 L n

2 L n

então