Organização Funcional

Modelo de Arquitectura de Von Neuman

26

Organização Funcional

Modelo de Arquitectura de Von Neuman

CPU – Unidade Central de processamento (central process unit)

• “Onde tudo se passa”;

• Leitura de Instruções da memória;

• Execução de Instruções;

• Leitura de Dados;

• Escrita de Resultados;

Em sistemas de pequena dimensão, como o PC, utiliza-se

um microprocessador.

Memória Principal

• Dispositivo com capacidade para armazenar informação digital binária,

normalmente organizada em células de 8 bits ;

• Armazena dados, instruções e resultados;

• Dividida em dois tipos: RAM – Ramdom Access Memory e ROM – Read Only

Memory;

27

1

Organização Funcional

Modelo de Arquitectura de Von Neuman

Unidades de I/O

São utilizados para estabelecer a comunicação com o mundo

exterior (periféricos);

Exemplos: Teclado, Disco, Rato

Bus de Sistema

• Conjunto de linhas (ligações) que transportam informação digital binária;

• Permitem a comunicação entre o CPU, a memória e as unidades de I/O;

• Este Bus é constituído pelo Bus de Dados, Bus de Endereços e Bus de

Controlo;

CLK- Clock

Define a frequência de operação do sistema. É utilizado para efectuar a sincronização

das operações;

28

Organização Funcional

Modelo de Arquitectura de Von Neuman

Bus de Dados

Conjunto de linhas (ligações físicas) por onde se transporta a

informação digital binária (instruções, dados, resultados)

entre o CPU, memória e I/O (bidireccional).

A largura do bus de dados é dado pelo número de linhas do

bus ou pelo numero de bits, “tamanho”, do microprocessador.

Modelo

Bus dados Bus dados

interno

externo

8088

16

8

8086

16

16

80286

16

16

80386SX

32

16

80486

32

32

29

2

Organização Funcional

Modelo de Arquitectura de Von Neuman

Bus de Endereços

Conjunto de linhas (ligações físicas) que transportam o

endereço das células de memória ou dos portos de I/O

(unidireccional).

A largura do bus de endereços é dado pelo número de linhas

do bus ou pelo numero de bits, e define a capacidade de

endereçamento.

N.º Linhas (N)

Capacidade

Endereçamento

8088

20

1Mb

8086

20

1Mb

80286

24

16Mb

80386SX

32

4Gb

80486

32

4Gb

Modelo

Para N bits consigo uma capacidade

de endereçamento de 2N.

1K=210=1024

1M=220=1024K

1G=230=1024M

30

Organização Funcional

Modelo de Arquitectura de Von Neuman

Bus de Controlo

Contém os sinais necessários para uma correcta implementação do protocolo de

comunicação. Podemos referir como exemplo a comunicação entre CPU, memória

e I/O.

M/IO’ – Controla o acesso à memória ou

unidades de I/O.

RD’ – Operações de Leitura.

Memória

I/O

CPU

WR’ – Operações de Escrita.

CPU

Memória

I/O

31

3

Organização Funcional

Armazenamento da Informação Digital Binária

A organização da memória é feita em células,

normalmente constituídas por 8 bits. A cada célula

é atribuído um endereço.

Logo, a palavra do computador é igual à unidade

de memória mínima endereçável.

00001h

Endereços

00000h

Células de memória

O armazenamento de dados é baseado no

modelo “LITLE ENDIAN”, que se traduz no

facto dos bytes menos significativos serem

armazenados

nos

endereços

menos

significativos.

3A

00FF3h

42

00FF2h

1F

00FF1h

01

00FF0h

…

Consideremos as seguintes variáveis

byte – 8 bits com valor BD(h) armazenado em 0000Ah

Word – 16 bits com valor AC19h armazenado em 00F0h.

dword – 32 bits com valor 3A421F01h armazenado em 00FF0h

AC

000F1h

19

000F0h

….

BD

0000Ah

32

Organização Funcional

Organização da memória principal

byte

Bus Endereços

A19..A0

00FA1h

CPU

MEMR’

MEMW’

Células

Descodificador

de

endereços

Registo

de

Dados

D0

D7

Bus de Dados

33

4

Organização Funcional

Operação de leitura da célula de memória com endereço 00FA1h

•

•

O CPU activa a linha de controlo MEMR

O CPU coloca o valor 00FA1h nas linhas A19-A0 do Bus Endereços.

•

•

A memória descodifica o endereço 00FA1h, activando a célula de

memória correspondente.

Por se tratar de uma operação de leitura ( MEMR activado) o conteúdo da

célula activada é colocado no registo de dados.

34

Estrutura interna do CPU (microprocessador) 8086

Blocos funcionais

Execution Unit (EU)

Registos: AX, BX, CX, DX,

SP,BP, SI, DI

Operandos

Bus Interface Unit (BIU)

Registos de Segmento: CS,

DS, SS, ES

Registo de Instrução: IP

Addressing Unit (AU)

Controlo dos Bus

Calculo de Endereços

ALU (16bits)

Registo de Flags

Instruction Prefetch Queue

Fila de espera das instruções (6

bytes)

Control Unit (CU)

Registo de instruções

35

5

Estrutura interna do CPU (microprocessador) 8086

Registos de uso genérico

AX

15

8

AL

•AX registo de 16 bits

•AH registo de 8 bits (8 bits + significativos)

•AL registo de 8 bits (8 bits - significativos)

•Registo acumulador

•Implícito em algumas instruções

BL

•BX registo de 16 bits

•BH registo de 8 bits (8 bits + significativos)

•BL registo de 8 bits (8 bits - significativos)

•Registo de Base

•Normalmente utilizado para endereçar

variáveis em memória.

7

AH

0

BX

15

8

7

BH

0

36

Estrutura interna do CPU (microprocessador) 8086

Registos de uso genérico

CX

15

8

7

CH

0

CL

DX

15

8

DH

7

0

DL

•CX registo de 16 bits

•CH registo de 8 bits (8 bits + significativos)

•CL registo de 8 bits (8 bits - significativos)

•Registo acumulador

•Implícito em algumas instruções como

contador.

•DX registo de 16 bits

•DH registo de 8 bits (8 bits + significativos)

•DL registo de 8 bits (8 bits - significativos)

•Registo de Dados

•Utilizado em algumas operações

aritméticas.

•Utilizado em instruções de I/O

37

6

Estrutura interna do CPU (microprocessador) 8086

Registos de endereçamento

SP

15

0

•SP registo de 16 bits

•Stack Pointer

•Utilizado para referenciar variáveis na

pilha do sistema.

BP

15

0

•BP registo de 16 bits

•Base Pointer

•Utilizado para referenciar parâmetros e

variáveis locais em subrotinas

38

Estrutura interna do CPU (microprocessador) 8086

Registos de indexação

SI

15

0

•SI registo de 16 bits

•Source Index

15

DI

0

•DI registo de 16 bits

•Destination Index

Estes registos são utilizados para referenciar variáveis em memória, bem como

em algumas instruções específicas no tratamento de cadeias de caracteres.

39

7

Estrutura interna do CPU (microprocessador) 8086

Registos especiais

Registo de FLAGS (estado)

15

14 13 12

11 10

9

8

7

6

O

I

T

S

Z

D

5

4

3

A

2

P

1

0

C

C – Carry – Ultimo transporte em operações aritméticas;

P – Paridade

A – Auxiliary Carry – transporte intermédio em operações com números BCD

Z – Zero – Resultado=0 da ultima operação aritmética; Lógico.

S – Sinal – Sinal do resultado de uma adição ou subtracção

T – Trap – Utilizado para debugging de software

I – Interrupt

D – Direction – Utilizado em manipulações de strings.

O – Overflow – Referencia a existência de transbordo.

40

Estrutura interna do CPU (microprocessador) 8086

Registos especiais

Registo apontador de instrução

15

0

•Instruction Pointer (IP)

•Registo de 16 bits

•Contém o endereço da próxima instrução

a ser executada

Registos de segmentos

No 8086 existem 4 registos de segmentos, todos eles de 16 bits:

• CS – “Code Segment” – Segmento de código - Armazena as instruções do

programa

CS:[IP] – Ponteiro para a próxima instrução a ser Executada

41

8

Estrutura interna do CPU (microprocessador) 8086

Registos especiais

Registos de segmentos

• DS – “Data Segment” – Segmento de dados

Armazena dados/resultados relativos a variáveis

DS:<deslocamento>

• SS – “Stack Segment” – Segmento de pilha

Suporte à Programação estruturada: Subprogramas; passagem de

parâmetros

SS:<deslocamento>

• ES – “Extra Segment” – Segmento extra

Segmento auxiliar, utilizado por exemplo na manipulação de algumas

cadeias de caracteres

42

Estrutura interna do CPU (microprocessador) 8086

Segmentos de memória

Organização da memória em segmentos

Endereço lógico

Endereço físico/línear

O endereço lógico pode tomar um

dos seguintes formatos:

<segmento>:[<deslocamento>]

<segmento>:[<offset>]

<segmento>:[<displacement>]

O endereço físico/linear pode ser

determinado da seguinte forma:

Segmento *16

+ deslocamento

Endereço físico/línear

43

9

Estrutura interna do CPU (microprocessador) 8086

Segmentos de memória

Sobreposição de segmentos

ES – Extra segment

Inicio

52B90h

52B90

+FFFFh

Fim

62B8Fh

SS – Stack segment

62B8F

Inicio

5D270h

5D270

+FFFFh

Fim

6D26Fh

44

Estrutura interna do CPU (microprocessador) 8086

Segmentos de memória

Endereços dos segmentos

45

10

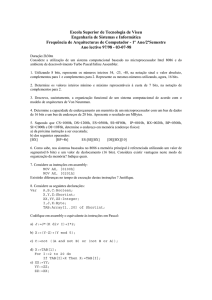

Instruções do CPU 8086

Formato geral

<OPERAÇÃO>

[<DESTINO>] , [<ORIGEM>]

Codificação de programas em Assembly

• Cada operação é representada por uma mnemónica

• Os operandos são representados por identificadores

Exemplo:

MOV AX,BX

• MOV – mnemónica que representa a operação (cópia).

• AX – Registo interno do CPU (Destino)

• BX – Registo interno do CPU (Origem)

A instrução copia o conteúdo do registo BX para o registo AX.

46

Instruções do CPU 8086

Código máquina

• Codificação binária das instruções com base em operação + operandos (“OP-CODE”)

• De acordo com o tipo de instrução, a sua codificação pode ocupar vários bytes

Exemplo:

MOV AX,CX

• 89h codifica a operação MOV

• C1h codifica os operandos AX,CX

Assim sendo, se efectuamos uma codificação em linguagem assembly esta tem

de ser “traduzida” para código máquina. Esse compilador chama-se

ASSEMBLER.

47

11

Instruções do CPU 8086

Tipo de instruções quanto ao número de operandos

• 2 operandos

Exemplo:

MOV AX,CX

Copia o conteúdo de CX para AX; AX:=CX;

• 1 operando

Exemplo:

INC AX Incrementa o conteúdo de AX;

AX:=AX+1;

• 0 operandos

Exemplo:

CBW

Converte o byte AL para a word AX;

48

Instruções do CPU 8086

Tipos de instruções de acordo com a função que realizam

Instruções Aritméticas

Instrução

Descrição

Bits de estado

afectados

ADD

a, b

a←a+b

Z, C, O, N

ADC

a, b

a←a+b+C

Z, C, O, N

NEG

a

a←–a

Z, C, O, N

SUB

a, b

a←a–b

Z, C, O, N

SBB

a, b

a←a–b–C

Z, C, O, N

MUL

b

ax ← ax * b

Z, C, O, N

DIV

b

a←a/b

Z, C, O, N

INC

a

a←a+1

Z, C, O, N

DEC

a

a←a–1

Z, C, O, N

49

12

Instruções do CPU 8086

Tipos de instruções de acordo com a função que realizam

Instruções lógicas

AND

a, b

ai ← ai ∧ bi (i ∈ 0..N-1)

OR

a, b

ai ← ai ∨ bi (i ∈ 0..N-1)

XOR

a, b

ai ← ai ⊕ bi (i ∈ 0..N-1)

COM

a

ai ← ai (i ∈ 0..N-1)

a

aN-1

aN-2

...

a2

a1

a0

b

bN-1

bN-2

...

b2

b1

b0

∧, ∨

ou ⊕

∧, ∨

ou ⊕

∧, ∨

ou ⊕

∧, ∨

ou ⊕

∧, ∨

ou ⊕

50

Instruções do CPU 8086

Tipos de instruções de acordo com a função que realizam

Instruções de deslocamento

SHL

a, n

aN-1

n * [ai+1 ß ai (i ∈ 0..N-2); a0 ß 0]

...

SHR

a, n

n * [ai ß ai+1 (i ∈ 0..N-2); aN-1 ß 0]

SAR

a, n

n * [ai ß ai+1 (i ∈ 0..N-2); aN-1 ß aN-1]

0

aN-1

aN-1

...

0

a0

a0

51

13

Instruções do CPU 8086

Tipos de instruções de acordo com a função que realizam

Instruções de rotação

ROL

a, n

n * [ai+1 ß ai (i ∈ 0..N-2); a0 ß aN-1]

aN-1

...

a0

a, n n * [ai ß ai+1 (i ∈ 0..N-2); aN-1 ß a0]

ROR

aN-1

...

a0

52

Instruções do CPU 8086

Tipos de instruções de acordo com a função que realizam

Instruções de rotação com carry

RCL

a, n

C

RORC

aN-1

a, n

C

n * [ai+1 ß ai (i ∈ 0..N-2); a0 ß C; C ß aN-1]

...

a0

n * [ai ß ai+1 (i ∈ 0..N-2); aN-1 ß C; C ß a0]

aN-1

...

a0

53

14

Modos de endereçamento no 8086

Endereçamento por registo

Este tipo de endereçamento acontece quando os operandos das

instruções são registos do CPU.

Exemplos:

MOV AX, BX

MOV DL, AL

Utilização de registos de segmentos

A utilização de registos de segmento tem algumas restrições:

• O registo de segmento CS (“code segment”) não pode ser utilizado

como operando de destino. A instrução MOV CS, AX é incorrecta.

• Apenas um dos operandos pode ser um registo de segmento. A

instrução MOV DS, CS é incorrecta.

54

Modos de endereçamento no 8086

Endereçamento em memória

Endereçamento imediato

Este tipo de endereçamento acontece quando o operando está contido na

própria instrução.

Exemplo:

MOV CX,3064h

IP

mm

mm

CS

nn

nn

CX

30

64

Instrução CS:[IP]

nnnn0

+ mmmm

p p p pm

30h

64h

B9h

ppppm+2

ppppm+1

ppppm

55

15

Modos de endereçamento no 8086

Endereçamento em memória

Endereçamento directo

Este tipo de endereçamento acontece quando a instrução fornece o

endereço em memória do operando

Exemplo:

AX

MOV AL,[001Fh]

YY

YY

Segmento

de Dados

00h

1Fh

A0h

Segmento

de Código

DS:[001Fh]

DS

Instrução CS:[IP]

56

Modos de endereçamento no 8086

Endereçamento em memória

Endereçamento Indirecto

Este tipo de endereçamento acontece quando o endereço do operando é obtido

por:

Registo de base: [BX] ou [BP]

Registo de base + deslocamento:

[BX+displ] ou [BX] displ ou displ [BX]

ou …

Registo de indexação: [SI] ou [DI]

Registo de indexação + deslocamento: [SI+displ] ou [DI+ displ] ou ….

Registo de base + registo de indexação:

[BX+DI] ou [BP+SI] ou …

Registo de base + indexação + deslocamento:

[BX+SI+ disp] ou ...

57

16

Modos de endereçamento no 8086

Observações:

Existe a possibilidade de fazermos referência explícita ao registo de segmento,

conhecido por “Segment override”. Como exemplo podemos referir a instrução

MOV AX, ES:[BX].

Para instruções com dois operandos não é possivel utilizar endereçamento em

memória simultaneamente no operando origem e no operando destino.

Exemplo:

MOV [BX], [BP+001Fh]

incorrecto

MOV AX, [BP+001Fh]

MOV [BX], AX

Correcto

Utilização das directivas byte ptr e/ou word ptr para endereçamento em memória

MOV [BX], 10

estamos perante um tipo de endereçamento

(indirecto), (imediato). O valor é armazenado em

memória como 8 ou 16 bits??

58

Modos de endereçamento no 8086

Observações:

Combinações admitidas no formato destino,origem

registo, registo

registo, imediato

registo, directo

registo, indirecto

directo, imediato

directo, registo

indirecto, registo

indirecto, imediato

Combinações não admitidas no formato destino, origem

imediato, <qualquer outro tipo>

<end. em memoria>, <end. em memoria>

59

17