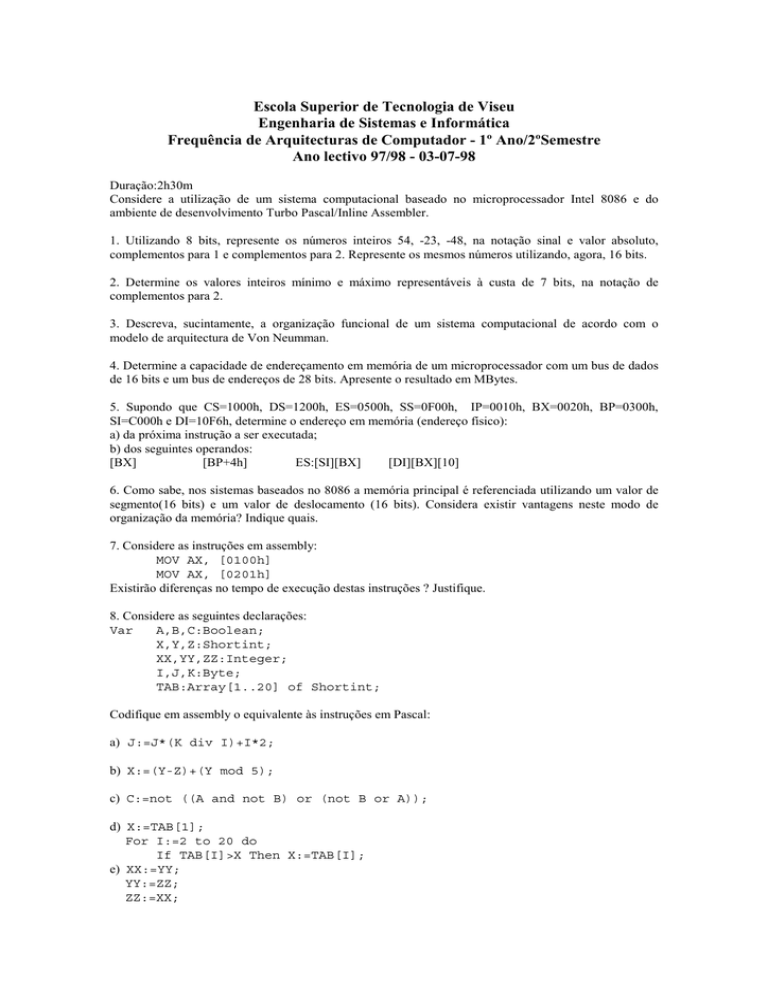

Escola Superior de Tecnologia de Viseu

Engenharia de Sistemas e Informática

Frequência de Arquitecturas de Computador - 1º Ano/2ºSemestre

Ano lectivo 97/98 - 03-07-98

Duração:2h30m

Considere a utilização de um sistema computacional baseado no microprocessador Intel 8086 e do

ambiente de desenvolvimento Turbo Pascal/Inline Assembler.

1. Utilizando 8 bits, represente os números inteiros 54, -23, -48, na notação sinal e valor absoluto,

complementos para 1 e complementos para 2. Represente os mesmos números utilizando, agora, 16 bits.

2. Determine os valores inteiros mínimo e máximo representáveis à custa de 7 bits, na notação de

complementos para 2.

3. Descreva, sucintamente, a organização funcional de um sistema computacional de acordo com o

modelo de arquitectura de Von Neumman.

4. Determine a capacidade de endereçamento em memória de um microprocessador com um bus de dados

de 16 bits e um bus de endereços de 28 bits. Apresente o resultado em MBytes.

5. Supondo que CS=1000h, DS=1200h, ES=0500h, SS=0F00h, IP=0010h, BX=0020h, BP=0300h,

SI=C000h e DI=10F6h, determine o endereço em memória (endereço físico):

a) da próxima instrução a ser executada;

b) dos seguintes operandos:

[BX]

[BP+4h]

ES:[SI][BX]

[DI][BX][10]

6. Como sabe, nos sistemas baseados no 8086 a memória principal é referenciada utilizando um valor de

segmento(16 bits) e um valor de deslocamento (16 bits). Considera existir vantagens neste modo de

organização da memória? Indique quais.

7. Considere as instruções em assembly:

MOV AX, [0100h]

MOV AX, [0201h]

Existirão diferenças no tempo de execução destas instruções ? Justifique.

8. Considere as seguintes declarações:

Var

A,B,C:Boolean;

X,Y,Z:Shortint;

XX,YY,ZZ:Integer;

I,J,K:Byte;

TAB:Array[1..20] of Shortint;

Codifique em assembly o equivalente às instruções em Pascal:

a) J:=J*(K div I)+I*2;

b) X:=(Y-Z)+(Y mod 5);

c) C:=not ((A and not B) or (not B or A));

d) X:=TAB[1];

For I:=2 to 20 do

If TAB[I]>X Then X:=TAB[I];

e) XX:=YY;

YY:=ZZ;

ZZ:=XX;

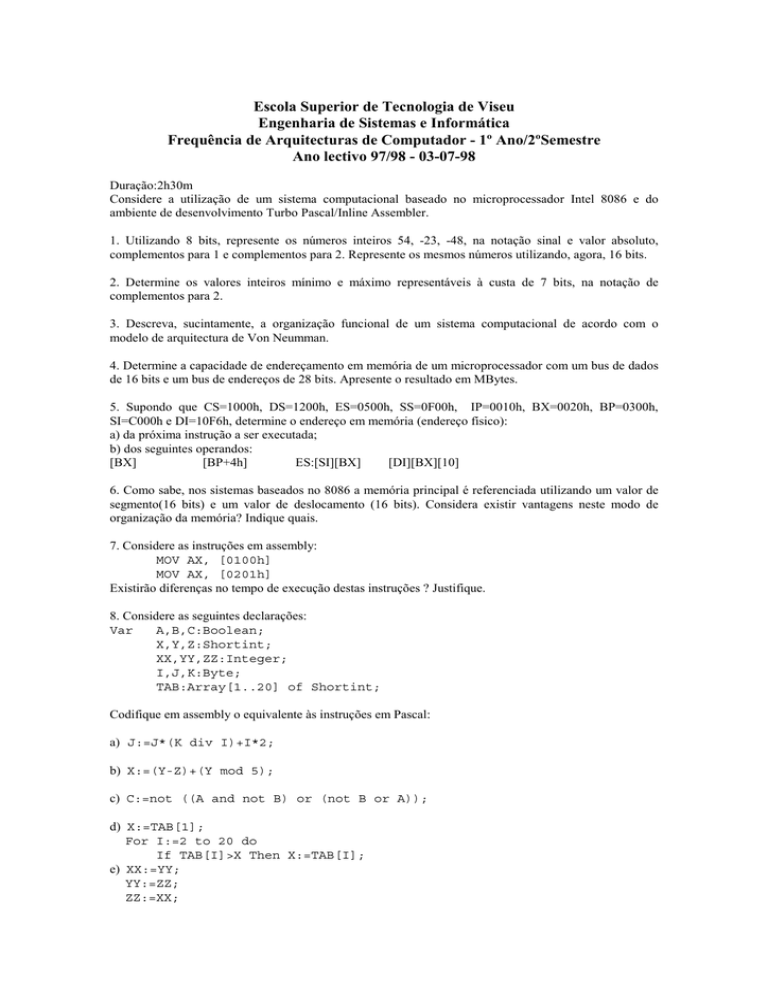

9) Considere um procedimento identificado por PROC1, com a seguinte lista de parâmetros formais:

-Parâmetro da classe valor do tipo char;

-Parâmetro da classe variável do tipo integer;

-Parâmetro da classe valor do tipo integer;

a) Apresente o cabeçalho do procedimento considerando o tipo de chamada “intra-segment “ (“near call”).

b) Supondo que são declaradas duas variáveis locais do tipo integer, descreva a organização da pilha

aquando da invocação deste procedimento. Indique como referenciar os parâmetros e as variáveis locais.

c) Escreva o código assembly que invoca este procedimento com a seguinte lista de parâmetros reais:

‘A’, X, -10 (X é uma variável do tipo integer).

d) Neste procedimento utiliza-se a pilha do sistema para a passagem de parâmetros. Que outros

mecanismos conhece para a passagem de parâmetros?

10) Escreva um subprograma em assembly que ordene uma tabela de registos definida por:

Type RTAB= Record

X,Y:Shortint;

End;

TTAB=Array[1..10] of RTAB;

A ordenação deverá ser por ordem crescente do campo X

11) Escreva um função que, sendo dado um número de bit (0..15) e uma variável do tipo integer, devolva

o valor armazenado na variável com o bit correspondente complementado. Por exemplo, se o valor da

variável é 0110 0100 1001 0011b e o número do bit é 8, o valor devolvido pela função deverá ser 0110

0101 1001 0011b.

Considere a seguinte declaração:

Function CompValor(N:Byte;Var X:Integer):Integer; Far; Assembler;

12) O interface de uma unidade de I/O, cujo endereço base (word) está armazenado em 0040h:0020h, é

constituído por um registo de dados (endereço base + 0h) e um registo de estado (endereço base + 1h). A

escrita no registo de dados permite o envio de um byte para o periférico. O periférico indica se pode ou

não receber novos dados através do bit B4 do registo de estado.

Registo de estado

B7 B6 B5 B4 B3 B2 B1 B0

X

X

X

1/0

X

X

X

X

B4=0 => o periférico pode receber dados

B4=1 => o periférico não pode receber dados

Escreva um subprograma em assembly que envie uma cadeia de caracteres para o periférico.

13) Descreva, de forma sucinta, os mecanismos de transferência de dados entre as unidades de I/O e o

CPU ou memória.