UNIVERSIDADE FEDERAL DE SANTA CATARINA

CENTRO TECNOLÓGICO

DEPARTAMENTO DE INFORMÁTICA E ESTATÍSTICA

Curso de Ciências da Computação

SEMINÁRIO ASSEMBLY:

Arquitetura PIC

DOUGLAS DAL POZZO

DIEGO VITTI

Florianópolis – Santa Catarina

Fevereiro – 2007

UNIVERSIDADE FEDERAL DE SANTA CATARINA

CENTRO TECNOLÓGICO

DEPARTAMENTO DE INFORMÁTICA E ESTATÍSTICA

Curso de Ciências da Computação

SEMINÁRIO ASSEMBLY:

Arquitetura PIC

Este trabalho destina-se a cumprir

requisito de avaliação da disciplina

INE5309 – Programação de sistemas,

turma 0432 de 2006.2 ministrada pelo

professor Dr. Antônio Augusto Fröhlich.

DOUGLAS DAL POZZO

DIEGO VITTI

Florianópolis – Santa Catarina

Fevereiro – 2007

Histórico

Os micro-controladores PIC originaram-se em 1975 a partir do projeto de um

processador de 16 bits da General Instrument's Microelectronics Division. Esse

processador, denominado CP1600, apresentava baixa performance de I/O e então essa

mesma companhia desenvolveu o primeiro micro-controlador PIC (PIC1650) para ser

usado em conjunto com o processador CP1600, aumentando a performance desse

processador com a passagem do controle de tarefas de I/O para o micro-controlador

PIC.

Em 1985 a

General Instrument's vendeu seu setor de microeletrônica. O novo

fabricante desativou quase todos os projetos que estavam então ultrapassados. No

entanto, os micro-controladores PIC foram renovados e continuaram a evoluir e hoje, a

Microchip Technology, atual fabricante dos micro-controladores PIC, oferece uma

ampla variedade de modelos.

O Que São Micro-controladores

Micro-controlador é um componente cujo núcleo possui os mesmos blocos funcionais

de um microprocessador. No entanto, sua aplicação é um pouco mais geral. Para isso,

no mesmo chip são embutidos interfaces de comunicação com o mundo externo. Nesse

sentido, um micro-controlador é um sistema completo, com sistema de memória,

sistema de entrada e saída, tudo isso em um único chip.

Caracterização da Arquitetura de Micro-controladores PIC

A arquitetura PIC possui uma família de micro-controladores de 12, 14 e 16 bits. É uma

arquitetura RISC baseada em outra arquitetura denominada arquitetura Harvard.

A arquitetura Harvard surgiu a partir da necessidade de melhorar o desempenho dos

micro-controladores. Para isso, ela define o uso de duas memórias separadas: uma

memória de dados e outra memória de programa (instruções). Essas duas memórias são

conectadas por barramentos distintos e isso permite o uso de diferentes tamanhos de

palavras para dados e instruções.

Diagrama de blocos da arquitetura Harvard e da arquitetura von-Neumann. A arquitetura Harvard possui

memórias para dados e instruções separadas o que possibilita diferentes tamanhos de barramentos. Isso

permite, no caso dos PICs, que todas as instruções ocupem uma única word de 14 bits, por exemplo,

enquanto os dados ocupem somente 8 bits.

Por pertencer a arquitetura RISC, os micro-controladores PIC apresentam instruções

simples. Isso implica em maior código para a programação de funções mais avançadas.

Em geral esses micro-controladores apresentam um conjunto entre 30 e 40 instruções.

Algumas aplicações dos Micro-controladores PIC

Os micro-controladores possuem larga aplicação em dispositivos eletrônicos que

requerem algum tipo de controle digital. Máquinas de lavar roupas, microondas,

telefones, ar-condicionado são alguns exemplos. Isso acontece pelas suas características

como simplicidade, facilidade de programação, baixo preço.

Diagrama de blocos do PIC16F84

Análise comparativa: arquitetura PIC vs. arquitetura MIPS

Para fins de comparação da arquitetura PIC com a arquitetura MIPS será utilizado o

micro-controlador PIC16F84 e o processador MIPS-RS2000. Cada implementação

específica de cada uma dessas arquiteturas possuem pequenas mudanças que não irá

interferir de modo considerável nessa comparação.

Número de instruções

PIC

MIPS-32

Arquitetura

PIC

35 instruções

RISC – Harvard

Um caminho de dados de 14 bits para instruções

Um caminho de dados de 8 bits para dados

65 instruções

MIPS

(contém instruções para operações em ponto

RISC –flutuante)

Von Neumann

Um único caminho de dados de 32 bits para

dados e instruções.

Modos de endereçamento

PIC

MIPS-32

3 modos de endereçamento

Endereçamento direto

Endereçamento indireto

Endereçamento relativo

5 modos de endereçamento:

- endereçamento em registrador

- endereçamento de base ou deslocamento

- endereçamento imediato

- endereçamento relativo ao PC

- endereçamento pseudo-indireto

Registradores / memória

PIC

MIPS-32

12 registradores

32 registradores de uso geral

memória acessada via instruções de

transferência de dados

Suporte a procedimentos

1. Parâmetros são carregados nos registradores de passagem de 1. Parâmetros são carregados nos registradores de passagem de

parâmetros

parâmetros

CALL <endereço do início do procedimento>

1. Endereço de retorno (PC + 1) é salvo no topo da pilha.

2. Endereço do início do procedimento é carregado em PC.

...

execução

...

resultado é colocado em um endereço para retorno

...

RETURN

1. O elemento do topo da pilha é retirado e carregado em no PC

jal <endereço do início do procedimento>

1. Endereço de retorno (PC + 1) é salvo em $ra.

2. Endereço do início do procedimento é carregado em PC.

...

execução

...

resultado é colocado em registrador de retorno

...

jr $ra

1. O endereço armazenado em $ra é carregado em no PC

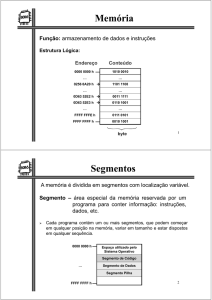

Organização da Memória

A memória do micro-controlador PIC16F84 é dividida em 2 blocos: memória de

programa e memória de dados. Pela arquitetura Harvard, cada memória tem o seu

próprio barramento o que possibilita que ambas sejam acessadas dentro do mesmo ciclo

do relógio.

A memória de dados ainda pode ser dividida em 2 blocos: General Purpouse RAM

(GPR) e Special Function Registers (SFR). A memória denominada SFR é utilizada

para o controle do dispositivo. A memória GPR é usada para armazenamento das

variáveis e constantes do programa. Esta memória também contém a memória de dados

EEPROM (Electronically Erasable Programmable Read-Only Memory ) que mantém

seu estado mesmo quando o dispositivo estiver desligado e é acessada indiretamente

através de registradores de uso específico.

Organização da Memória de Dados

A memória de dados é dividida em dois blocos. O primeiro é a área de registro

de função especial (SFR) , enquanto o segundo é a área do registro de propósito

geral(GPR).

O SFR controla a operação do dispositivo.

Blocos de memória de dados são dispostos para ambos, a área de SFR e a área

de GPR.

A área de GPR é alocada para deixar mais que 116 bytes de RAM de

propósito geral. As áreas alocadas do SFR são para os registradores que controlam as

funções periféricas. Alocações requerem o uso do controle para seleção do bank. Esses

controles são localizados no registro de STATUS.

Figura abaixo mostra o mapa de organização da memória de dados.

Instruções MOVWF e MOVF podem mudar valores do registro W para qualquer

local no arquivo de registro (“FF”), e vice-versa.

A memória de dados pode ser acessada diretamente usando o endereço absoluto

de cada arquivo do registro ou indiretamente através do FILE SELECT

REGISTER(FSR). Endereçamento indireto usa o valor presente do RPO bit para acesso

nas áreas alocadas da memória de dados

ARQUIVOS DO REGISTRO DE PROPOSITO GERAL

Cada registro de propósito geral (GPR) tem 8 bits de tamanho e é acessado

diretamente ou indiretamente pelo FSR( seção 2.5).

Os endereços do GPR em Bank 1 são mapeados para endereços em Bank 0.

como exemplo, o local de endereço 0Ch ou 8Ch vão acessar o mesmo GPR.

REGISTROS DE FUNÇÕES ESPCECIAIS

O registro de função especial é usado pelo CPU e funções periféricas para

controlar a operação do dispositivo. Esses registros são de RAM estática.

Os registros de funções especiais podem ser classificados em duas classes, o

núcleo e periférico.

STATUS REGISTER

O registro de STATUS contém a posição aritmética da ALU,

RESET e a seleção de BANK para a memória de dados.

a posição de

O registro de STATUS pode ser o destino para qualquer instrução. Se o registro

de STATUS é a destino para uma instrução que afeta o Z, DC ou bits de C, então o

write para esses três bits é desabilitado.

Esses bits são programados ou zerados de acordo com a lógica do dispositivo.

Alem disso, os TO E PD bits não são writable. Portanto o resultado de uma

instrução com o registro de STATUS como destino pode ser diferente do que se

esperava.

Por exemplo, CLRF STATUS, vai limpar os três bits de cima e colocar o Z bit.

Isso deixa o registro de STATUS como ooou u1uu ( onde u = não mudado).

Só as instruções de BCF, BSF, SWAPF E MOVWF devem ser usados para

alterar o registro de STATUS, porque essas instruções não afetam qualquer bit de

STATUS.

PCL E PCLATH

O contador do programa especifica os endereços da instrução para localizar a

execução. O PC é 13bits de tamanho, o byte menor é chamado do registro de PCL. Esse

registro pode ser lido e escrito. O byte maior é chamado do registro de PCH. Esse

registro contem o PC<12;8> BITS.

STACK

A pilha contém o endereço de retorno da execução

A área de dados da pilha não faz parte do programa e o ponteiro da pilha não

pode ser lido ou escrito. O PC é deslocado na pilha quando uma instrução de chamada

é executada.

A pilha é deslocada no evento de RETURN, TETLW ou em uma

execução de instrução de RETFIE.

Depois de a pilha ter sido deslocada oito vezes, o nono deslocamento

sobrescrever o valor que foi armazenado no primeiro deslocamento.

deslocamento sobrescrever o segundo deslocamento e assim por diante.

O décimo

Conjunto de Instruções

As instruções da família PIC16CXX são formadas por words de 14 bits

divididas em um OPCODE que identifica a instrução e um ou mais operandos sobre os

quais a instrução irá operar. As instruções são classificadas em 3 tipos:

Byte-Oriented:

Para as instruções orientadas a bytes, f representa um file register e 'd' representa

o endereço de destino. O file register especifica qual registrador será usado pela

instrução.

Mnemonic, Operands

ADDWF

ANDWF

CLRF

CLRW

COMF

DECF

DECFSZ

INCF

INCFSZ

IORWF

MOVF

MOVWF

f, d

f, d

f

f, d

f, d

f, d

f, d

f, d

f, d

f, d

f

NOP

RLF

RRF

SUBWF

SWAPF

XORWF

f, d

f, d

f, d

f, d

f, d

Bit-oriented:

14-Bit Opcode

Status

MSb

LSb Affected

BYTE-ORIENTED FILE REGISTER OPERATIONS

Add W and f

1

0 0 0111 dfff

ffff

C,DC,Z

AND W with f

1

0 0 0101 dfff

ffff

Z

Clear f

1

0 0 0001 lfff

ffff

Z

Clear W

1

0 0 0001 0xxx xxxx

Z

Complement f

1

0 0 1001 dfff

ffff

Z

Decrement f

1

0 0 0011 dfff

ffff

Z

Decrement f, Skip if 0

1 (2)

0 0 1011 dfff

ffff

Increment f

1

0 0 1010 dfff

ffff

Z

Increment f, Skip if 0

1 (2)

0 0 1111 dfff

ffff

Inclusive OR W with f

1

0 0 0100 dfff

ffff

Z

Move f

1

0 0 1000 dfff

ffff

Z

Move W to f

1

0 0 0000 lfff

ffff

0 0 0000 0xx0

No Operation

1

0000

Rotate Left f through Carry

1

0 0 1101 dfff

ffff

C

Rotate Right f through Carry

1

0 0 1100 dfff

ffff

C

Subtract W from f

1

0 0 0010 dfff

ffff

C,DC,Z

Swap nibbles in f

1

0 0 1110 dfff

ffff

Exclusive OR W with f

1

0 0 0110 dfff

ffff

Z

Description

Cycles

Notes

1,2

1,2

2

1,2

1,2

1,2,3

1,2

1,2,3

1,2

1,2

1,2

1,2

1,2

1,2

1,2

Para as instruções orientadas a bit, 'b' representa a posição de um bit de um

campo do file register.

Mnemonic, Operands

BCF

BSF

BTFSC

BTFSS

f, b

f, b

f, b

f, b

14-Bit Opcode

MSb

LSb

BIT-ORIENTED FILE REGISTER OPERATIONS

Bit Clear f

1

0 1 00bb bfff

ffff

Bit Set f

1

0 1 01bb bfff

ffff

Bit Test f, Skip if Clear

1 (2)

0 1 10bb bfff

ffff

Bit Test f, Skip if Set

1 (2)

0 1 11bb bfff

ffff

Description

Cycles

Status

Affected

Notes

1,2

1,2

3

3

Literal and Control Instructions:

Mnemonic, Operands

ADDLW

ANDLW

CALL

CLRWDT

GOTO

IORLW

MOVLW

RETFIE

RETLW

RETURN

SLEEP

SUBLW

XORLW

k

k

k

k

k

k

k

k

k

14-Bit Opcode

Status

MSb

LSb Affected

BIT-ORIENTED FILE REGISTER OPERATIONS

Add literal and W

1

1 1 111x kkkk kkkk

C,DC,Z

AND literal with W

1

1 1 1001 kkkk kkkk

Z

Call subroutine

2

1 0 0kkk kkkk kkkk

Clear Watchdog Timer

1

0 0 0000 0110 0100 TO,PD

Go to address

2

1 0 1kkk kkkk kkkk

Inclusive OR literal with W

1

1 1 1000 kkkk kkkk

Z

Move literal to W

1

1 1 00xx kkkk kkkk

Return from interrupt

2

0 0 0000 0000 1001

Return with literal in W

2

1 1 01xx kkkk kkkk

Return from Subroutine

2

0 0 0000 0000 1000

Go into standby mode

1

0 0 0000 0110 0011 TO,PD

Subtract W from literal

1

1 1 110x kkkk kkkk

C,DC,Z

Exclusive OR literal with W

1

1 1 1010 kkkk kkkk

Z

Description

Cycles

Notes

Tabela : Descrição dos operandos das instruções.

O Algoritmo de Multiplicação

MULT

MULT

CLRF RESULTADO

LOOP

MOVF TEMPX,W

BTFSC TEMPY,0

ADDWF RESULTADO

BCF STATUS,C

RRF TEMPY,F

BCF STATUS,C

RLF TEMPX,F

MOVF TEMPY,F

BTFSS STATUS,Z

GOTO MULT

RETURN

Execução do algoritmo

MOVF

MOVWF

MOVF

MOVWF

CALL

MOVF

MOVWF

x,W

TEMPX

y,W

TEMPY

MULT

RESULTADO,W

z

;

;

;

;

;

;

;

;

;

;

;

clear file RESULTADO

endereço simbólico do inicio da subrotina

mover o conteúdo do endereço TEMPX para W

Bit test TEMPY, skip if 1th bit is clear

RESULT = W + f

bit clear STATUS, C = clear the carry flag

rotate right file

bit clear STATUS

rotate left file and store itself

mover o conteúdo do endereço TEMPY para W

bit test, skip if clear