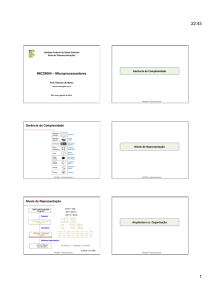

Microprocessadores

Arquitectura Geral de Microprocessador

António M. Gonçalves Pinheiro

Departamento de Física

Universidade da Beira Interior

Covilhã - Portugal

[email protected]

Microprocessadores

Modelo de von Neuman

Barramento de Endereços

µProcessador

Memória

Entrada/Saída

Barramento de Dados

Sinais de Controlo

Universidade da Beira Interior

Microprocessadores

MUX

Estrutura de µProcessadores

A

B

M2

M1

M0

ALU

S1

S0

R WR

F

FLAGS

Fz

Fov

Fs

R1

R2

MUX

DEMUX

R0

WF

R3

D1

D0

Universidade da Beira Interior

Microprocessadores

MUX

Estrutura de µProcessadores

A

B

M2

M1

M0

ALU

S1

S0

R WR

F

WF

R1

R2

MUX

DEMUX

R0

WD RD

FLAGS

Fz

Fov

Fs

R3

D1

D0

"Buffer"

de

dados

Barramento

de Dados

Universidade da Beira Interior

Microprocessadores

Estrutura de µProcessadores

WSP RSP

"STACK

POINTER"

A

Contador

de

Programa

B

M2

M1

M0

ALU

S1

S0

R WR

WE RE IE

MUX

MUX

WPC RPC

Barramento

de Endereços

F

Registo de

Endereço

WF

R1

R2

MUX

DEMUX

R0

WD RD

FLAGS

Fz

Fov

Fs

R3

D1

D0

"Buffer"

de

dados

Barramento

de Dados

Universidade da Beira Interior

Microprocessadores

Estrutura de µProcessadores

WSP RSP

"STACK

POINTER"

A

Contador

de

Programa

B

M2

M1

M0

ALU

S1

S0

R WR

WE RE IE

MUX

MUX

WPC RPC

Barramento

de Endereços

F

Registo de

Endereço

WF

R1

R2

MUX

DEMUX

R0

WD RD

FLAGS

Fz

R3

Fov

Fs

"Buffer"

de

dados

D1

D0

Controlador

CK

M0 D0 S0 R

Registo

de Instrucção

Barramento

de Dados

WI

RSP RE RDRPC

M1 D1 S1 WR WSP WE WD W PC

M2

WF

WI

IE

Universidade da Beira Interior

Microprocessadores

ALU - Unidade Lógica e Aritmética

M2 M1 M0

0

0

0

0

0

1

0

1

0

0

1

1

1

0

0

1

0

1

1

1

0

1

1

1

O PERAÇÃO

A+B

A-B

A+1

A-1

A AND B

A OR B

A EXOR B

NOT (A)

Universidade da Beira Interior

Microprocessadores

Instrucções

T RÊS G RUPOS :

- O PERAÇÕES DE M OVIMENTO DE DADOS

- O PERAÇÕES A RITMÉTICAS E L ÓGICAS

- O PERAÇÕES DE C ONTROLO DE P ROGRAMA

E XEMPLO : I NSTRUCÇÕES DE 8 BITS :

I7

0

1

1

I6

0

1

T IPO DE O PERAÇÃO

A RITMÉTICAS E L ÓGICAS

M OVIMENTO DE DADOS

C ONTROLO DE P ROGRAMA

Universidade da Beira Interior

Microprocessadores

Instrucções

O PERAÇÕES DE M OVIMENTO DE DADOS

I7 I6 I5 I4 I3 I2 I1 I0 M NEMÓNICA O PERAÇÃO

1 0 0 0 s1 s0 d1 d0 MOV Rd ,Rs M OVE C ONTEÚDO DE Rs PARA Rd

C ARREGA Rd COM CONTEÚDO DO

1 0 1 0 0 0 d1 d0

LD Rd

1 0 1 1 0

0 s1 s 0

1 0 0 1 0

1 s1 s0 MOV RE ,Rs

1 0 0 1 1

0 s1 s 0

1 0 0 1 1

1 s1 s0 MOV PC,RE

ST Rs

MOV SP,Rs

ENDEREÇO

A RMAZENA Rs NO ENDEREÇO

M OVE Rs PARA O R EGISTO DE EN -

DEREÇO

M OVE Rs PARA O “S TACK P OINTER "

M OVE R EGISTO DE ENDEREÇO PARA

O

C ONTADOR DE P ROGRAMA

Universidade da Beira Interior

Microprocessadores

Instrucções

O PERAÇÕES A RITMÉTICAS E L ÓGICAS

I7

0

0

0

0

0

0

0

0

0

I6

0

0

0

0

0

1

1

1

1

I5

0

1

1

0

0

1

1

0

0

I4

0

0

1

0

1

0

1

0

1

I3

0

s1

s1

1

1

s1

s1

s1

1

I2

0

s0

s0

1

1

s0

s0

s0

1

I1

0

d1

d1

d1

d1

d1

d1

d1

d1

I0 M NEMÓNICA

0

NOP

d0 ADD Rd ,Rs

d0 SUB Rd ,Rs

d0

INC Rd

DEC Rd

d0

d0 AND Rd ,Rs

d0 OR Rd ,Rs

d0 EXOR Rd ,Rs

d0

NOT Rd

O PERAÇÃO

“N O O PERATION "

Rd ← Rd + Rs

Rd ← Rd - Rs

Rd ← Rd + 1

Rd ← Rd - 1

Rd ← Rd AND Rs

Rd ← Rd OR Rs

Rd ← Rd EXOR Rs

Rd ← NOT(Rd )

Universidade da Beira Interior

Microprocessadores

Instrucções

O PERAÇÕES DE C ONTROLO DE P ROGRAMA

I7

1

1

1

1

1

I6

1

1

1

1

1

I5

0

0

0

0

0

I4

0

0

0

0

1

I3

0

0

1

1

0

I2 I1 I0 M NEMÓNICA

0 0 0

JMP

C2 C1 C0

J CC

0 0 0

CALL

C2 C1 C0

C CC

0 0 0

RET

O PERAÇÃO

S ALTO INCONDICIONAL

S ALTO CONDICIONAL

ROTINA INCONDICIONAL

ROTINA CONDICIONAL

R ETORNO DE ROTINA

Universidade da Beira Interior

Microprocessadores

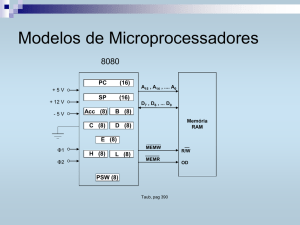

Arquitecturas de Microprocessadores

Modelo de Von Neumann

Barramento de Endereços

µProcessador

Memória

Entrada/Saída

Barramento de Dados

Sinais de Controlo

Universidade da Beira Interior

Microprocessadores

Arquitecturas de Microprocessadores

Arquitectura Geral

Interligação

Barramento

de Endereços

Ponteiro do Stack

Contador de Programa

Registo de Endereço

Interligação

Barramento

de Dados

Registo de Instrução

Registos

Gerais

Unidade

de

Controlo

ALU

Registo de Flags

Universidade da Beira Interior

Microprocessadores

Arquitecturas de Microprocessadores

Arquitectura Geral

Organização

da Memória

Estrutura

de Dados

Linguagem de

Alto Nível

Variáveis

com Nome

Microprocessador

“Array"

Linear

Multidimensionais

Unidimensionais

Programação

- Rotinas e Retornos

- Parâmetros

- Memória Dinâmica

Operações de “Stack"

Tipo

de Memória

Dados 6= Instrucção

Dados = Instrucção

Normalmente feitas para superar o Semantic Gp

Universidade da Beira Interior

Microprocessadores

Arquitecturas de Microprocessadores

Arquitectura Geral

Arquitectura e EficiÊncia de Execução

Tipos de Dados

• +/− idênticos no Microprocessador e na Linguagem de Alto Nível

Modos de Endereçamento

• Definem mecansimos para aceder aos dados

• Podem proporcionar mecanismos eficientes para mapear estruturas de dados complexas

Conjunto de Instrucções

Podem aumentar eficiência de duas formas:

• CISC - Complex Instruction Set Computer

• RISC - Reduced Instruction Set Computer

Universidade da Beira Interior

Microprocessadores

Ciclos de Instrucção

Ciclo Básico de Instrucção

Início

Ciclo

de Busca

Ciclo de

Execução

Halt

Universidade da Beira Interior

Microprocessadores

Ciclos de Instrucção

Ciclo Básico de Instrucção com Interrupções

Início

Ciclo

de Busca

Não

Processa

Interrupção

Sim

Interrupção?

Ciclo de

Execução

Halt

Universidade da Beira Interior

Microprocessadores

FPU - “Floating Point Unit”

Representação de Números Reais

Ponto Fixo

Ponto Flutuante

1

Parte

Inteira

Parte

Decimal

x(10)2

Sinal Mantissa

Expoente

Underflow Número com valor absoluto muito pequeno diferente de zero que não pode ser representado.

Overflow Número com valor absoluto muito grande que não pode ser representado.

FPU - “Floating Point Unit”

Circuito que se destina a fazer operações com números em vírgula flutuante.

Universidade da Beira Interior

Microprocessadores

FPU - “Floating Point Unit”

Norma do IEEE 754-1985

Número

de bits

Precisão Simples

32

Precisão Dupla

64

Nome

Sinal Mantissa Expoente Polarização

1

1

23

52

8

11

127

1023

Valor representado em decimal:

(−1)Sinal ×

1+

p−1

X

!

Mantissa(n) × 2−n

× 2Expoente-Polarização

n=1

Formato:

Sinal

Expoente

Mantissa

Casos especiais:

Tipo

Expoente Mantissa

Zero

00...000 00...000

Infinito

11...111 00...000

NaN

11...111

6= 0

Num. não normalizado 00...000

6= 0

Universidade da Beira Interior