UNIVERSIDADE FEDERAL DO RIO GRANDE DO NORTE

CENTRO DE TECNOLOGIA

PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA

Um sistema para simular o comportamento de bancos

trifásicos de reguladores de tensão usados em sistemas de

distribuição de energia elétrica.

Jânio Mendonça Júnior

Orientador: D.Sc. José Alberto Nicolau de Oliveira

NATAL - RN

MARÇO/2010

JÂNIO MENDONÇA JÚNIOR

Um sistema para simular o comportamento de bancos

trifásicos de reguladores de tensão usados em sistemas de

distribuição de energia elétrica.

Dissertação de mestrado submetida ao programa de Pós-Graduação em Engenharia

Elétrica do Centro de Tecnologia da Universidade Federal do Rio Grande do Norte, em

cumprimento às exigências para obtenção do grau de Mestre em Engenharia Elétrica,

na área de concentração de Sistemas de Energia Elétrica.

Orientador: D.Sc. José Alberto Nicolau de Oliveira

NATAL - RN

MARÇO/2010

JÂNIO MENDONÇA JÚNIOR

Um sistema para simular o comportamento de bancos

trifásicos de reguladores de tensão usados em sistemas de

distribuição de energia elétrica.

Dissertação de mestrado submetida ao programa de Pós-Graduação em Engenharia

Elétrica do Centro de Tecnologia da Universidade Federal do Rio Grande do Norte, em

cumprimento às exigências para obtenção do grau de Mestre em Engenharia Elétrica,

na área de concentração de Sistemas de Energia Elétrica.

Aprovado por:

Prof. D.Sc. Marcos Antonio Dias de Almeida

Prof. D.-Ing. Manoel Firmino de Medeiros Jr.

Prof. D.Sc. José Alberto Nicolau de Oliveira

NATAL - RN

MARÇO/2010

Resumo

A crescente concorrência nos serviços de distribuição de energia elétrica de boa qualidade obriga as concessionárias a investirem em projetos que garantam a sua qualidade.

Manter níveis de tensão em padrões aceitáveis no ponto de entrega da energia elétrica

ao consumidor é um dos principais problemas enfrentados. A utilização de reguladores

de tensão torna-se uma forma viável para garantir a qualidade do serviço na entrega do

produto (energia elétrica), no entanto, a especificação de seus ajustes não se constitue

em tarefa simples, principalmente quando se tem grande variação de carregamentos,

inclusive, desequilíbrios.

Com base nos problemas expostos na utilização de reguladores de tensão, foi desenvolvido um sistema para simular o comportamento de bancos trifásicos de reguladores

de tensão usados em sistemas de distribuição de energia elétrica. Tal simulação será de

grande valor para visualização do comportamento de bancos trifásicos de reguladores de

tensão, antes de sua instalação na rede de distribuição, para definição de parâmetros de

regulação e restrições de regulação, para visualização de valores de ajuste de regulação

e variações de tensão.

Uma característica importante deste simulador é fato deste se comunicar com um

programa TOpReDE (Técnicas de otimização para redes de distribuição de energia elétrica), com intuito de comparar e validar resultados através da geração de gráficos, a

R

partir do Matlab.

R

Nesta implementação foram utilizados os blocos funcionais do Matlab/Simulink

R chamada DSP builder, ambiente no qual

em conjunto com a biblioteca da Altera,

serão feitas simulações e testes do sistema de regulação de tensão.

Palavras-Chave

Parâmetros de sensibilidade, Simulação, Sistemas de distribuição, Reguladores de

Tensão, DSP builder.

i

Sumário

1

Introdução

1

2

As ferramentas utilizadas

5

3

4

2.1

R . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

MATLAB

5

2.2

Simulink . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

5

2.3

Quartus II . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

6

2.4

R DSP builder . . . . . . . . . . . . . . . . . . . . . . . . . .

O Altera

7

2.4.1

Desenvolvimento . . . . . . . . . . . . . . . . . . . . . . . . .

8

2.4.2

Implementação e verificação . . . . . . . . . . . . . . . . . . .

8

2.4.3

Fluxo Automático (com simulink) e Fluxo Manual (sem simulink)

9

Reguladores de tensão

11

3.1

Introdução . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

11

3.2

Reguladores de tensão . . . . . . . . . . . . . . . . . . . . . . . . . .

13

3.2.1

Modelagens do Regulador de Tensão . . . . . . . . . . . . . .

15

3.2.2

Esquemas de ligação de reguladores em circuitos trifásicos . . .

16

3.2.3

Procedimentos atuais de controle dos reguladores de tensão . .

19

O algoritmo de simulação

4.1

4.2

21

Embasamento para o desenvolvimento do simulador do comportamento

de bancos trifásicos de reguladores de tensão . . . . . . . . . . . . . .

21

Desenvolvimento . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

23

4.2.1

Diagrama de blocos do simulador monofásico . . . . . . . . . .

23

4.2.2

Diagrama de blocos do simulador trifásico . . . . . . . . . . .

24

4.2.3

O simulador trifásico . . . . . . . . . . . . . . . . . . . . . . .

26

4.2.4

Memória ROM . . . . . . . . . . . . . . . . . . . . . . . . . .

28

ii

5

6

4.2.5

Temporização do modelo . . . . . . . . . . . . . . . . . . . . .

30

4.2.6

A UAT (unidade de ajuste de tensão) . . . . . . . . . . . . . . .

31

4.2.7

A UCT (Unidade de controle de tap) . . . . . . . . . . . . . . .

35

4.2.8

A UCAT (Unidade de cálculo das tensões) . . . . . . . . . . . .

36

Resultados e discussões

39

5.1

Comparação de resultados . . . . . . . . . . . . . . . . . . . . . . . .

39

5.2

Análise gráfica . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

41

5.2.1

Análise gráfica na fase C . . . . . . . . . . . . . . . . . . . . .

41

5.2.2

Análise gráfica na fase B . . . . . . . . . . . . . . . . . . . . .

43

5.2.3

Análise gráfica na fase A . . . . . . . . . . . . . . . . . . . . .

44

Conclusões

47

A A interface do simulador

50

B O formato Intel-HEX

53

B.1 O conteúdo de um registro HEX . . . . . . . . . . . . . . . . . . . . .

53

B.2 Exemplos de registro HEX . . . . . . . . . . . . . . . . . . . . . . . .

54

iii

Lista de Figuras

2.1

Fase de projeto com a biblioteca DSP builder . . . . . . . . . . . . . .

7

2.2

Blocos funcionais disponíveis na biblioteca DSP builder . . . . . . . .

9

2.3

Visão geral do fluxo de projeto utilizando DSP builder . . . . . . . . .

10

3.1

Diagrama unifilar de um trecho de um alimentador. . . . . . . . . . . .

12

3.2

Diagrama unifilar de uma rede de distribuição. . . . . . . . . . . . . . .

14

3.3

Modelos Básicos de autotransformador . . . . . . . . . . . . . . . . . .

14

3.4

Modelo elétrico do conjunto rede de distribuição - regulador . . . . . .

15

3.5

Modelo de referência para um regulador de tensão monofásico . . . . .

16

3.6

Ligação Estrela Aterrada de três reguladores monofásicos em uma rede

de distribuição trifásica. . . . . . . . . . . . . . . . . . . . . . . . . . .

3.7

Ligação Delta de três reguladores monofásicos em uma rede de distribuição trifásica. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

3.8

17

18

Ligação Delta Aberto de três reguladores monofásicos em uma rede de

distribuição trifásica. . . . . . . . . . . . . . . . . . . . . . . . . . . .

18

4.1

Alimentador utilizado em uma das simulações. . . . . . . . . . . . . .

22

4.2

Diagrama de blocos do simulador do regulador monofásico . . . . . . .

24

4.3

Diagrama de blocos do simulador do banco regulador trifásico . . . . .

24

4.4

Modelo do algoritmo de simulação para controle de tensão em um alimentador com regulador trifásico . . . . . . . . . . . . . . . . . . . . .

26

4.5

Memória Rom . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

29

4.6

Temporização do sistema. . . . . . . . . . . . . . . . . . . . . . . . . .

30

4.7

Máquina de estados (MdEcaPerfil) e bloco de configuração. . . . . . . .

31

4.8

Unidade de ajuste de tensão . . . . . . . . . . . . . . . . . . . . . . . .

32

4.9

Temporização na UAT. . . . . . . . . . . . . . . . . . . . . . . . . . .

33

4.10 Máquina de estados (MdE1_2) e bloco de configuração. . . . . . . . . .

34

iv

4.11 Unidade de controle de tap . . . . . . . . . . . . . . . . . . . . . . . .

35

4.12 Unidade de cálculo das tensões . . . . . . . . . . . . . . . . . . . . . .

37

5.1

Gráfico de comparação de tensão com TOpReDE na fase C. . . . . . . .

42

5.2

Gráfico tensão inicial X tensão final na fase C. . . . . . . . . . . . . . .

42

5.3

Gráfico de comparação de tensão com TOpReDE na fase B. . . . . . . .

43

5.4

Gráfico tensão inicial X tensão final na fase B. . . . . . . . . . . . . . .

44

5.5

Gráfico de comparação de tensão com TOpReDE na fase A. . . . . . . .

45

5.6

Gráfico tensão inicial X tensão final na fase A. . . . . . . . . . . . . . .

45

A.1 Simulador do comportamento de bancos trifásicos de reguladores de

tensão. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

51

A.2 Blocos do F1_subsistema. . . . . . . . . . . . . . . . . . . . . . . . .

52

v

Lista de Simbolos

TOpReDE Técnicas de otimização para redes de distribuição de energia elétrica

ASCII American Standard Code for Information Interchange

FPGA

Arranjo de portas programáveis no campo (Field Programable Gate Array)

DSP Processador Digital de Sinais (Digital Signal Processing)

VHDL

Linguagem de descrição de hardware (Hardware Description Language)

VHSIC

Very High Speed Integrated Circuit

FIR Finite Impulse Response

NCO

Numerically Controlled Oscilator

FFT Fast Fourier Transform

IFFT Inverse Fast Fourier Transform

A/D Analógico/Digital

D/A Digital/Analógico

LED Diodo emissor de luz (Light Emitting Diode)

FIFO Primeiro a entrar primeiro a sair (First in first out)

RAM Memória de acesso aleatório (Random Access Memory)

ROM

Memória apenas para leitura (Read Only Memory)

MdE

Máquina de estados

UAT

Unidade de ajuste de tensão

UCT

Unidade de controle de Tap

UCAT Unidade de Cálculo de Tensões

p.u.

por unidade

vi

Lista de Siglas

V1

Tensão complexa no ponto 1

V2

Tensão complexa no ponto 2

x, X

Impedância reativa

r, R

Impedância ativa

Vs

Tensão no secundário do transformador

Zs

Impedância no ramo série do regulador de tensão

Zd

Impedância no ramo em derivação

IL

Corrente de carga

Is

Corrente no ramo série do regulador de tensão

Id

Corrente no ramo em derivação do regulador de tensão

V ref

Vd

Tensão de referência

Tensão no enrolamento

n Número de espiras ou relação de espiras

I∗

S1 , S2

Conjugado da corrente

Potências aparentes complexas de entrada e saída no regulador de tensão

S Potência aparente complexa

I∗s

Corrente conjugada no ramo série do regulador de tensão

VA

Tensão na fase A

VB

Tensão na fase B

VC

Tensão na fase C

V AB

Tensão entre as fases A e B

V BC

Tensão entre as fases B e C

V CA

Tensão entre as fases C e A

Z Impedância equivalente

Vj , Vi

Tensões nos nós j e i

∆fc

Variação de carregamento

∆V i

Variação de tensão no nó i

∆V j

Variação de tensão no nó j

vii

V iest

Tensão de saída estimada no nó regulador i

V iant

Tensão de saída anterior a uma regulação de tensão no nó regulador i

V jant

Tensão de regulação anterior a uma variação de tensão no nó j

V jdes

Tensão de regulação desejada no nó j

V imed

∂Vj

∂Vi

V iat

Tensão medida na saída do nó regulador i

V jSim

Tensão de regulação calculada pelo simulador

V jT

Tensão de regulação calculada pelo TOpReDE

Coeficiente de tensão

Tensão de saída atingida no nó regulador i

viii

Capítulo 1

Introdução

A crescente concorrência nos serviços de distribuição de energia elétrica de boa qualidade, obriga as concessionárias a investirem em projetos que garantam a qualidade no

fornecimento do serviço. Qualidade em energia é portanto um fator de preocupação para

as concessionárias de energia elétrica. Tal preocupação iniciou-se em meados da década

de 80 segundo [11]. Como intervenientes principais nesta qualidade, destacam-se:

−→ a regulação de tensão no ponto de entrega de cada consumidor fora de padrões

estabelecidos. Alguns equipamentos são muito sensíveis a variações de tensão,

como aparelhos que contêm microprocessadores controlados e dispositivos eletrônicos que são sensíveis a qualquer tipo de perturbação;

−→ os cintilamentos (flickers) causados pelas repetitivas e rápidas mudanças de tensão

na rede de distribuição;

−→ o aumento da consciência sobre qualidade de energia pelo consumidor, que vem

se tornando mais interessado em questões como interrupções, variações de tensão,

interrupções freqüentes, e com isso vem cobrando das concessionárias de energia

elétrica melhorias na qualidade e na continuidade da energia entregue.

Para superar alguns destes problemas apresentados, reguladores de tensão e bancos

de capacitores são freqüentemente incorporados às redes de distribuição de energia elétrica [15], [16]. No entanto, a localização destes equipamentos, e em destaque a dos

reguladores de tensão, é fortemente dependente da topologia da rede e até há pouco

tempo, totalmente orientada por exaustivas análises de fluxos de carga, feitas nas unidades de planejamento das concessionárias de energia elétrica, onde são consideradas

1

regras cotidianas previsíveis (dayly) e mudanças sazonais de carregamentos [10]. A

proposta da regulação de tensão em redes de distribuição é manter níveis de tensão dentro de um faixa prescrita de valores, no ponto de entrega dos consumidores [8]. Alguns

avanços nessa área já são notados como a programação dinâmica e algoritmos de controle que implementam lógica fuzzy, utilizados para controle de bancos de capacitores e

transformadores com mudanças de taps [16].

A partir de análises feitas com algoritmos de fluxo de cargas, envolvendo alimentadores reais, constatou-se que uma variação na tensão de saída de um regulador se

reflete, linearmente, para todos os nós, localizados a jusante, para condições fixas de

carga e que, para uma condição fixa de tap do regulador, as tensões nos nós a jusante,

também variam linearmente, para excursões de carregamentos no intervalo usual da

curva de carga diária. Tais observações levaram à conclusão de que é possível controlar

a tensão de regulação de qualquer ponto desejado (local ou remoto) [10].

Outro aspecto bastante importante motivador para o desenvolvimento deste trabalho é a carência de simuladores do comportamento de bancos reguladores trifásicos de

tensão diante da grande necessidade de ensaios e simulações destes importantes equipamentos em redes de distribuição de energia elétrica. Algumas pesquisas foram feitas

e não foi encontrado nenhum sistema de simulação de comportamento dos reguladores

de tensão em redes de distribuição de energia elétrica.

Diante de tais fatos, desenvolveu-se um simulador para avaliar o comportamento de

bancos reguladores trifásico usados em redes de distribuição de energia elétrica. Tal

simulação é de grande valor para caracterizar parâmetros de regulação e restrições de

regulação, para visualizar valores de ajuste de regulação, variações de tensão e simulação de cargas. O simulador foi implementado com base nos coeficientes das funções

que definem a sensibilidade de tensão para cada nó presente em um alimentador.

Uma característica importante deste simulador é fato deste se comunicar com o programa TOpReDE (Técnicas de otimização para redes de distribuição de energia elétrica)1 , com intuito de comparar e validar os resultados através da geração de gráficos a

R

partir do Matlab.

1

Técnicas de Otimização para Redes de Distribuição de Energia Elétrica - desenvolvido pela base de

pesquisa OSEE (Otimização em Sistemas de Energia Elétrica), em 2004 e 2005, durante a execução de um

projeto de Pesquisa e Desenvolvimento proposto pela COSERN. A Base de pesquisa OSEE é composta

por professores e alunos dos cursos de Engenharia Elétrica e de Engenharia da Computação da UFRN.

2

R

Nesta implementação foram utilizados os blocos funcionais do Matlab/Simulink

R

em conjunto com a biblioteca DSP builder da Altera.

Foi também no ambiente

R

Matlab/Simulink

que foram feitas as simulações e os testes do sistema de simulação

R

de regulação de tensão implementado. O desenvolvimento do simulador no Matlab/Simulink,

utilizando-se da biblioteca DSP builder possibilita, que sejam feitas alterações bem

como uma posterior síntese e programação em um FPGA.

Para concretizar o trabalho proposto, o caminho delineado consistiu de cinco etapas

articuladas:

1. a primeira etapa abrangeu o levantamento bibliográfico sobre os objetos em questão, incluindo o estudo, a revisão e a classificação dos principais elementos subsidiadores das análises requeridas e propostas formuladas;

2. a segunda etapa, consistiu em aprender os blocos funcionais necessários ao deR DSP builder;

senvolvimento do simulador na biblioteca Altera

3. a terceira etapa, correspondeu à implementação do algoritmo de simulação no

R Simulink, bem como na análise, depuração e validação;

Matlab

4. a quarta etapa, foi dedicada à definição de uma proposição mais adequada;

5. a quinta etapa, foi reservada à fundamentação e ao aprofundamento teórico das

inferências ocorridas no transcorrer do trabalho e à redação final do trabalho de

dissertação.

Esta dissertação está estruturada em 6 capítulos, que guardam em si peculiaridades,

e entre si a coerência necessária às exigências da investigação, de modo a preservar sua

unidade.

O primeiro capítulo, corresponde à apresentação formal da proposta de dissertação,

sua fundamentação e seus direcionamentos.

R

O segundo capítulo, centra sua análise na biblioteca do Matlab/Simulink

desenR chamada DSP builder, onde são apresentados alguns conceitos

volvida pela Altera

básicos de estruturação dos blocos, quais as vantagens e desvantagens de utilizar tal

biblioteca, bem como a explicação das fases de um projeto utilizando a biblioteca DSP

builder e uma pequena apresentação de todas as ferramentas utilizadas para desenvolvimento do simulador.

3

O terceiro capítulo, faz uma breve apresentação sobre reguladores de tensão, demonstrando uma modelagem para reguladores de tensão bem como apresentando os

esquemas de ligação e os procedimentos de regulação de tensão atualmente utilizados.

O quarto capítulo, enfatiza o algoritmo desenvolvido para ajuste dos parâmetros

dos reguladores de tensão trifásico, utilizados em sistemas de distribuição. Ainda no

terceiro capítulo será analisada a implementação do simulador, apresentando todos os

blocos desenvolvidos e os detalhes de implementação de cada bloco.

O quinto capítulo, é dedicado a apresentar os resultados obtidos pelo simulador, a

análise de tais resultados e a comparação destes resultados com os resultados obtidos

pelo programa TOpReDE.

Nas conclusões (sexto capítulo) se estabelece um caminho de volta às proposições,

correlacionando-as com os objetivos alcançados. Apontam-se caminhos e perspectivas

geradas.

4

Capítulo 2

As ferramentas utilizadas

Este capítulo faz uma breve introdução às ferramentas utilizadas no desenvolvimento do

simulador de bancos trifásicos de reguladores de tensão, bem como analisa as vantagens

e algumas desvantagens de se utilizar tais ferramentas.

2.1

R

MATLAB

R é uma ferramenta de alto desempenho para programação técnica, foi desenMatlab

volvida pela Mathworks, empresa fundada em 1984, especializada em softwares para

R traz consigo a vantagem de que em uma mesma ferracomputação técnica. O Matlab

menta, tem-se a computação, visualização e a programação em um ambiente amigável,

onde os problemas e as soluções são expressos numa notação matemática familiar [2].

R oferece um ambiente para desenvolvimento de algoritmos em dois níveis;

O Matlab

um consiste da utilização de uma linguagem proprietária para descrição de algoritmos,

R o outro

semelhante à linguagem C, com arquivos .m no próprio ambiente do Matlab;

é um ambiente para desenvolvimento de sistemas, um ambiente gráfico, onde podem ser

instanciados blocos desenvolvidos em .m, chamado Simulink.

2.2

Simulink

Nos últimos anos, o Simulink tornou-se uma das ferramentas mais utilizadas em universidades e indústrias para se trabalhar com sistemas dinâmicos. O simulink é um pacote

de software que faz a modelagem, simulação e análise de sistemas dinâmicos. Ele su-

5

porta sistemas lineares, sistemas não lineares modelados em tempo contínuo, tempo

discreto ou híbrido. Os sistemas podem também ser multi-rate, isto é, possuem diferentes partes que podem ser amostradas ou atualizadas em diferentes taxas.

Com a ferramenta simulink, o usuário pode facilmente construir seu próprio modelo ou apenas modificar um modelo existente. O simulink trabalha com simulações

interativas, no entanto, qualquer alteração no programa pode ser notada em tempo de

simulação.

R e simulink permitem o desenvolvimento

O uso integrado das ferramentas Matlab

de algoritmos e sistemas de forma muito eficiente, permitindo desenvolver partes do

R

algoritmo em .m (extensão do Matlab),

simular estas partes individualmente e de-

pois integrá-las no sistema completo, simular o sistema e verificar o resultado final. O

sistema de desenvolvimento permite ainda, uma vez concluído o desenvolvimento e a

simulação do sistema, gerar programas em C ou código de descrição de hardware com

a implementação do sistema completo utilizando ferramentas de implementação.

2.3

Quartus II

Quartus II é um programa bastante utilizado no desenvolvimento de projetos que envolvem as linguagens VHDL e Verilog (Linguagem de descrição de hardware para projetos

eletrônicos). O programa fornece algumas ferramentas capazes de fazer análise e otimização de projetos que sejam elaborados em linguagem VHDL e Verilog para então

serem gravados em um dispositivo lógico programável. Os módulos abaixo são os blocos padrões utilizados pelo Quartus II para compilação de projetos [3].

- Analysis & Synthesis - executa a análise e síntese da lógica do projeto, com objetivo de otimizar a lógica do projeto e diminuir o tempo de compilação. Este

estágio também gera uma base de dados que será integrada ao projeto.

- Fitter - adapta a lógica do projeto em um dispositivo lógico programável.

- Assembler - converte os arquivos gerados nas fases Analysis & Synthesis e Fitter

para uma linguagem interpretada pelo dispositivo lógico programável.

- Timing Analyzer - analisa e válida a performance de tempo de toda lógica do

projeto.

6

O Quartus II utiliza os módulos de compilação com o objetivo de melhorar a lógica

do projeto e tornar o desenvolvimento do projeto mais rápido.

2.4

R DSP builder

O Altera

R Essa bibliO DSP builder é uma biblioteca para o simulink desenvolvida pela Altera.

R e de FPGA (Field

oteca integra em um único ambiente os fluxos de projeto do Matlab

Programable Gate Array), permitindo uma implementação simples e direta de algoritmos no ambiente simulink. A simulação do algoritmo dentro do ambiente simulink, a

conversão do algoritmo para código HDL e finalmente a compilação do projeto, carregálo em hardware e testar em hardware o sistema completo são atribuições da biblioteca

R A Figura 2.1 demonstra as fases do projeto desenvolvido pela

DSP builder da Altera.

biblioteca DSP builder [2].

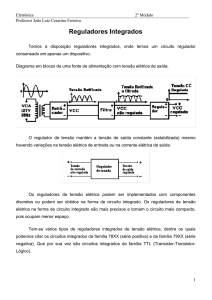

Figura 2.1: Fase de projeto com a biblioteca DSP builder

R

No desenvolvimento, os algoritmos são elaborados a partir do simulink do Matlab,

porém, as ferramentas utilizadas no desenvolvimento são apenas as que estão presentes

na biblioteca DSP builder, se forem utilizados blocos de outros Toolbox que não sejam

do DSP builder, estes blocos não serão implementados em VHDL. Na elaboração de

projetos utilizando a ferramenta DSP builder podem ser utilizados os Sinks e Sources

do Toolbox do simulink, desde que os blocos utilizados sejam apenas para gerar sinais de

entrada e para monitorar os resultados intermediários e finais do modelo de construção.

A fase de implementação, caracteriza-se pela capacidade que a ferramenta DSP builder

R

tem de comunicar o ambiente de desenvolvimento Matlab/simulink

com a ferramenta

de gravação em FPGA´s (field programmable gate arrays) e o Quartus II. A última fase

7

é a de verificação que se caracteriza pela análise dos sinais do hardware no próprio

simulink.

No projeto do simulador do comportamento de bancos trifásicos de reguladores de

tensão usados em sistemas de distribuição de energia elétrica, foi totalmente concluído

apenas na fase de desenvolvimento mostrada na Figura 2.1, uma vez que não havia a

proposição de implementação final do hardware em FPGA.

2.4.1

Desenvolvimento

A biblioteca DSP Builder contém alguns blocos funcionais, dentre os quais destacam-se

os que implementam funções aritméticas (chamada Arithmetic), funções de armazenamento (storage), funções para tratamento com números complexos (Complex Type) e,

de interface com dispositivos de entrada e saída (IO & Bus). A biblioteca DSP Builder,

permite também implementar máquinas de estado, sendo possível definir os sinais de

entrada, de saída e os estados internos bem como as transições de estados. Na Figura

2.2 é mostrada a relação de todos os blocos funcionais disponíveis no simulink após a

instalação da biblioteca DSP Builder.

Uma característica importante na biblioteca DSP builder, é que a mesma traz funções

complexas já implementadas, tais como, filtros FIR (Finite Impulse Response), NCOs

(Numerically Controlled Oscilator), FFT (Fast Fourier Transform), IFFT (Inverse Fast

Fourier Transform), entre outros. Nesta categoria de funções estão incluídas as funções

R e que podem ser incluídas no projeto de

complexas de DSP desenvolvidas pela Altera

forma imediata, bastando configurar os parâmetros da função e adicioná-la ao projeto

como um novo bloco [2]. A grande vantagem na utilização da biblioteca DSP Builder é

a de que além dela conter todas as atribuições antes citadas, ainda inclui blocos que perR tais

mitem fazer a interface direta com as placas de desenvolvimento DSP da Altera,

como utilizar pinos de entrada específicos, utilizar de forma direta os conversores A/D

e D/A disponíveis na placa, acessar os LEDs e chaves da placa, entre outros recursos.

2.4.2

Implementação e verificação

A biblioteca DSP builder fornece duas opções para síntese e compilação de projetos;

são as chamadas Fluxo Automático e Fluxo Manual. A Figura 2.3 demonstra uma visão

geral do fluxo de projeto utilizando a ferramenta DSP builder.

8

Figura 2.2: Blocos funcionais disponíveis na biblioteca DSP builder

2.4.3

Fluxo Automático (com simulink) e Fluxo Manual (sem simulink)

O fluxo automático permite fazer a síntese e compilação do projeto apenas utilizando

R

as ferramentas Matlab/simulink

com a adição da biblioteca DSP builder, a partir do

bloco SignalCompiler. No fluxo automático, o bloco SignalCompiler produz arquivos

VHDL, verilog HDL e Tcl; executa a síntese e compilação no Quartus II e opcionalmente carrega o projeto em um dispositivo lógico programável. O fluxo manual é utilizado quando o projeto necessita de configurações próprias na compilação [1].

Uma grande vantagem de utilizar a biblioteca DSP builder, é que o desenvolvimento

do sistema baseia-se no conceito de ambiente unificado onde o projeto de hardware e de

software usam a mesma infra-estrutura integrada, tendo por resultado uma melhoria do

desempenho global do sistema. A biblioteca DSP builder baseia-se no desenvolvimento

de projetos no paradigma de Co-design, cuja vantagem principal é o aumento do nível

de integração entre os sistemas, permitindo que sistemas inteiros sejam encapsulados

9

Figura 2.3: Visão geral do fluxo de projeto utilizando DSP builder

em um único chip.

Uma outra vantagem na utilização da biblioteca DSP builder é que não é necessário

ter conhecimento e prática com a linguagem VHDL, basta apenas saber manusear os

blocos do simulink de forma correta e então a biblioteca DSP Builder, a partir do bloco

SignalCompiler gera o código do projeto em linguagem VHDL.

Uma desvantagem na utilização da biblioteca DSP builder é que ela não implementa em blocos funcionais todas as ferramentas da linguagem VHDL, no entanto, se

for necessária a utilização de alguma ferramenta que a biblioteca DSP Builder não implemente, o DSP builder possui um bloco para código customizado a partir do qual

pode-se construir e adicionar a biblioteca qualquer bloco funcional.

10

Capítulo 3

Reguladores de tensão

Este capítulo apresenta alguns coneitos básicos de sistemas de distribuição de energia

elétrica, aborda também uma modelagem para reguladores de tensão, apresentando os

esquemas de ligação e os procedimentos de regulação de tensão atualmente utilizados.

3.1

Introdução

Um dos mais importantes objetivos de um sistema de qualidade, adotado pelas concessionárias de energia elétrica, é a manutenção dos níveis de tensão entregues aos seus

clientes. O suprimento das cargas presentes no sistema resulta em correntes através de

todos os componentes do sistema. Essas correntes causam quedas de tensão nos elementos presentes no sistema. A queda de tensão presente nos elementos constituintes de um

sistema é regida pela relação complexa V = I · Z . Uma das soluções mais diretas para

otimização da regulação de tensão, seria minimizar a impedância presente em todos os

elementos (as impedâncias dos condutores e as condições de carregamento influenciam

bastante na queda de tensão presente nos elementos constituintes do sistema), porém, tal

solução torna-se muito cara e bastante inviável. A Figura 3.1 demonstra um trecho de

um alimentador e tem o propósito de mostrar a origem das perdas existentes nos sitemas

de energia elétrcia.

11

Figura 3.1: Diagrama unifilar de um trecho de um alimentador.

A tensão V 2 na saída do transformador é maior que a tensão que chega à carga

0

V 2 . Isto ocorre, devido à impedância presente nos condutores aliada à corrente que flui

nestes condutores. A impedância é o resultado da resistência presente principalmente

nos condutores somada a reatância, grandeza presente em sistemas que trabalham com

corrente alternada. A demonstração da queda de tensão presente nos alimentadores, de

acordo com a Figura 3.1, é dada por:

0

V2 = V2 + Z ∗ I

(3.1)

O produto Z ∗ I representa a queda de tensão no condutor e quanto maior for a

corrente solicitada pela carga, maiores serão as perdas do sistema. A decomposição da

Equação 3.1 demonstra a relação da corrente com as perdas do sistema.

0

V2 = V2 − Z ∗ I

0

V 2 = V 2 − (r + jx) ∗ I

0

V 2 = V 2 − rI − jxI

(3.2)

0

V 2 I = V 2 I − rI2 − jxI2

Conclui-se que, um aumento de corrente se reflete significantemente em perdas para

o sistema, tendo em vista que o quadrado da corrente esta relacionado à potência ativa

(rI2 ) e potência reativa (jxI2 ) ao qual significam perdas para o sistema, como pode ser

visto na decomposição da Equação 3.1.

Uma forma de minizar as perdas em um sistema é a redução da corrente através

do sistema. Garantir que somente a porção de corrente em kVA requerida pelo cliente

12

seja entregue, ou seja, que flua pelo sistema apenas a potência solicitada, para isto é

necessária a instalação de bancos de capacitores em lugares estratégicos do sistema de

distribuição, os quais são responsáveis pela correção de fator de potência.

Um segundo método para ajuste de tensão nos sistemas de distribuição utilizado

pelas concessionárias de energia elétrica é a instalação de reguladores de tensão. O regulador de tensão nada mais é do que um autotransformador com um sistema de controle

apropriado capaz de fazer ajustes de tap de acordo com a necessidade do carregamento

do sistema [4]. Um dispositivo bem utilizado é o regulador de tensão monofásico que

pode ser empregado em sistemas monofásicos, ou pode ser conectado a outros reguladores monofásicos e formar um banco regulador para ser utilizado em sistemas trifásicos.

3.2

Reguladores de tensão

O regulador de tensão é um equipamento projetado para manter um nível de tensão prédeterminado no ponto de regulação, independentemente das variações das cargas, desde

que sua margem de regulação não seja ultrapassada. Construtivamente, é composto basicamente por um autotransformador associado a um comutador automático de derivação

sob carga e de um sistema de controle, que corrige os desvios momentâneos da tensão

de regulação, relativos ao valor especificado. Usualmente, os reguladores para redes

de distribuição são equipamentos monofásicos. Sua instalação é realizada, por meio da

formação de bancos trifásicos e, dependendo da configuração utilizada, pode-se obter

margens de regulação de até 15%1 (para cima ou para baixo).

A Figura 3.2 mostra o diagrama unifilar de uma rede de distribuição, onde o nó 1 é

a saída da subestação; entre os nós 3 e 4 está presente um regulador de tensão. Os nós

situados antes do regulador são considerados nós a montante e os nós situados depois

do regulador de tensão são considerados nós a jusante. Para efeito de simulações, o nó

situado imediatamente antes do regulador de tensão é considerado o nó regulador e para

este diagrama unifilar será considerado o nó 6 como sendo o nó regulado. A atuação

de um regulador será exemplificada através de um caso hipotético em que é necessário

elevar o nível de tensão no nó 6.

1

Os reguladores de tensão atualmente produzidos são autotransformadores reguladores com faixas

de regulação 10% acima a 10% abaixo, relativamente à tensão de linha, podendo ser ajustadas em 5%,

6,25%, 7,5%, 8,75% e 10%. A elevação ou a redução da tensão é feita em 32 degraus de aproximadamente

5/8% (16 para elevar e 16 para diminuir)

13

Monte

1

Nó

regulado

Nó

regulador

2

3

4

5

6

SVR

Figura 3.2: Diagrama unifilar de uma rede de distribuição.

O modelo básico do autotransformador usado em regulador é apresentado na Figura

3.3, em que suas bobinas são ligadas, uma em paralelo com a carga, chamada de bobina

ou enrolamento em derivação, e a outra, em série com a carga, chamada de bobina ou

enrolamento série. A bobina série poderá estar ligada no sentido de elevar a tensão no

secundário do regulador, Figura 3.3.a, ou no sentido de abaixar a tensão no secundário

do regulador, Figura 3.3.b. Um esquema genérico pode ser obtido acrescentando-se uma

chave reversível no enrolamento série como mostrado na Figura 3.3.c. Com a chave na

posição (x), o circuito funcionará como elevador e na posição (y), como abaixador de

tensão.

Figura 3.3: Modelos Básicos de autotransformador

Os reguladores trabalham igualmente bem em condições de altas ou de baixas tensões. O modelo mostrado na Figura 3.4 mostra a representação de um regulador aplicado em uma linha onde a tensão V 2 é corrigida para o valor V 3 . Os reguladores são

14

sensíveis à tensão e são usualmente controlados e ajustados automaticamente para manter constante a tensão de saída.

Figura 3.4: Modelo elétrico do conjunto rede de distribuição - regulador

3.2.1

Modelagens do Regulador de Tensão

Para modelagem de um regulador de tensão foi usado, inicialmente, o modelo visto na

Figura 3.5, apresentado em [9]. Por esse modelo, S1 e S1 são as potências aparentes

de entrada e saída do regulador, V s e V d são as tensões nos enrolamentos e Zs e Zd

representam as impedâncias do equipamento no enrolamento série e no enrolamento em

derivação, respectivamente. No circuito apresentado, para uma relação de transformação de n espiras, foi obtido o seguinte conjunto de equações:

V 2 = V 1 − V s − I s Zs

(3.3)

V d = V 1 − Id Zd − V ref

(3.4)

V s = V d /n

(3.5)

I = Is + Id

(3.6)

S1 = V 1 · I∗

(3.7)

S2 = V 2 · I∗s

(3.8)

Das observações feitas [9] em sua modelagem matemática do regulador, três pontos

devem ser ressaltados:

−→ de acordo com as equações acima, a tensão V s que está sendo somada à tensão

de entrada do regulador, estará praticamente em fase com a tensão de entrada V 1 ,

15

Figura 3.5: Modelo de referência para um regulador de tensão monofásico

no caso em que V ref é a tensão de neutro e, poderá estar defasada em relação à

tensão de entrada, no caso em que V ref é uma tensão de outra fase. Isso significa

que, além de ocorrer um incremento no módulo da tensão de entrada, o ângulo da

tensão de saída poderá não ser o mesmo que o da tensão de entrada.

−→ no caso em que o ramo em derivação de um regulador adota como referência uma

outra fase (em vez de um ponto neutro), a potência na entrada do regulador não

será necessariamente igual à potência na sua saída, ou seja, a presença do ramo

em derivação permite que a fase a ele ligada forneça potência ativa ao regulador.

−→ depois que a corrente que passa pelo regulador ultrapassa a sua corrente nominal,

a sua capacidade de regulação passa a decrescer. Porém, essa perda de capacidade

de regulação não é diretamente decorrente das características elétricas internas

(queda de tensão, perdas, relação de espiras) do regulador, mas de um ajuste que

é feito manualmente no regulador onde o tap máximo é limitado, para que os

limites de operação do equipamento não sejam ultrapassados.

3.2.2

Esquemas de ligação de reguladores em circuitos trifásicos

Os três esquemas usuais de construção de bancos trifásicos de reguladores são o Estrela

Aterrada 2 , mostrado na Figura 3.6, que usa três reguladores monofásicos, o Delta,

2

Três reguladores não podem ser ligados diretamente em Estrela Isolada em circuito trifásico a três

fios pois pode haver deslocamento do neutro.

16

mostrado na Figura 3.7, que usa também três reguladores monofásicos e o Delta Aberto,

mostrado na Figura 3.8, que usa apenas dois reguladores monofásicos. Notar que cada

fase está ligada a uma bobina em derivação, na saída do regulador, sobre a qual se aplica

uma tensão de fase (ligação em Estrela) ou de linha (ligações Delta e Delta Aberto) e

que as impedâncias, série e paralela, são representadas por uma impedância equivalente

Z, no ramo série.

Figura 3.6: Ligação Estrela Aterrada de três reguladores monofásicos em uma rede de

distribuição trifásica.

17

Figura 3.7: Ligação Delta de três reguladores monofásicos em uma rede de distribuição

trifásica.

Figura 3.8: Ligação Delta Aberto de três reguladores monofásicos em uma rede de

distribuição trifásica.

No esquema em Estrela Aterrada, as tensões de fase V A2 , V B2 e V C2 são aplicadas

nas bobinas em derivação que induzem tensões nV A2 , nV B2 e nV C2 nas bobinas série

correspondentes. Estas tensões serão somadas às tensões de entrada V A2 , V B2 e V C2 .

Nesse tipo de configuração as tensões reguladas se mantêm em fase com as tensões de

18

entrada, mas para uma mudança máxima de tap, a máxima regulação que se pode obter

é de 10% (para cima ou para baixo).

Numa ligação em Delta (Figura 3.7), pode-se observar que as tensões aplicadas nas

bobinas em derivação dos reguladores são tensões de linha e não de fase. Neste caso, as

parcelas das tensões de linha nV AB2 , nV BC2 e nV CA2 serão somadas, respectivamente,

as tensões de entrada dos reguladores V A1 , V B1 e V C1 . Como as tensões de linha são

maiores do que as tensões de fase, consegue-se uma faixa de regulação de até 15%

(para cima ou para baixo), 50% maior do que a faixa de regulação que se obtem com o

esquema de ligação em Estrela Aterrada.

No esquema em Delta Aberto (Figura 3.8), são utilizados apenas dois reguladores

monofásicos. Nesta configuração, as três tensões de linha aumentam ou diminuem proporcionalmente. Com esse esquema de ligação, consegue-se uma faixa de regulação de

até 10%, igual, portanto, ao esquema em Estrela Aterrada, mas, com um regulador a

menos.

3.2.3

Procedimentos atuais de controle dos reguladores de tensão

Os controles atuais dos reguladores de tensão incorporam lógica digital e tecnologia microprocessada, normalmente de 8 bits, associadas a um conversor analógico/digital. A

lógica de operação dessas unidades de controle é disparada sempre que a tensão medida

na saída do regulador apresentar valores fora de uma faixa pré-estabelecida de tensões

de ajuste. Por exemplo, entre 119 V e 121 V para uma tensão de base 120 V e uma

largura de faixa de 2 V [5]. A operação da unidade de controle pode ser descrita de

acordo com os seguintes procedimentos:

1. quando a tensão medida move-se para um nível fora da faixa, a amostra do sinal

é convertida em um formato digital e fornecida ao microprocessador;

2. o microprocessador, reconhecendo a condição de tensão como fora da faixa, dispara um circuito de retardo de tempo3 , sendo este tempo de retardo igual ou superior a 30 s;

3

O tempo de retardo é o período de tempo (em segundos) que o controle espera, desde o primeiro

instante quando a tensão sai da faixa ao instante em que o relé, responsável por elevar ou abaixar a

tensão, atua. Se uma resposta rápida é requerida, um valor pequeno de ajuste deve ser feito. Se há vários

reguladores na mesma linha para serem coordenados (em cascata), diferentes ajustes de tempo de retardo

serão requeridos para permitir a operação adequada na seqüência desejada. Partindo da subestação, cada

19

3. enquanto aguarda o término do tempo de retardo, a tensão é continuamente medida. Se a tensão momentaneamente mover-se para a faixa, a operação de ajuste

será interrompida. Persistindo a condição fora de faixa, ao término do tempo de

retardo, uma mudança de tap é iniciada;

4. ao reconhecer que a mudança de posição de tap foi completada, é feita uma pausa

de 2 s. Após essa pausa, se a tensão medida ainda estiver fora da faixa, outra

mudança de tap é iniciada. Este procedimento se repete até que a tensão medida

volte para a faixa, quando então a operação de ajuste é concluída.

Em geral, como garantia de funcionamento adequado do controle, é incluído um

sistema de vigilância, chamado de cão de guarda watchdog, executado periodicamente,

de tal forma que se houver qualquer anormalidade no funcionamento do sistema, a execução do software será reinicializada.

regulador deveria ter um tempo de retardo maior que o regulador que o precede. Recomenda-se um

mínimo de 15 segundos de diferença entre reguladores localizados na mesma fase do mesmo alimentador.

O retardo permite que reguladores a montante atuem antes dos reguladores a jusante.

20

Capítulo 4

O algoritmo de simulação

Este capítulo tem por objetivo detalhar o algoritmo desenvolvido para ajuste das tensões

de saída dos bancos trifásicos reguladores de tensão utilizados em sistemas de distribuição de energia elétrica, bem como demonstrar a teoria na qual esse simulador foi

baseado e detalhar todos os blocos constituintes do simulador.

4.1

Embasamento para o desenvolvimento do simulador do comportamento de bancos trifásicos de reguladores de tensão

Baseado em estudos de fluxo de carga em sistemas de distribuição de energia elétrica,

realizados em alimentadores reais [13] [14] [10], concluiu-se que a tensão de todos os

nós a jusante do regulador variam linearmente com a sua tensão de saída, considerando

cargas constantes, para os nós 7, 11 e 21 do alimentador mostrado na Figura 4.1 usado

em uma das simulações da referência [12]. Similarmente, para uma condição fixa de tap

do regulador, as tensões nos nós a jusante, também variam linearmente, para excursões

de carregamentos no intervalo usual da curva de carga diária.

Esses dois comportamentos lineares da variação de tensão, para todo nó j situado a

jusante de um regulador, fixado em um nó i, são dados pelas duas equações abaixo.

∆Vj =

∂Vj

∂Vi

∆Vi |∆fc = 0

21

(4.1)

Figura 4.1: Alimentador utilizado em uma das simulações.

∆Vi =

∂Vi

∂Vj

∆Vj |∆fc = 0

(4.2)

Donde pode-se depreender que a variação total da tensão no ponto de regulação será

dada por [5]:

∂Vj

∆Vi +

∂Vj

∆fc j

(4.3)

∂Vi

∂fc j

Tais observações permitiram chegar à conclusão de que é possível controlar a tensão

Vj =

de regulação, em qualquer ponto desejado, a partir dos coeficientes das funções que

definem essas linearizações, para cada nó, situado a jusante do regulador. Assim, a

tensão que se estabelecerá em um nó regulado j, em decorrência da medição de uma

variação de tensão no nó regulador i, será dada pela seguinte Equação:

∂Vj

(Vimed − Viant )

(4.4)

∂Vi

Semelhantemente, uma variação de carga ∆fc implicará em tensões nos nós, reguVjest = Vjant +

lador e regulado, dadas respectivamente por:

22

Vjest = Vjant +

Vimed = Viant +

∂Vj

∂fc

∂Vi

∆fc

(4.5)

∆fc

∂fc

Fazendo-se a relação entre 4.5 e 4.6, como mostrado abaixo,

Vjest = Vjant +

∂Vj

∂fc

∂Vi

∂fc

(4.6)

(Vimed − Viant )

(4.7)

(Vimed − Viant )

(4.8)

Obtém-se:

Vjest = Vjant +

∂Vj

∂Vi

Onde:

Vjest - Tensão de regulação estimada no nó j.

Vimed - Tensão medida na saída do regulador.

Vjant - Tensão de regulação no nó j anterior à variação..

Viant - Tensão na saída do regulador anterior à variação..

fc - fator de carregamento.

Monitorando-se a tensão de saída do regulador, será possível então obter o valor da

tensão Vimed e estimar a tensão no ponto de regulação Vjest , de acordo com 4.8 [5].

Com o conhecimento dos parâmetros de sensibilidade

∂Vj

∂Vi

e

∂Vj

∂fc

, é possível também

fazer uma estimativa da mudança que irá ocorrer no perfil de tensão de um alimentador,

em decorrência de uma variação imposta por mudança dos taps de um banco regulador

de tensão bem como por uma variação imposta por mudanças no carregamento.

4.2

4.2.1

Desenvolvimento

Diagrama de blocos do simulador monofásico

R

Em um primeiro momento, foi desenvolvido um sistema em Matlab/Simulink

com

a adição da biblioteca DSP Builder para fins de simulação do comportamento de reguladores de tensão em sistemas monofásicos [7], tal sistema é capaz de controlar a

tensão de regulação, em qualquer ponto desejado (local ou remoto), a partir dos coeficientes das funções que definem cada nó. A Figura 4.2 ilustra o diagrama de blocos do

algoritmo de simulação de um regulador de tensão monofásico.

23

Figura 4.2: Diagrama de blocos do simulador do regulador monofásico

A partir da implementação do simulador monofásico, foi desenvolvido o simulador de bancos trifásicos de reguladores. Os blocos do diagrama da Figura 4.2 serão

explicados com mais detalhes na Subseção 4.2.2.

4.2.2

Diagrama de blocos do simulador trifásico

A implementação do simulador do banco regulador trifásico mostrado na Figura 4.3,

incorpora todos os blocos desenvolvidos no simulador monofásico e adiciona outros

blocos. O simulador de bancos reguladores trifásicos foi desenvolvido utilizando-se as

R

ferramentas Matlab/Simulink

e a biblioteca DSP Builder, no entanto a geração do

código em linguagem VHDL foi feita a partir do Quartus II.

ROMp1

ROMc1

InLoad

Reset

Plot

Medidor de

tensão

UAT (Unidade

ROMp2

V1

ROMc2

de Ajuste de

Tensão)

UAT (Unidade

ROMp3

UAT (Unidade

V2

ROMc3

V3

de Ajuste de

Tensão)

MdE

V1

V2

V3

ADC

UCAT

(Unidade de

cálculo das

tensões)

Sampler

UCT

(Unidade

de

controle

de Tap)

de Ajuste de

Tensão)

V1

V2

V3

Figura 4.3: Diagrama de blocos do simulador do banco regulador trifásico

No diagrama de blocos apresentado na Figura 4.3, as unidades ROMp1, ROMp2,

ROMp3 e ROMc1, ROMc2, ROMc3 são memórias que permitem o pré-armazenamento

24

de dados. Esses dados são os perfis de tensão e os coeficientes de tensão de todos os nós

presentes no alimentador informados pelo programa TOpReDE. No modelo proposto,

através da unidade Sampler seria possível simular o comportamento do circuito a partir

dos sinais efetivamente medidos, informados pelo ADC ou por um valor de posicionamento atual do tap, informado pela UCT (unidade de controle de tap). No entanto, a

unidade Sampler não será implementada, porém, ela é demonstrada no diagrama como

forma de continuação deste trabalho.

Toda temporização do modelo é feita pela Máquina de Estado (bloco MdE), sendo

possível controlar, por meio do sinal InLoad se em uma simulação deve-se ou não carregar um novo perfil de tensão e novos coeficientes de tensão. As condições inicias e

as restrições de regulação, diferentemente do simulador do regulador monofásico, são

incorporadas ao bloco UCAT do simulador de bancos reguladores trifásicos de tensão.

As principais unidades do modelo são a UAT (Unidade de ajuste de tensão), UCT

(Unidade de controle de Tap) e UCAT (Unidade de Cálculo de Tensões). Cabe a UAT

fazer todas as análises necessárias que lhe permitam estimar as tensões de fase na saída

do nó regulador e que irá garantir a tensão desejada no nó regulado. A UCT se responsabiliza pelas mudanças de tap e pela atualização da tensão de saída do regulador. A

UCAT é responsável pelo cálculo dos perfis de tensão do alimentador após variações de

tensões na saída do regulador. A implementação de uma fase (fase 1) bem como os valores de tensão inicial, tensão estimada, posição do tap e tensões de saída do regulador,

referentes as três fases, são demonstrados na Figura 4.4.

25

Figura 4.4: Modelo do algoritmo de simulação para controle de tensão em um alimentador com regulador trifásico

Ainda observando a Figura 4.4, é notada a presença de um bloco chamado "HDL

SubSystem In Tap F1". Nesse bloco, estão situadas as unidades UAT (Unidade de ajuste

de tensão), UCT (unidade de controle de tap) e UCAT (Unidade de Cálculo de Tensões)

que serão melhor explicadas nas seções seguintes. A implementação das três fases do

simulador de bancos reguladores trifásicos é mostrada no Anexo A.

4.2.3

O simulador trifásico

O simulador desenvolvido é de interface amigável, ou seja, de fácil manuseio. Os dados

de entrada no simulador serão as quantidades de nós do alimentador a serem analisados

(vnNohsx), o nó regulador (vNohix), o nó regulado (vNohjx) e a tensão desejada no

nó regulado (vVjDejx) em p.u. O dados de saída das três fases serão a tensão atual no

nó regulador (DspVi_Fx), tensão estimada no nó regulador (DspViEspFx), variação de

26

tap (DspPosTap_Fx), tensão atingida no nó regulador (DspViAt_Fx) e o valor da diferença entre a tensão estimada e a tensão atingida (Dsp_Dif_ViAt-Viesp_x). Os dados

de entrada como os dados de saída podem ser visualizados na Figura 4.4.

Na Figura 4.4 é mostrado o modelo em uma simulação de um alimentador de vinte

e três nós com um banco regulador trifásico situado no nó 7, regulando o nó 16 em

aproximadamente 0.90 p.u na fase 1, 0.92 p.u. na fase 2 e 0.94 p.u na fase 3.

Armazenadas as informações inerentes ao alimentador (perfil de tensão, quantidade

de nós à serem analisados, nó regulador, nó regulado e faixas de tensões no nó regulado)

o algoritmo de simulação executa os seguintes passos:

1. Calcula as tensões inicias no nó regulador e estima as tensões de saída do nó

regulador para obter uma condição prévia as variações.

2. Verifica quantos passos, relativamente à posição atual de tap deve ser elevada ou

baixada para este objetivo.

3. Envia o sinal para mudança de tap se nenhuma restrição for violada; senão reavalia as mudanças de tap de acordo com a etapa precedente.

4. Calcula o novo perfil de tensão do alimentador, se alguma variação de tensão tiver

ocorrido na saída dos reguladores e, o representa graficamente.

Na situação apresentada na Figura 4.4, a tensão final estimada na saída do regulador

é de 0.971445 p.u na fase 1, 0.987273 p.u. na fase 2 e 1.003541 p.u. na fase 3, a tensão

inicial na saída do regulador era de 0.994257 p.u. para fase 1, 0.997905 p.u. para fase 2

e 1 p.u. na fase 3, deste modo, esses valores de tensões iniciais representam o caso base.

O tap está na posição -3 na fase 1 e, para este posicionamento do tap, a tensão de

saída do regulador é de 0.975507 p.u., na fase 2, o tap está na posição -1 e a tensão de

saída do regulador é de 0.991655 p.u. e, na fase 3 o tap está na posição 0 (não houve

mudança de tap para esta fase) e a tensão de saída do regulador é de 1 p.u (a mesma

tensão inicial, pois não foi necessária uma mudança de tap).

Após ocorrerem as devidas mudanças de tap, o simulador informa a diferença de

tensão entre a tensão estimada e a tensão atingida. A diferença de tensão foi de 0.004062

p.u. na fase 1, 0.004381 p.u. na fase 2 e de 0.003541 p.u. na fase 3.

Os blocos funcionais do simulador trifásico desenvolvidos foram: MdE (máquinas

de estados), UAT (unidade de ajuste de tensão), UCT (unidade de controle de Tap) e

27

UCAT (Unidade de Cálculo das tensões). Um bloco ao qual foi previamente desenvolvido é a unidade ADC (Conversão Analógica Digital), porém, sua atuação não será

verificada devido a proposta da implementação do simulador não abranger a atuação em

dispositivos lógicos programáveis.

As subseções seguintes explicarão detalhadamente como funciona cada bloco desenvolvido bem como a utilização das memórias de dados pré-armazenados (ROMp1,

ROMp2, ROMp3, ROMc1, ROMc2 and ROMc3) entre outras implementações.

4.2.4

Memória ROM

As memórias utilizadas no desenvolvimento do simulador são memórias do tipo ROM

que trabalham com dados pré carregados (são chamadas de ROM EAB pela biblioteca

DSP Builder). Um detalhe na utilização destas memórias é que elas leêm apenas dados

no formato Intel HEX (.hex). Maiores detalhes sobre o formato Intel HEX são explicados no Apêndice B.

A utilização das memórias ROM são de grande importância para a robustez do simulador desenvolvido. A principal característica na utilização destas memórias é o fato

delas lerem arquivos texto escritos no formato Intel HEX. Diante disto, foi possível validar os resultados do simulador em comparação com os dados gerados pelo programa

TOpReDE. Dentro do programa TOpReDE foi incluído um código escrito em linguagem

C++ para gerar arquivos texto no formato Intel HEX, então, alguns dados de entrada necessários ao simulador, tais como, os perfis de tensão e os coeficientes de tensão foram

gerados e codificados no formato intel HEX e fornecidos ao simulador para então serem

lidos pelas memórias ROM.

No caso do simulador ser implementado em um dispositivo lógico programável, a

utilização das memórias ROM seria de grande importância, no sentido de que se houvesse a necessidade de uma recarga dos dados das memórias, seria suficiente apenas

uma troca de cartão de memória, não sendo necessária uma mudança no simulador e

uma nova gravação do simulador no dispositivo lógico programável.

A figura 4.5 demonstra duas memórias ROM utilizadas na implementação do simulador, uma para armazenar os perfis de tensão (ROM EAB) e a outra para armazenar os

coeficientes de tensão (ROM EAB1) referentes à fase A. Na figura 4.5 também pode ser

percebido um bloco dos parâmetros das memórias (Block Parameters: ROM EAB).

C As palavras contidas no arquivo .hex do simulador, são palavras de 32 bits geradas

28

Figura 4.5: Memória Rom

pelo programa TOpReDE, e um detalhe a ser exposto é que o formato intel HEX só

reconhece números inteiros, sinalizados ou não.

Os perfis de tensão e os coeficientes de tensão (dados codificados no formato intel

HEX) são, na maioria das vezes, números fracionários, então, para que esses números

sejam codificados para o formato requerido, é necessário transformá-los em números

inteiros. O artifício utilizado para transformar os números fracionários em números

inteiros, é a multiplicação dos perfis e coeficientes de tensão por um número grande

de forma que não perca tanto a precisão das casas decimais do número. Após serem

transformados em números inteiros, eles finalmente são codificados para o formato intel HEX (tanto a codificação quanto a transformação foram realizadas pelo programa

TOpReDE) e passados ao simulador, então, o simulador lê esses dados das memórias

ROM e dividi-os pelo mesmo coeficiente ao qual foram multiplicados para se obter o

número fracionário. Na divisão feita pelo simulador, os números fracionários perdem

precisão, muitas das vezes, a partir da terceira casa decimal depois da vírgula, comprometendo muito a precisão dos resultados finais do simulador. Diante deste problema, a

solução encontrada foi fazer a normalização dos perfis de tensão e dos coeficientes de

tensão, de modo que, como as palavras do arquivo .hex armazenavam dados de 32 bits,

o maior valor a ser representado tanto para os perfis, quanto para os coeficientes de ten-

29

são é de 231 , pois o bit mais significativo é o bit de sinalização. A Tabela 4.1 demonstra

as formas de representação de alguns valores dos perfis e coeficientes de tensão.

Tabela 4.1: Representação de valores

Perfil de tensão (p.u.) Perfil de tensão (normalizado) Perfil de tensão (.hex)

1

2147483648

:0400xxxx80000000xx

0.9998

2147060736

:0400xxxx7FF98C00xx

0.9561

2053328896

:0400xxxx7A635000xx

0.9140

1962930560

:0400xxxx74FFF180xx

O objetivo da normalização foi fazer com que o simulador entendesse os números

normalizados como números fracionários, e isso foi possível devido à propriedade das

memórias ROM de interpretar os dados do arquivo .hex como números fracionários

sinalizados. Esta propriedade pode ser vista na Figura 4.5, caracterizada por Data Bus

Type: Signed Fractional.

4.2.5

Temporização do modelo

Toda temporização do circuito simulador acompanha o diagrama de estado mostrado na

Figura 4.6, gerado pela MdE (máquina de estado) MdEcaPerfil. Na Figura 4.6, S1 representa o estado inicial e os símbolos IL, Str e P l são, respectivamente, abreviações

dos sinais InLoad, Start e Plot.

Figura 4.6: Temporização do sistema.

Em seqüência têm-se: a inicialização da UAT em S1; a inicialização da UCT em

S2; a transferência de parâmetros de tensão da rede para a UAT e o cálculo das tensões

estimadas em S3; os cálculos e as definições de mudanças dos taps são implementadas

durante os estados S4, S5, S6 e S7 e; em S8 e S9 são concluídos os ajustes de tensões

e calculado o novo perfil de tensão do alimentador.

30

Figura 4.7: Máquina de estados (MdEcaPerfil) e bloco de configuração.

Toda a configuração da máquina de estados MdEcaPerfil é feito a partir do bloco

DSP builder - Sate Machine Builder como pode ser visto na Figura 4.7. Neste bloco

são informadas as entradas (Inputs), os estados da máquina (States) e as condições dos

estados (Conditional Statements). A Figura 4.7 demonstra as entradas e os estados na

máquina de estados MdEcaPerfil e no bloco de configuração é demonstrado as condições dos estados de acordo com o grafo da Figura 4.6.

4.2.6

A UAT (unidade de ajuste de tensão)

Implementada como um subsistema, a UAT, mostrada na Figura 4.8, é basicamente composta por duas memórias RAM (random access memory), duas memórias FIFO (first in

first out), um contador, alguns operadores lógicos e aritméticos, uma máquina de estado

e um multiplexador, sendo responsável pela análise das condições atuais do alimentador e pela estimação das tensões de saída do banco regulador frente às imposições de

tensões e de cargas em cada nova simulação.

Após ser inicializada os valores dos perfis de tensão e os valores dos coeficientes

de tensão, são passados das memórias (ROMp1, ROMp2, ROMp3, ROMc1, ROMc2

and ROMc3), externas ao bloco UAT, para memórias RAM internas ao bloco UAT. O

contador é iniciado com o número de nós da rede e são buscadas as informações de

número de nós, do nó regulador, do nó regulado e dos valores de tensões de regulação

desejados no nó regulado.

31

Figura 4.8: Unidade de ajuste de tensão

Como dito anteriormente, a UAT é responsável por estimar as tensões de fase na

saída do regulador. Este cálculo de estimação é baseado na Equação 4.8 [5], de onde

chegou-se a Equação 4.9:

Viest = Viant +

∂Vi

∂Vj

(Vjdes − Vjant )

(4.9)

onde:

Viest - Tensão de saída estimada no nó regulador i.

Viant - Tensão de saída anterior a uma regulação de tensão no nó regulador i.

∂Vi

∂Vj

- Inverso do coeficiente de tensão.

Vjant - Tensão de regulação anterior a uma variação de tensão no nó j.

Vjdes - Tensão de regulação desejada no nó j.

A UAT foi desenvolvida com base na Equação 4.9. Analisando a Figura 4.8 percebese cada bloco responsável pelo cálculo do Viest . No centro da Figura tem-se três blocos

denominados DeltaVj, DeltaVi e vViEsp. De acordo com a Equação 4.9, eles calculam

32

respectivamente a diferença entre a tensão de regulação desejada no nó j e tensão de

regulação anterior a uma variação de tensão no nó j (DeltaVj); o produto entre o inverso

do coeficiente de tensão e a diferença entre as tensões (Vjdes e Vjant ) (DeltaVi) e por

último a soma entre DeltaVj e DeltaVi (vViEsp).

Um detalhe a ser notado na Equação 4.9, é que o elemento

∂Vi

∂Vj

é o inverso do coe-

ficiente de tensão. Então, os coeficientes de tensão são, na maioria das vezes, números

fracionários. Para fazer o cálculo do inverso dos coeficientes de tensão utilizou-se o

bloco Divider. No entanto, o Divider não trabalha com números fracionários o que

obrigou a utilização de um artifício fosse possível trabalhar com os coeficientes de tensão. O artifício utilizado foi; a divisão dos coeficientes de tensão por uma constante

(um número grande 218 ), com o objetivo de não perder a precisão das casas decimais,

e depois multiplicar o resultado pelo inverso da constante. Os blocos da biblioteca DSP

builder utilizados para realizarem esta operação foram o Divider e o Binary Point Casting que podem ser vistos no canto superior direito da Figura 4.8. O artifício utilizado é

demonstrado na Equação 4.10.

218 1

X

218

=

1

X

(4.10)

Temporização interna na UAT

Internamente, toda operação da UAT é controlada pela máquina de estado MdE1_2, cujo

diagrama de estado é mostrado na Figura 4.9, com estado inicial S1_1 e seqüência de

operação disparada com o reconhecimento de um nível 0 no sinal sCont, emitido pela

máquina de estados MdEcaPerfil.

Figura 4.9: Temporização na UAT.

Durante S1_1 são armazenados, nas memórias FIFO1_1 e FIFO1_2, os perfis de

tensões e os coeficientes de tensão e, durante S2_1 a S8_1 são controladas as operações

executadas pela UAT no cálculo estimado das tensões de saída dos reguladores, a serem

disponibilizadas para a UCT.

33

Figura 4.10: Máquina de estados (MdE1_2) e bloco de configuração.

De forma idêntica a configuração da máquina de estados MdEcaPerfil, a configuração da máquina de estados MdE1_2 também foi feita a partir do bloco DSP builder

- State Machine Builder como pode ser visto na Figura 4.10. Essa figura mostra as

entradas e os estados na máquina de estados MdE1_2 e no bloco de configuração são

mostradas as condições dos estados, que foram embasados na seqüência de operação da

máquina de estados MdE1_2.

Um bloco bastante importante da biblioteca DSP builder no desenvolvimento do simulador é o Delay, ele serve para sincronizar os tempos de amostragem do simulador,

por exemplo, para serem feitas as leituras corretas dos perfis de tensão e coeficientes de

tensão dos seus respectivos nós foi necessário incluir o bloco Delay na UAT que pode

ser visto na parte superior da Figura 4.8 abaixo do bloco Counter. O bloco Counter é

responsável por ler a quantidade de nós do alimentador que foram informadas no simulador, dar estímulo às memórias ROM para que estas passem os valores dos perfis de

tensão e coeficientes de tensão paras as memórias RAM internas ao bloco UAT e o bloco

Counter também determinem quais posições das memórias RAM os dados passados das

memórias ROM serão armazenados. No entanto, o bloco Counter e as memórias RAM

estão localizadas dentro do subsistema UAT e as memórias ROM estão na parte externa

do simulador, então, um sinal enviado pelo bloco Counter as memórias ROM percorre

muito mais blocos do que um sinal enviado do bloco Counter as memórias RAM. Deste

modo, para sincronizar estes sinais, foi utilizado o bloco Delay.

34

4.2.7

A UCT (Unidade de controle de tap)

A UCT, responsável pelas mudanças de taps, é também implementada como um subsistema, mostrado na Figura 4.11, e composto basicamente por uma memória FIFO, um

contador, alguns multiplexadores e alguns operadores lógicos e aritméticos.

Figura 4.11: Unidade de controle de tap

Após ser inicializado por S1, emitido pela MdE MdEcaPerfil, a UCT fica em estado

de espera, aguardando as informações de tensões iniciais e estimadas, geradas pela UAT,

quando então, passa a monitorar as medições de tensões, recebidas através do bloco

ADC ou auto-realimentadas. Com base nos valores iniciais, estimados e medidos, o

bloco UCT calcula e executa as mudanças necessárias de taps. O funcionamento da

UCT pode ser melhor explicado se for analisada a expressão 4.11.

|(Viest − Vimed )160| ≥ 1

(4.11)

Vimed - Tensão medida na saída do nó regulador i.

A Equação 4.11 determina se haverá ou não variação de tap, de modo que se a

condição for atendida haverá variação de tap. Um detalhe importante nesta equação é o

número "1", pois este número determina a restrição na variação de tap. Se a diferença

35

entre Viest e o Vimed for inferior a 1 p.u. não haverá mudança no posicionamento do

tap do regulador.

Uma outra implementação importante na UCT, é determinar se a variação de tap

vai ser de elevação ou abaixamento, então utilizou-se o bloco ExtractBit que pode ser

notado quase ao centro da Figura 4.11. Se o bit mais significativo do resultado de

(Viest − Vimed ) for 1 (resultado positivo), haverá uma elevação no posicionamento do

tap e se o bit mais significativo for 0, haverá um abaixamento no posicionamento do

tap.

Na parte superior direita da Figura 4.11 tem-se três blocos que são: PosTap[4:0],

iTap e pTap. O bloco PosTap[4:0] informa a posição atual do tap, o bloco iTap informa

se haverá elevação (1) ou abaixamento (0) do posicionamento atual do tap e o bloco

pTap informa se haverá (1) ou não (0) mudança no posicionamento do tap. Os reguladores de tensão. Os blocos If´s são responsáveis por esse controle nos degraus, então se

uma regulação de tensão necessita mais do que 16 degraus para cima ou para baixo os

blocos If´s limitam essa mudança assim como é feito nos reguladores de tensão atuais.

Na parte inferior central da Figura 4.11 existem dois blocos com os valores 0.00625

e −0.00625 que são os valores em p.u. aos quais serão incrementados ou rebaixados

ao valor de tensão de saída do regulador se houver uma mudança de tap1

4.2.8

A UCAT (Unidade de cálculo das tensões)

Este subsistema é composto por duas memórias ROM , um contador, operadores lógicos

e aritméticos. A UCAT tem a sua principal tarefa, de ao final da simulação, durante o

estado S8 da máquina de estados MdEcaPerfil, gerar e armazenar os novos perfis de

tensão do alimentador, como mostrado na Figura 4.12, provocados pelas mudanças nos

taps dos reguladores.

1

Considerando os reguladores de distribuição atualmente produzidos com faixas de regulação iguais

a +-10% da tensão de linha, um degrau corresponde a aproximadamente 5/8% da sua tensão de base

correspondente a 0,625% de sua tensão nominal. Para 13.8 KV igual a 86,25V ou 0.00625 p.u.

36

Figura 4.12: Unidade de cálculo das tensões

A UCAT foi toda desenvolvida com base na Equação 4.12, que foi obtida a partir da

equação 4.8.

Vj = Vjant +

∂Vj

∂Vi

(Viat − Viant )

(4.12)

onde:

∂Vj

∂Vi

- Coeficiente de tensão.

Viat - Tensão de saída atingida no nó regulador i.

Na Figura 4.12 têm-se três blocos denominados DeltaVi, DeltaVj e vVj. De acordo

com a Equação 4.12 eles calculam respectivamente a diferença entre a tensão de saída

atingida no nó regulador i e tensão de saída anterior a uma regulação de tensão no nó

regulador i (DeltaVi); o produto entre o coeficiente de tensão e a diferença entre as

tensões (Viat e Viant ) (DeltaVj) e por último a soma entre DeltaVi e DeltaVj (vVj) para

chegar ao resultado do V j. As memórias ROM utlizadas na UCAT foram utilizadas

com o mesmo propósito para o qual foram utilizadas no bloco UAT, ou seja, passar os

valores referentes aos perfis de tensão e coeficientes de tensão.

Como dito anteriormente, o bloco UCAT só atua no estado S8 da máquina de estados MdEcaPerfil, ou seja, ao término das operações da UAT e UCT, no entanto, ele

é de grande importância para a validação do simulador. O bloco UCAT é responsável

por gerar vetores com número de nós (vnNohs), tensão de regulação anterior a uma variação de tensão no nó j (Vjant ) e a tensão de regulação no nó j (Vj ). Estes vetores

R onde foi desenvolvido um algoritmo em .m

são informados ao workspace do Matlab,

37

R para gerar gráficos. Este algoritmo é chamado de PLOTAR 1. O

(extensão do Matlab)

algoritmo .m

PLOTAR 1

como também a descrição do simulador em VHDL podem ser

vistos no CD em anexo a este documento.

O algoritmo para desenvolvimento de gráficos, foi feito com o objetivo de comparação entre os resultados obtidos com o simulador do comportamento de bancos trifásicos

de reguladores de tensão e os resultados obtidos pelo programa de análise de fluxo de

cargas (TOpReDE). A análise dos resultados obtidos será discutida no capítulo 5.

38

Capítulo 5

Resultados e discussões

Este capítulo apresenta os resultados alcançados a partir do simulador do comportamento de bancos trifásicos de reguladores de tensão. A análise de tais resultados, baseiase na comparação dos resultados do simulador com os resultados obtidos pelo programa

de análise de fluxo de carga, o TOpReDE, como forma de validação do simulador.

5.1

Comparação de resultados

O simulador foi implementado com base nos coeficientes das funções que definem a

sensibilidade de tensão (coeficientes de tensão) para cada nó presente em um alimentador. Como forma de validação no uso destes coeficientes de tensão para definição do

novo perfil de tensão do alimentador, em resposta a variações de tensão, tomando como

base alguns alimentadores, foram feitas algumas análises.

Na Tabela 5.1 estão representados os dados referentes aos nós 10 e 12 de um alimentador real, de 56 nós, após uma determinada variação de tensão na saída do nó

regulador, nó 7, para este caso. Este mesmo alimentador de 56 nós será utilizado em

todas as análises feitas neste capítulo. A Tabela 5.1 tem como objetivo demonstrar os

resultados obtidos pelo simulador e também fazer uma comparação com os resultados

obtidos no programa TOpReDE.

39

Nó 10

Tabela 5.1: Tabela para comparação com o TOpReDE

A

B

C

Nó 12

A

B

Vjant

0.9546

0.9604

0.9644

Vjant

0.9381

Vjdes

0.90

0.92

0.94

Vjdes

0.90

VjSim

0.9046

0.9292

0.9457

VjSim

0.9068

0.9265 0.9443

VjT .M aior

0.9409

0.9410

0.9450

VjT .M aior

0.9373

0.9388 0.9439

VjT .M edia

0.9229

0.9330

0.9270

VjT .M edia

0.9212

0.9228 0.9280

VjT .M enor

0.9027

0.9030

0.9067

VjT .M enor

0.9047

0.9062 0.9114

Viant

0.9942

0.9979

1

Viant

0.9942

0.9979

Viest

0.9396

0.9574

0.9755

Viest

0.9561

0.9726 0.9894

Viat

0.9442

0.9666

0.9812

Viat

0.9630

0.9791 0.9937

Pos. tap

-8

-5

-3

Pos. tap

-5

Dif. Viest

0.0046

0.0091

0.0056

Dif. Viest

0.0068

C

0.9453 0.9505

0.92

-3

0.94

1

-1

0.0065 0.0042

Testes com diferentes alimentadores e diferentes tensões foram feitos para validação

dos resultados do simulador. Uma primeira análise feita foi a das tensões dos nós regulados VjSim . Onde pela Tabela 5.1 se observam: Vjant (tensão anterior a uma regulação

de tensão nas três fases do nó 10, caso base); Vjdes (tensão de regulação desejada no nó

10 para as três fases); VjSim (tensão de regulação no simulador, ou seja, é a tensão de

saída dos nós regulados, calculada pelo simulador após um ajuste de tensão); VjT .M aior ,

VjT .M edia e VjT .M enor (tensão de regulação no TOpReDE, ou seja, é a tensão de saída

dos nós regulados calculada pelo TOpReDE após um ajuste de tensão). Comparando

os valores da Vjdes e VjSim nota-se que são muito próximas, levando a concluir que o

simulador gerou os resultados esperados. Uma comparação importante é a VjSim com

as VjT .M aior , VjT .M edia e VjT .M enor . Um detalhe importante desta comparação é o fato

do programa de análise de fluxo de carga (TOpReDE) não aceitar como entrada a Vjdes ,

o mesmo somente aceita como entrada um valor de tensão para a saída do regulador,

diferente do simulador, onde se tem a possibilidade de três valores distintos para os reguladores de tensão. Desse modo, houve a necessidade de passar ao programa de análise

de fluxo de carga os valores das tensões atingidas nos reguladores, Viat , porém, como a

simulação é feita com três reguladores houve a necessidade de informar o maior valor,

o menor valor e a média dos valores dos três reguladores e então analisar os resultados.