Capítulo 2

Coletores Abertos e Tri-State

Sumário

2.2

Saídas de coletor aberto e de dreno aberto.................................................................... 4

2.3

Buffers / drivers de coletor aberto e de dreno aberto.................................................... 6

2.3.1

Símbolo IEEE/ANSI para saída de coletor aberto e dreno aberto ............................... 6

2.4

Saídas lógicas tristate (três estados) .............................................................................. 8

2.4.1

Vantagem do tristate..................................................................................................... 9

2.4.2

Buffers tristate............................................................................................................... 9

2.4.3

CIs tristate................................................................................................................... 10

2.4.4

Símbolo IEEE/ANSI para saídas tristate .................................................................... 11

2.5

Interface lógica de barramento de alta velocidade ...................................................... 12

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

2.1 SAÍDAS DE COLETOR ABERTO E DE DRENO ABERTO

Existem situações nas quais diversos dispositivos digitais têm de compartilhar o uso de

um único fio para transmitir um sinal para um dispositivo de destino, situação muito

parecida com aquela em que vários vizinhos compartilham a mesma rua. Isso significa

que vários dispositivos devem ter suas saídas conectadas no mesmo fio que

basicamente conecta todos eles um ao outro. Para todos os dispositivos lógicos

considerados até este momento, isso representa um problema. Cada saída tem dois

estados, ALTO e BAIXO. Quando uma saída está em nível ALTO enquanto a outra está

em nível BAIXO, e quando elas são conectadas juntas, temos um conflito ALTO / BAIXO.

Quem ganhará? Assim como em uma luta de braço, o mais forte dos dois ganha. Nesse

caso, o circuito com transistor cujo transistor de saída tiver a menor resistência no estado

"ON” conduzirá a saída em sua direção.

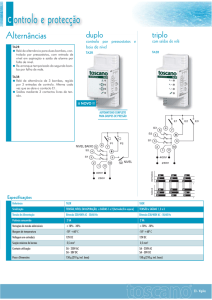

A Figura 1 mostra um diagrama em bloco genérico de dois dispositivos lógicos com suas

saídas conectadas em um fio comum. Se os dois dispositivos forem CMOS, então a

resistência no estado ON do circuito pull-up que tem como saída um nível ALTO, será

aproximadamente a mesma que a resistência ON do circuito pull-down que apresenta

uma saída de nível BAIXO. A tensão no fio comum estará em torno da metade da tensão

de alimentação. Essa tensão está na faixa indeterminada para a maioria das séries

CMOS e é inaceitável para acionar uma entrada CMOS. Além disso, a corrente através

dos dois MOSFETs em condução será muito maior que o normal, especialmente para

valores maiores que VDD e isso pode danificar os CIs.

As saídas CMOS de dispositivos convencionais nunca devem ser conectadas

juntas.

Se os dois dispositivos fossem TIL com saídas totem-pole conforme é mostrado na

Figura 2, uma situação similar ocorreria, mas com resultados diferentes devido a

diferença no circuito de saída. Suponha que a saída da porta A esteja no estado ALTO

(Q3A ON, Q4A OFF) e a saída da porta B esteja no estado BAIXO (Q3B OFF, Q4B ON).

Nessa situação, Q4B tem uma resistência de carga muito menor que Q3A e drenará uma

corrente que será muito maior que a corrente para a qual ele foi projetado. Essa corrente

pode não danificar Q3A ou Q4B imediatamente, mas durante um período de tempo, ela

pode causar sobreaquecimento deteriorando a performance e provocando um eventual

dano ao dispositivo.

2

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

Figura 1. Duas saídas competindo para o controle de um fio.

Outro problema causado por essa corrente relativamente alta fluindo através de Q4B é

que ela produzirá uma grande queda de tensão entre coletor e emissor do transistor,

fazendo VOL se situar entre 0,5 e 1 volt. Isso é maior do que o valor VOL(máx) permitido.

Por essas razões:

As saídas TTL totem-pole nunca devem ser conectadas juntas.

Figura 2. Saídas totem-pole conectadas juntas podem produzir uma corrente

muito alta através de Q4.

3

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

2.2 Saídas de coletor aberto e de dreno aberto

Uma solução para o problema do compartilhamento de um fio comum entre portas

lógicas é remover o transistor pull-up ativo do circuito de saída de cada porta. Dessa

maneira, nenhuma das portas tentará insistir no nível lógico ALTO. Os circuitos de saída

CMOS que tenham sido modificados dessa maneira são denominados saídas de dreno

aberto. A saída é tomada no dreno do MOSFET pull-down canal-N, que é um circuito

aberto (isto é, não está conectado em um outro circuito).

A saída TTL equivalente é chamada de saída de coletor aberto, porque o coletor do

transistor da parte inferior do totem-pole é conectado diretamente no pino de saída e em

nenhum outro ponto, conforme é mostrado na Figura 3(a). A estrutura de coletor aberto

elimina os transistores pull-up Q3, DI e R4. Com a saída no estado BAIXO, Q4 está ON

(tem corrente de base e essencialmente apresenta um curto entre coletor e emissor);

com a saída no estado ALTO, Q4 está OFF (não tem corrente de base e essencialmente

apresenta um circuito aberto entre coletor e emissor). Visto que o circuito não tem

internamente um caminho para estabelecer uma saída de nível ALTO, o projetista do

circuito tem de conectar um resistor de pull-up, Rp, externo na saída conforme é

mostrado na Figura 3(b).

Quando Q4 está ON, ele faz com que a tensão de saída seja uma tensão de nível

BAIXO.Quando Q4 está OFF, Rp faz com que a saída da porta esteja em nível ALTO.

Observe que sem o resistor de pull-up, a tensão de saída seria indeterminada (flutuante).

O valor do resistor Rp é geralmente escolhido como sendo de 10kΩ. Esse valor é

pequeno o suficiente de modo que a queda de tensão no estado ALTO devido à corrente

de carga não diminuirá a tensão de saída abaixo do VOH mínimo. Esse resistor tem um

valor alto o suficiente para que no estado BAIXO ele limite a corrente através de Q4 a um

valor abaixo de IQL(máx).

Quando várias portas com saídas de coletor aberto ou de dreno aberto compartilham

uma conexão em comum conforme é mostrado na Figura 4, o fio comum está em nível

ALTO devido ao resistor de pull-up. Quando qualquer uma (ou mais de uma) das saídas

das portas estiverem em nível BAIXO, haverá uma queda de tensão de 5V sobre o

resistor Rp e o ponto de conexão comum estará no estado BAIXO.Visto que a saída

comum estará em nível ALTO apenas quando todas as saídas estiverem no estado

ALTO, conectando as saídas dessa maneira implementamos, essencialmente, a função

lógica AND. Isso é denominado conexão wired-AND. Isso é mostrado simbolicamente

pelo símbolo de uma AND desenhada pontilhada. Na realidade, a porta AND não existe.

Uma conexão wired AND pode ser implementada apenas com dispositivos m de coletor

aberto ou dispositivos CMOS de dreno aberto.

Resumindo, os circuitos de coletor aberto e de dreno aberto não são capazes de fazer

suas saídas irem para o estado ALTO por meio de um circuito ativo; eles podem apenas

fazer com que elas estejam em nível BAIXO. Essa característica pode ser usada para

possibilitar que vários dispositivos compartilhem o mesmo fio para transmitirem um nível

lógico para outro dispositivo, ou combinar efetivamente as saídas dos dispositivos em

uma função lógica AND. Conforme já visto, a finalidade do transistor pull-up ativo no

circuito de saída de uma porta convencional é carregar rapidamente a capacitância de

carga permitindo um chaveamento rápido. Os dispositivos de coletor aberto e dreno

aberto têm uma velocidade de chaveamento muito lenta de nível BAIXO para nível ALTO

e, conseqüentemente, não são usados em aplicações de alta velocidade.

4

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

Figura 3. (a) Circuito TTL de coletor aberto; (b) com resistor pull-up externo.

Figura 4. Operação wired-AND usando portas de coletor aberto.

5

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

2.3 Buffers / drivers de coletor aberto e de dreno aberto

As aplicações de saídas de coletor aberto e de dreno aberto foram muito mais

predominantes na época do surgimento dos circuitos lógicos do que hoje em dia. O uso

mais comum desses circuitos agora é como buffer/driver. Um buffer, ou um driver, é um

circuito lógico projetado para ter uma capacidade de corrente e/ou tensão de saída maior

que um dispositivo lógico comum. Eles permitem que uma saída de circuito de pequena

capacidade possa acionar uma carga que exige maior corrente. Os circuitos de coletor

aberto e de dreno aberto oferecem, de um certo modo, uma flexibilidade única para

buffers/drivers.

Devido às suas especificações altas para IQL e VOH, o 7406 e 7407 são os únicos

dispositivos TIL padrão ainda recomendados para novos projetos. O 7406 é um CI

buffer/driver de coletor aberto que contém seis INVERSORES com saídas de coletor

aberto capazes de absorver até 40 mA no estado BAIXO. Além disso, o 7406 é capaz de

lidar com tensões de saída de até 30 volts no estado ALTO. Isso significa que a saída

pode ser conectada em uma carga que opera com uma tensão maior que 5 V.

Isso está ilustrado na Figura 5, em que um 7406 é usado como um buffer entre um flipflop 74LS112 e uma lâmpada incandescente de 24 V e 25 mA. O 7406 controla o estado

ON/OFF da lâmpada para indicar o estado da saída Q do flip-flop. Observe que a

lâmpada é alimentada com +24 V e funciona como um resistor de pull-up para a saída de

coletor aberto.

Quando Q = 1, a saída do 7406 vai para o nível BAIXO, seu transistor de saída absorve

os 25 mA da corrente da lâmpada alimentada pela fonte de 24 V e a lâmpada fica ligada.

Quando Q = O, o transistor de saída do 7406 é desligado, não há um caminho para a

passagem de corrente e a lâmpada fica desligada. Nesse estado, toda a tensão de 24 V

aparece sobre o transistor de saída, que está OFF, logo VOH= 24 V, que é menor do que

o parâmetro VOHmáximo do 7406.

Saídas de coletor aberto são freqüentemente usadas para acionar LEDS conforme é

mostrado na Figura 6(a). O resistor é usado para limitar a corrente em um valor seguro.

Quando a saída do INVERSOR estiver em nível BAIXO, seu transistor de saída

proporcionará um caminho de baixa resistência para GND para a corrente do LED,

assim, o LED estará ligado. Quando a saída do INVERSOR estiver em nível ALTO, seu

transistor de saída estará desligado e não haverá um caminho para a corrente do LED;

nesse estado, o LED estará desligado.

O 7407 é um buffer não inversor de coletor aberto com os mesmos parâmetros de

tensão e corrente que o 7406.

O 74HC05 é um CI inversor sêxtuplo de dreno aberto com capacidade de absorver

corrente de até 25 mA. A Figura 6(b) mostra uma maneira de fazer uma interface de um

FF D 74AHC74 com um relé de controle. Um relé de controle é uma chave

eletromagnética. Os contatos se fecham magneticamente quando a corrente projetada

flui pela bobina. O 74HC05 é capaz de lidar com relés de correntes e tensões

relativamente altas, de modo que a saída do 74AHC74 possa ligar e desligar o relé.

2.3.1 Símbolo IEEE/ANSI para saída de coletor aberto e dreno

aberto

A nova simbologia IEEE/ANSI usa uma notação diferente para identificar saídas de

coletor aberto e de dreno aberto. A Figura 7 mostra a representação no padrão

IEEE/ANSI para uma saída de coletor aberto ou de dreno aberto. É um losango

sublinhado. Embora a simbologia IEEE/ANSI não seja usada normalmente neste livro,

usaremos esse losango sublinhado para indicar saídas de coletor aberto e de dreno

aberto.

6

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

Figura 5. Um buffer/driver com saída de coletor aberto aciona uma

carga de alta corrente e de alta tensão

Figura 6. (a) Uma saída de coletor aberto pode ser usada para

acionar um LED; (b) uma saída CMOS de dreno aberto.

Figura 5. s

Figura 6. d

Figura 7. Notação IEEE/ANSI para saídas de coletor aberto e de dreno aberto.

7

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

Questões para Revisão

1. Em que situação ocorre um conflito entre os níveis lógicos ALTO / BAIXO?

2. Por que não se deve conectar saídas totem-pole juntas?

3. Em que as saídas de coletor aberto diferem das saídas totem-pole?

4. Por que uma saída de coletor aberto precisa de um resistor de pull-up?

5. Qual é a expressão lógica para a conexão das seis saídas de um 7406?

6. Por que as saídas de coletor aberto são, geralmente, mais lentas do que

as saídas totem-pole?

7. Qual é o símbolo IEEE/ANSI para as saídas de coletor aberto?

2.4 SAÍDAS LÓGICAS TRISTATE (TRÊS ESTADOS)

A configuração tristate é um terceiro tipo de circuito de saída usado nas famílias TTL e

CMOS. Esse tipo de saída aproveita a vantagem da operação em alta velocidade das

configurações de saída pull-up/pull-down ao mesmo tempo, permitindo que as saídas

sejam conectadas juntas para compartilharem um fio comum. Ela é denominada tristate

porque permite três estados na saída: ALTO, BAIXO e alta impedância (Hi-Z). O estado

de alta impedância é uma condição na qual os dois transistores, pull-up e pull-down, são

desligados (OFF) de modo que o terminal de saída fica em alta impedância tanto para

GND quanto para a tensão de alimentação +v. A Figura 8 ilustra esses três estados para

um simples circuito inversor.

Dispositivos com saídas tristate têm uma entrada enable (habilitar). Essa entrada é

freqüentemente denominada E para enable ou OE para output enable. Quando OE =1,

conforme mostrado na Figura 8(a) e (b), o circuito opera como um INVERSOR normal

porque o nível lógico ALTO em OE habilita a saída. A saída estará em nível ALTO ou

BAIXO dependendo do nível da entrada. Quando OE = O, conforme mostrado na Figura

8.35(c), a saída do circuito é desabilitada. A saída entra no estado de alta impedância

tendo os dois transistores de saída em corte. Nesse estado, o terminal de saída é

essencialmente um circuito aberto (não está eletricamente conectado em nada).

Figura 8. Três condições de saída tri-state.

8

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

2.4.1 Vantagem do tristate

As saídas dos CIs com tristate podem ser conectadas juntas (compartilhando o uso de

um fio comum) sem sacrificar a velocidade do chaveamento. Isso é conseguido graças à

saída tristate que, quando habilitada, opera como uma saída totem-pole para TTL ou um

pull-up/pull-down CMOS com suas características associadas de baixa impedância e alta

velocidade. Entretanto, é importante perceber que quando saídas tristate estão

conectadas juntas, apenas uma delas deve ser habilitada de cada vez. Caso contrário,

duas saídas ativas competiriam pelo controle do fio comum, conforme discutimos antes,

provocando altas correntes e produzindo níveis lógicos inválidos.

Em nossa discussão sobre circuitos de coletor aberto, de dreno aberto e tristate, temos

mencionado casos em que as saídas de vários dispositivos têm de compartilhar um

único fio para transmitir informação para outro dispositivo. O fio compartilhado é referido

como linha de barramento. Um barramento de entrada é construído com várias linhas

(fios) que são usadas para transportar uma informação digital entre dois ou mais

dispositivos que compartilham o uso do barramento.

2.4.2 Buffers tristate

Um buffer tristate é um circuito usado para controlar a passagem de um sinal lógico da

entrada para a saída. Alguns buffers tristate também invertem o sinal que passa por eles.

Os circuitos mostrados na Figura 8 podem ser denominados buffer tristate inversores.

Dois CIs buffers tristate usados comumente são o 74LS125 e o 74LS126. Ambos contêm

quatro buffers tristate não inversores como os que são mostrados na Figura 9. O

74LS125 e o 74LS126 se diferem apenas no estado ativo de suas entradas ENABLE. O

74LS125 permite que o sinal na entrada A alcance a saída quando E = O, enquanto o

74LS126 permite a passagem do sinal de entrada quando E = 1.

Figura 9. Buffers tristate não inversores.

Os buffers tristate têm muitas aplicações em circuitos nos quais diversos sinais são

conectados a linhas comuns (barramentos). Podemos ter uma idéia básica a partir da

Figura 10(a). Nesse caso, temos os três sinais lógicos A, B e C conectados em uma linha

de barramento comum através de buffers tristate 74AHC126. Essa configuração permite

transmitir qualquer um desses três sinais pela linha de barramento para outros circuitos,

habilitando-se o buffer apropriado.

Por exemplo, considere a situação mostrada na Figura 10(b) em que EB = 1 e EA = EC =

O. Isso desabilita os buffers das partes superior e inferior, de modo que suas saídas

9

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

estarão em alta impedância e estarão, essencialmente, desconectadas do barramento.

Isso está simbolizado por um X no diagrama. O buffer da parte central está habilitado;

assim, o sinal em sua entrada, B, passa para sua saída e, conseqüentemente, para o

barramento, de onde é levado para outros circuitos conectados no barramento. Quando

saídas tristate são conectadas juntas, conforme é mostrado na Figura 8.37, é importante

lembrar que não mais que uma saída deve ser habilitada de cada vez. Caso contrário,

duas ou mais saídas totem-pole ativas seriam conectadas, o que produziria correntes

elevadas. Ainda que não ocorra nenhum dano, a situação produziria um sinal no

barramento que seria a combinação de mais de um sinal. Isso é normalmente

denominado contenção de barramento. A Figura 11 mostra o efeito da habilitação das

saídas A e B simultaneamente. Na Figura 10, quando as entradas A e B estão em

estados opostos, elas competem pelo controle do barramento. A tensão resultante no

barramento é um estado lógico inválido. Em sistemas de barramento tristate, o projetista

tem de garantir que o sinal de habilitação não permitirá que a contenção de barramento

ocorra.

Figura 10. (a) Buffers tristate usados para conectar alguns sinais a um barramento

comum; (b) condições para transmitir o sinal B para o barramento.

2.4.3 CIs tristate

Além dos buffers tristate, muitos CIs são projetados com saídas tristate. Por exemplo, o

74LS374 é um CI registrador de oito FFs do tipo D com saídas tristate. Isso significa que

ele é um registrador de oito bits construídos com FFs D cujas saídas são conectadas em

buffers tristate. Esse tipo de registrador pode ser conectado em linhas comuns de

barramento, juntamente com as saídas de outros dispositivos similares, para emitir uma

transferência eficiente de dados pelo barramento. Outros tipos de dispositivos lógicos

disponíveis com saídas tristate incluem decodificadores, multiplexadores, conversores

analógico-digital, chips de memória e microprocessadores.

10

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

Figura 11. Se duas saídas CMOS habilitadas forem conectadas juntas, o

barramento terá uma tensão de aproximadamente VDD/2 quando as saídas

tiverem níveis diferentes.

2.4.4 Símbolo IEEE/ANSI para saídas tristate

A simbologia lógica tradicional não tem notação especial para saídas tristate. A Figura 12

mostra a notação usada na simbologia IEEE/ANSI para indicar uma saída tristate. Essa

notação é um triângulo que aponta para baixo. Embora essa notação não seja parte da

simbologia tradicional, usaremos esse triângulo para indicar saídas tristate no restante

deste livro.

Figura 12. Notação IEEE/ANSI para saídas tristate.

Questões para Revisão

1. Quais são os três estados possíveis de uma saída tristate?

2. Qual é o estado de uma saída tristate quando ela está desabilitada?

3. O que é contenção de barramento?

4. Que condições são necessárias para transmitir o sinal C pelo barramento

mostrado na Figura 8.37?

5. Qual é a notação IEEE/ANSI para saídas tristate?

11

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

2.5 INTERFACE LÓGICA DE BARRAMENTO DE ALTA

VELOCIDADE

Muitos sistemas digitais usam um barramento compartilhado para transferir sinais digitais

e dados entre diversos componentes do sistema. Como se pode ver a partir do

desenvolvimento da tecnologia CMOS, os sistemas estão ficando cada vez mais rápidos.

Muitas das recentes séries lógicas de alta velocidade são projetadas especificamente

para interface em sistemas com barramento tristate. Os componentes nessas séries são

principalmente buffers tristate, transceptores bidirecionais, latches e acionadores

(drivers) de linha de alta corrente.

Freqüentemente, uma distância significante separa fisicamente os dispositivos nesses

sistemas. Se essa distância for maior que quatro polegadas (aproximadamente

10,16cm), os fios que formam o barramento entre os dispositivos têm de ser vistos como

uma linha de transmissão. Embora a teoria sobre linha de transmissão possa ocupar um

livro inteiro, e estar além do objetivo deste livro, a idéia geral é suficientemente simples.

Os fios têm indutância, capacitância e resistência, o que significa que para sinais que

variam (CA) os fios têm uma característica de impedância que pode afetar um sinal

colocado em uma das extremidades e destorcê-lo quando ele alcança a outra

extremidade. Em sistemas de altas velocidades, sobre os quais estamos discutindo, os

tempos envolvidos diminuem o tamanho dos fios, e os efeitos de ondas refletidas

(semelhantes a ecos) e as oscilações se tornam uma preocupação real. Existem

diversas formas de combater os problemas associados às linhas de transmissão. Para

evitar pulsos de onda refletidos, o final do barramento tem de ter uma terminação com

uma resistência que seja igual à impedância da linha (em torno de 50Q) conforme

mostrado na Figura 13(a). Esse método não é prático devido à grande corrente requerida

para manter as tensões dos níveis lógicos através de resistências tão baixas. Outra

técnica usa um capacitor para bloquear a corrente contínua quando a linha não estiver

variando, mas nas bordas de subida e descida dos pulsos, apenas o resistor aparece

efetivamente. Esse método é mostrado na Figura 13(b).

Usando um divisor de tensão, conforme mostrado na Figura 13(c), com resistências

maiores que a da linha, a impedância ajuda a reduzir as reflexões, porém, com centenas

de linhas individuais de barramento, obviamente, isso se torna uma carga de alto

consumo para a fonte de alimentação. A terminação com diodos, conforme mostrado na

Figura 13(d), simplesmente ceifa os overshoot/undershoot1 das oscilações causadas

pelo comportamento reativo da indutância (L) e da capacitância (C) natural da linha.

Terminações em série com o dispositivo-fonte, conforme é mostrado na Figura 13(e),

diminuem a velocidade de chaveamento, reduzindo a freqüência limite do barramento,

porém, melhorando substancialmente a segurança dos sinais no barramento.

Como se pode ver, nenhum desses métodos é ideal. Os fabricantes de CIs estão

projetando novas séries de circuitos lógicos que superam muitos desses problemas. As

séries lógicas de interfaces de barramento da Texas Instruments oferecem novos

circuitos de saída que diminuem dinamicamente a impedância de saída durante as

transições do sinal para proporcionar tempos de transições menores; durante o estado

estacionário, a impedância aumenta (semelhante à terminação em série) para amortecer

qualquer oscilação e reduzir reflexões na linha do barramento. A série BTL (lógica

transceptora para placa-mãe) de dispositivos de interface de barramento é

especialmente projetada para acionar barramentos relativamente longos que conectam

módulos de um grande sistema digital. Através da placa-mãe (backplane), os módulos

são interconectados em um padrão industrial de sistema de montagem em rack de 19”. A

lógica GTL (lógica transceptora para placas reduzidas) é mais adequada para

barramentos de alta velocidade em uma placa de circuito única, ou entre placas

acomodadas em um pequeno espaço como um gabinete de um computador pessoal.

1

* Considere que um sinal esteja sendo ajustado em um determinado nível de operação. Caso o nível do

sinal supere, momentaneamente, o nível de operação, retomando em seguida, dizemos que ocorreu um

overshoot. Caso o nível do sinal caia abaixo do nível de operação estipulado, dizemos que ocorreu um

undershoot. (N. T.)

12

Capítulo 2: Coletores Abertos e Tri-State

Grupo de Sistemas Digitais – EESC/USP

Figura 13. Técnicas de terminação de barrramento.

13