Anexo A1

Capítulo 1

1

Fig. A.1. Fotografia mostrando o interior do microprocessador MIPS R3000. No lado direito do chip, pode-se

ver a parte operativa. O lado superior esquerdo contem a unidade de controle. O canto inferior esquerdo contem

a parte do sistema de memória chamada "Translation Lookaside Buffer", ou seja, a memória cache do

microprocessador.

2

Fig. A.2. Fotografia mostrando o interior do microprocessador MIPS R4000. A pastilha tem a dimensão de

1,5cm por 1,1cm, contendo cerca de 1,3 milhão de transistores. No lado direito do chip pode-se ver a parte

operativa para cálculo de operações com números inteiros, enquanto que o lado esquerdo contem a parte

operativa para cálculos em ponto flutuante. A unidade de controle está no centro do chip e os dois grandes

blocos no alto são as memórias cache do microprocessador.

3

Fig. A.3. Fotografia de um wafer de 6 polegadas contendo microprocessadores MIPS R4000 (esquerda) e um

wafer de 6 polegadas contendo microprocessadores MIPS R3000 (direita). O número de pastilhas do R3000 no

wafer da direita, para um rendimento de 100%, é 210. Cada pastilha mede 0,8 x 0,9cm2 e contem cerca de

125.000 transistores. O número de pastilhas do R4000 no wafer da esquerda, para um rendimento de 100%, é de

59. O tamanho da pastilha é 1,5 x 1,1cm2 e cada pastilha contem cerca de 1,3 milhão de transistores. Alguns

dos chips do R3000 colocados nas bordas do wafer não serão utilizados; eles foram incluídos porque é mais fácil

para se criar as máscaras para imprimir o circuito no silício. Os retângulos "vazios" em ambos wafers contém

circuitos de teste usados para rapidamente se testar o wafer. O wafer do MIPS R4000 tem quatro circuitos de

teste adicionais nas bordas.

Fig. A.4. Fotografia do microprocessador Intel 4004, de 1971, o primeiro microprocessador. A pastilha tem a

dimensão de: 0,3 x 0,4cm2 e possui 2.300 transistores.

4

Anexo A2

Capítulo 4

5

Anexo A3

Exercícios

6

Capítulo 1

1. Encontre a palavra ou frase na lista abaixo que melhor se enquadra na descrição das

questões q1 à q26.

a. níveis de abstração

b. assembler

c. número binário

d. bit

e. cache

f. CPU

g. chip

h. compilador

i. família de computadores

j. parte de controle

k. parte operativa

l. defeito

m. pastilha

n. DRAM

o. implementação

p. instrução

q. arquitetura de um conjunto de instruções

r. circuito integrado LSI (large scale integration)

s. memória

t. sistema operacional

u. processador

v. semicondutor

w. supercomputador

x. transistor

y. VLSI (very large scale integration)

z. rendimento

q1. Abstração específica que o hardware fornece ao software de baixo nível:

q2. Parte ativa do computador, seguindo instruções dos programas para somar números, testar

números, etc...:

q3. Outro nome para processador:

q4. Número na base 2:

q5: Dígito binário:

q6. Coleção de implementações de computadores apresentando mesma arquitetura de

conjunto de instruções; ela é disponível ao mesmo tempo e varia em preço e performance:

q7: Componente do processador que realiza operações aritméticas:

q8: Componente do processador que controla a parte operativa, a memória e os dispositivos

de I/O de acordo com as instruções do programa:

q9: Hardware que obedece a abstração da arquitetura do conjunto de instruções:

q10. Técnica para projetar o hardware ou software; o sistema consiste de camadas de

hierarquia, onde cada camada inferior mostra detalhes da camada acima:

q11. Máquina de alta performance:

q12. Comando individual para um computador:

q13. Circuito integrado comumente utilizado para construir a memória principal:

q14. Integra dezenas à centenas de transistores dentro de um único chip:

q15. Integra centenas de milhares à milhões de transistores dentro de um único chip:

q16. Localização de programas quando estão sendo executados, contém dados necessários

também:

q17. Imperfeição microscópica de um wafer:

q18. Apelido, abreviação de uma pastilha ou circuito integrado:

q19: Chave (switch) de liga/desliga, controlada por eletricidade:

q20. Percentagem de pastilhas boas entre o número total de pastilhas no wafer:

q21. Programa que gerencia, administra um computador para o benefício dos programas que

rodam naquela máquina:

q22. Programa que traduz uma versão simbólica de uma instrução para uma versão binária

(linguagem de máquina):

7

q23. Programa que traduz uma notação em linguagem em alto-nível para a linguagem

assembler.

q24. Componente retangular que resulta da divisão de um wafer:

q25. Memória pequena e rápida que atua como um buffer para a memória principal:

q26. Material que não conduz eletricidade muito bem:

2. Usando as categorias listadas abaixo, classifique as seguintes palavras. Use as letras à

esquerda das palavras na tabela para responder. As letras destas palavras podem ser usadas

mais de uma vez.

a. software de aplicação

b. linguagem de programação de alto-nível

c. dispositivo de entrada

d. circuito integrado

e. minicomputador

q1. Apple II:

q2. Assembler:

q3. Compilador:

q4. Cray-1:

q5. DRAM:

q6. Fortran:

q7. IBM-PC:

q8. Keyboard:

f. dispositivo de saída

g. computador pessoal

h. semicondutor

i. supercomputador

j. software de sistemas

q9. Microprocessador:

q10. Mouse:

q11. Sistema operacional:

q12. Pascal:

q13. PDP-8:

q14. Impressora:

q15. Display de CRT:

3. Um disco magnético contendo dados está constantemente girando. Em média, leva-se a

metade de uma revolução completa do disco para que a informação desejada passe embaixo

da cabeça de leitura/escrita. Assumindo-se que o disco esteja girando a uma velocidade de

3600 revoluções/minuto, qual é o tempo médio para o dado desejado passar pela cabeça de

leitura/escrita do disco? E qual é o tempo se o disco estivesse girando à 5400rpm?

4. Combine as três equações [i], [ii], [iii] (pág. 4) para determinar o custo/pastilha em função

da área da pastilha. Se ignorar constantes, qual é a relação aproximada entre o custo e a área

da pastilha?

5. Qual é o custo aproximado de uma pastilha de R4000 no wafer mostado à esquerda na

figura 1.13 (pág. 11). Assuma que o wafer de 6 polegadas custa US$750,00 e que a

densidade de feito é 2/cm2. Use o número de pastilhas indicado nesta figura.

6. Mesmo exercício que o anterior, mas utilizando o wafer da direita (R3000).

8

Exercícios 7. 8. e 9.:

A cada nova geração, as pastilhas de circuitos de circuitos integrados DRAM tem

significantemente aumentado. No entanto, o rendimento do processo destes circuitos tem

permanecido aproximadamente o mesmo (43% à 48%). A tabela a seguir mostra alguns

dados estatísticos referentes à produção de memórias DRAMs entre 1980 e 1992.

7. Dado o aumento de área da pastilha de memórias DRAM, qual o parâmetro que deve ser

melhorado para se manter o mesmo rendimento?

8. Derive uma fórmula para o parâmetro que deve ser melhorado, obtido no exercício

anterior.

9. Usando a fórmula obtida no exercício anterior, qual é o melhoramento calculado para

aquele parâmetro entre 1980 e 1992?

10. Defina o termo "Hierarquia de Memória" em um computador. Quais são os parâmetros e

as heurísticas que devem ser considerados quando se deseja implementar uma hierarquia de

memória em um computador?

11. Responda às seguintes perguntas:

i) Considere uma memória RAM (Random Acess Memory = Memória de Acesso

Aleatório). Explique porque este tipo de memória é de "acesso aleatório". Um disco

magnético também é de acesso aleatório? Caso negativo, qual é o tipo de acesso? Porque?

ii) Considere uma memória SRAM (RAM estática) e outra DRAM (dinâmica).

Porque a memória SRAM é dita "estática"e a DRAM é dita "dinâmica"? Suponha que ambas

as memórias foram concebidas na mesma tecnologia e cuja pastilha de silício apresente as

dimenções de 1cm X 1cm. Neste caso: Qual das duas memórias armazena mais informação?

Porque? Qual é a mais cara em termos absolutos (preço da pastilha)? Qual é a mais cara em

termos relativos (preço/bit)? Qual é a mais rápida?

12. Defina Circuito Síncrono. Qual é a diferença entre um Circuito Combinacional Síncrono

e um Circuito Sequencial Síncrono? Um microprocessador é um circuito Combinacional ou

Sequencial? Porque?

9

13. No segmento do código C abaixo, f, g, h, i, j são variáveis.

L1:

L2:

if (i == j) goto L1;

f = g + h;

i = i + 1;

goto L2

f = g - h;

i = i - 1;

j = j + A[i];

Assuma que as 5 variáveis estão associadas aos registradores de $16 à $20 e que A é um array

de 20 elementos, cujo endereço inicial na memória é Astart. Qual é o código assembler para o

MIPS deste segmento de programa em C?

14. Assuma que as variáveis x, y, z estão associadas aos registradores $18, $19, $20.

Assuma também que o registrador $17 contem o valor de index (variável i). Qual é o código

assembler para o MIPS do seguinte comando em C:

If (x != y) A[i] = z + A[i]; else z = z + A[i];

15. Assuma que A é um array de 10 elementos cujo espaço de memória já foi alocado pelo

compilador, e que o compilador associa as variáveis w, x, y, z aos registradores $17 à $20.

Assuma também que o compilador associou o endereço Astart como o endereço inicial para o

array na memória. Traduza o trecho de programa em C abaixo para o assembler do

microprocessador MIPS:

w = A[x];

y = A[ x += z];

if (w != y) goto L1; else goto L2;

L1:

w = A[x];

y = A[x -= z];

goto L3;

L2:

A[x += y] += y;

L3:

x+= z;

10

Capítulo 2

1. Você é um usuário de computador e quer comparar a performance de dois sistemas

distintos: S1 e S2. O sistema S1 custa R$10.000 e o sistema S2 custa R$15.000. As seguintes

medidas mostradas na Tabela 1 foram publicadas para estes sistemas.

Programa

1

2

Tempo em S1

10 segundos

3 segundos

Tempo em S2

5 segundos

4 segundos

Tabela 1. Tempo de Execução.

a) Diz-se que um sistema é mais custo-efetivo do que outro se o seu quociente de

performance por custo é mais alto. Qual sistema é mais custo-efetivo para um usuário que

utiliza somente o programa 1? Por quanto?

b) Um outro usuário está interessado na capacidade de processamento de seu escritório, que

utiliza igualmente os programas 1 e 2. Que sistema é mais custo-efetivo para este usuário? Por

quanto?

c) As seguintes medidas adicionais foram feitas para os sistemas S1 e S2 executando o

programa 1.

Programa

1

Instruções Executadas em S1

6

20 x 10

Instruções Executadas em S2

6

16 x 10

Qual o valor de MIPS para o programa 1 em cada uma das máquinas?

d) Se a freqüência de clock do sistema S1 é de 20 Mhz e a freqüência de clock do sistema S2

é de 30 Mhz, qual o valor de CPI para o programa 1 nos dois sistemas?

e) Se a CPI de S2 fosse a mesma de S1 (ver questão d), quantas instruções do programa 1 S2

executaria em 5s?

f) Sabendo-se que o número de instruções em S1 para um programa 3 é de 55 x 106, qual deve

ser o valor máximo do CPI para que este programa seja executado em um tempo de CPU

igual ou menor que o do programa 1?

2. Considere duas máquinas M1 e M2. M1 possui uma freqüência de clock de 50 MHz e M2

possui uma freqüência de clock de 75 MHz. Ambas as máquinas possuem quatro classes de

instruções: A, B, C e D. Os valores de CPI para cada classe de instrução para cada máquina

são dados na tabela abaixo. Considere ainda que você está interessado em avaliar o

desempenho destas máquinas para um programa cujas instruções estão uniformemente

distribuídas entre as classes A, B, C e D. Considere também que o número de instrucões é o

mesmo em ambas as máquinas.

11

Classe

A

B

C

D

CPI em M1

1

2

3

4

CPI em M2

2

2

4

4

a) Qual máquina é mais rápida e por quanto?

b) Se desejássemos que ambas as máquinas possuíssem o mesmo desempenho (que M2)

para o programa mencionado acima, qual deveria ser a freqüência de clock de M1?

c)

Se desejássemos que ambas as máquinas possuíssem o mesmo desempenho (que M1)

para o programa mencionado acima, qual deveria ser a freqüência de clock de M2?

3. Suponha que você tem dois microcomputadores PC (de fabricantes diferentes) cuja

principal utilização é rodar duas planilhas de cálculos (uma em cada um dos PCs). Você sabe

que na primeira planilha de cálculo, 25% do tempo de processamento é gasto em operações de

ponto flutuante, enquanto que na segunda, este tempo é de 45%. Considere também que a

planilha roda em 10s e que a segunda em 23s.

Você vai ao shopping para comprar um novo coprocessador para operações em ponto

flutuante para instalar em um dos seus 2 PCs, encontrando dois modelos diferentes: um

coprocessador que acelera 5 vezes as operações em ponto flutuante, no caso do PC que roda a

primeira planilha de cálculos; e um outro coprocessador, que acelera 3 vezes o tempo para

executar as operações em ponto flutuante da máquina que roda a segunda planilha.

Pergunta: Qual dos dois coprocessadores você deve comprar? Em outras palavras, qual

deles vai gerar o maior speedup depois de instalado nos seus respectivos PCs?

4. Você está escrevendo o compilador C para uma nova máquina que será lançada

brevemente no mercado. Para um determinado comando em C você criou duas sequências

alternativas de instruções em assembler. A seqüência S1 executa 50 instruções e a seqüência

S2 executa 60 instrucões. Todas as instruções executadas em qualquer das seqüências são de

apenas 3 classes de instruções: A, B e C. Instruções da classe A executam em 1 período de

clock. Instruções da classe B executam em 2 períodos de clock e instruções da classe C

executam em 3 períodos de clock. As percentagens de instruções de cada classe executada por

cada seqüência são dadas na tabela a seguir.

Classe

S1

S2

a)

b)

Percentagem de Instruções da classe na seqüência

A

B

C

40%

20%

40%

60%

20%

20%

Qual o CPI de cada seqüência de código?

Qual seqüência de código executa mais rapidamente e por quanto?

5. Você está liderando o projeto de um novo processador. O projeto do processador e do

compilador foram completados e você precisa decidir se você vai produzir este processador

projetado ou se você vai gastar mais tempo para melhorá-lo. O seu grupo de engenharia lhe

apresenta as seguintes opções:

12

i. Deixar o projeto como está. Vamos chamar esta máquina de Mbase. Ela possui um clock de

50 Mhz, e as medidas mostradas na Tabela 1 foram feitas utilizando um simulador.

ii. Otimizar o hardware. O grupo de hardware garante que eles podem melhorar o projeto para

que a máquina trabalhe com uma freqüência de clock de 60 Mhz. Vamos chamar esta

máquina melhorada de Mótima. Um simulador foi utilizado para obter as medidas mostradas

na Tabela 2 para Mótima.

Tipo de Instrução CPI Freqüência

A

2

40%

B

3

25%

C

3

25%

D

5

25%

Tabela 1. Medidas da máquina Mbase.

a)

b)

c)

Tipo de Instrução

CPI

Freqüência

A

2

40%

B

2

25%

C

3

25%

D

4

10%

Tabela 2. Medidas da máquina Mótima.

Qual a CPI para cada máquina?

Quais os valores de MIPS nativa para Mbase e Mótima?

Quantas vezes Mótima é mais rápida do que Mbase?

d) O grupo de projetistas de compiladores ficou sabendo da discussão sobre o projeto

melhorado. Este grupo propôs que o compilador da máquina fosse reprojetado para melhorar

a performance. Vamos chamar esta máquina com compilador melhorado de Mcomp. As

melhorias conseguidas com este novo compilador foram estimadas de acordo com a Tabela 3.

Por exemplo, se a máquina base executa 500 instruções do tipo A, Mcomp executa o mesmo

programa executando 0.9 X 500 = 450 instruções tipo A. Qual a CPI de Mcomp?

Tipo de Instrução

Percentagem de Instruções

executada em relação à Mbase

A

90%

B

90%

C

85%

D

95%

Tabela 3. Instruções Executadas em Mcomp.

e)

Quantas vezes Mcomp é mais rápida do que Mbase?

f)

O grupo projetista de compiladores afirma que é possível implementar tanto as

melhorias de hardware de Mótima, quanto as melhorias de compilador de Mcomp na mesma

máquina. Suponha que a máquina com as duas melhorias seja chamada de Mambas. (Utilizar

a mesma otimização do compilador - Tabela 3 - em relação à Mótima.) Quantas vezes

Mambas é mais rápida do que Mbase?

g) O gerente de custos da empresa decidiu que apenas uma das melhorias poderá ser

incorporada no produto final, ou as melhorias de hardware de Mótima ou as melhorias do

compilador de Mcomp poderão ser implementadas. Você estima que os tempos mostrados na

Tabela 4 serão necessários para implementar estas otimizações.

Melhoria

Tempo para implementar Nome da máquina

Hardware

6 meses

Mótima

Compilador

6 meses

Mcomp

Ambas

8 meses

Mambas

Tabela 4. Tempo para implementar melhorias.

13

Você lembra ter lido em um jornal científico recentemente que as novas CPUs que tem

sido lançadas no mercado apresentam uma melhoria de performance de aproximadamente

50% por ano, ou aproximadamente 3.4% por mês. Assumindo que a máquina base possui uma

performance idêntica a dos seus competidores hoje, qual otimização você decidiria

implementar? Seria mais vantajoso lançar a máquina no mercado imediamente sem nenhuma

das modificações?

14

Capítulo 3

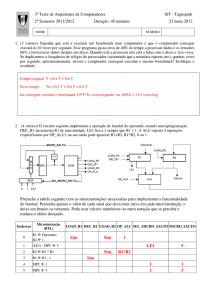

1. Um microprocessador consiste em um circuito seqüencial. Um circuito seqüencial pode

ser descrito como um conjunto de registradores e uma lógica combinacional que gera os

valores lógicos que devem ser armazenados neste conjunto de registradores a cada ciclo de

clock. A freqüência máxima de clock na qual um microprocessador pode operar é

determinada pela velocidade da lógica combinacional utilizada entre os registradores.

Portanto é importante determinar o tempo de execução de cada circuito utilizado nesta lógica

combinacional. Este tempo de execução é fortemente dependente da tecnologia utilizada para

a fabricação do componente, e esta tecnologia muda substancialmente de um ano para outro.

Uma prática comum é utilizar uma medida normalizada em unidades de tempo (ut). Para este

exercício, considere os seguintes tempos para os circuitos elementares :

• Cada porta lógica elementar, ou seja um E, um OU ou um INVERSOR possui um atraso de

1 ut.

• Um circuito multiplexador possui dois níveis lógicos, portanto seu atraso é de 2 ut.

• O tempo necessário para gerar a saída vai-um em um circuito somador elementar é de 2 ut.

• O tempo necessário para gerar a saída soma em um circuito somador elementar é de 2 ut.

a) No caso de uma soma, quanto tempo leva para gerar as saídas Vai-um e Resultado

na ULA apresentada na fig. 3.8?

b) Considere que a ULA de 32 bits da fig. 3.9 é construída com ULAs de 1 bit como a

mostrada na fig. 3.8. Quanto tempo leva para efetuar uma soma de 32 bits?

2.

Considere que uma operação de deslocamento à direita ou à esquerda leve 1 ut

independentemente do número de bits no registrador em que ela ocorre e que a ULA leve 2 ut

para somar tanto números positivos quanto negativos. Considere ainda os seguintes números

A = 0001111000111

expressos em binário:

B = 0010101010101

Indique na tabela abaixo quanto tempo (medido em unidades de tempo), as seguintes

operações necessitam para serem realizadas se os algoritmos de multiplicação indicados

forem utilizados.

Operação

AxB

BxA

Multiplicação 1

Alg. de Booth

3. Considere um computador cuja ULA opera com operandos de 32 bits. Marque com um x

em cada linha da tabela abaixo para indicar se a operação especificada resulta em overflow

quando realizada neste computador.

Operação

$7FFFFFF0

$000000FE

Resulta Overflow

+

15

Não Resulta Overflow

$00FEdCBA

$00100000

$80000001

$00000ABC

+

+

4. Considere a operação A x B onde A é o multiplicando e B o multiplicador, executada

pelos algoritmos de Multiplicação 1 e Booth apresentados em aula. Para operações de

multiplicação cujos operandos possuem 32 bits e que geram um produto de 64 bits. Escreva

na tabela abaixo quantas operações de adição/subtração são executadas para os operandos

indicados abaixo.

Operandos

Multiplicação 1

Alg. Booth

A = $0F0F 0F0F 0F0F 0F0F

B = $0000 FFFF 0000 0000

A = $0000 FFFF 0000 0000

B = $0F0F 0F0F 0F0F 0F0F

5. Considere um computador que representa números inteiros com sinal em palavras de 16

bits utilizando notação de complemento de dois. Qual é o maior número positivo e qual é o

número negativo de maior magnitude que podem ser representados neste computador?

Maior número positivo:

Número mais negativo:

6. Nas operações indicadas abaixo, os operandos estão representados em complemento de 2.

(a) $00000FFF + $00007FE0

(b) $0FFE07E0 + $0001F81F

(c) $FFFF0001 - $FFFF0000

(d) $7FABCDE0 + $F0A3F4B5

Considere que estas operações devem ser realizadas em um processador que possui

uma ULA de 32 bits. Os resultados das operações realizadas por esta ULA devem ser

armazenados também em um registrador de 32 bits. Para cada operação indique se ocorre

overflow. Se não ocorrer indique o resultado da operação em notação hexadecimal e decimal

(apresente seus cálculos).

7. Qual a representação binária e decimal dos seguintes números representados abaixo em

complemento de dois?

a. $FFFFFE0C

b. $FFFFFFFF

c. $7FFFFFFF

d. $7FFFFFFA

e. $FFFFd001

f. $007FFFE0

16

8. Considere que o circuito apresentado na fig. 3.8 é utilizado para implementar uma ULA de

1 bit. Os atrasos através de portas lógicas são normalmente contados em ns. Assuma os

seguintes atrasos para os componentes dos circuitos.

• As portas lógicas elementares (E, OU e inversor) possuem um atraso de 10 ns.

• O multiplexador de duas entradas possui um atraso de 20 ns.

• O multiplexador de três entradas possui um atraso de 30 ns.

• O somador elementar possui um atraso de 20 ns entre quaisquer entrada e saída.

Considere que uma ULA de 16 bits seja construída pela concatenação de 16 ULAs de

1 bit implementadas com o circuito descrito acima. A arquitetura da ULA de 16 bits é similar

a da fig. 3.9. Ao responder as perguntas abaixo, explique o raciocínio que você empregou

para obter o resultado.

(a) Quanto tempo leva para realizar uma soma na ULA de 16 bits?

(b) Quanto tempo leva para realizar uma subtração na ULA de 16 bits?

Capítulo 4

17

1. Quais são as possíveis causas de formação de “bolhas” em uma arquitetura em pipeline?

Que técnicas estão disponíveis para reduzir o custo da formação de bolhas nestas

arquiteturas?

2. Qual a diferença entre uma arquitetura “superpipeline” e uma arquitetura “superscalar”? É

possível construir uma máquina que seja ao mesmo tempo superscalar e superpipeline? Caso

afirmativo, como seria a organização desta máquina?

3.

Um estagiário de engenharia projetou uma máquina para operar em pipeline com

cinco estágios. Quando a máquina começou a operar, o estagiário terminou o seu estágio e

abandonou a empresa sem deixar nenhuma documentação sobre o tempo de execução de cada

estágio. Você inicia o seu estágio de informática nesta mesma empresa e seu supervisor

solicita que você escreva um programa para determinar a latência da máquina.

Para resolver o problema, você escreve dois trechos lineares de programa, isto é,

trechos de programa que não possuem desvios, e nos quais você tem certeza que não existem

dependências de qualquer natureza.

O seu primeiro trecho de programa possui 500 instruções e executa em 50.4 ms (este é

o tempo decorrido entre a busca da primeira instrução e o término da última instrução do

programa). O seu segundo trecho de programa possui 1000 instruções e executa em 100.4 ms.

Após assistir você realizando estes experimentos, o seu supervisor lhe pergunta:

a. Qual a latência do pipeline?

b. Qual é o tempo de execução do estágio mais lento deste pipeline?

4. Considere uma máquina em pipeline que utiliza previsão estática de que um branch nunca

ocorre. Esta máquina possui os seguintes tempos de operação em cada estágio:

1. Busca de instrução: 30 ns

2. Decodificação de Instrução: 35 ns

3. Execução de Instrução: 80 ns

4. Acesso à Memória: 100 ns

5. Escrita em Registradores: 45 ns

a) Qual a latência para execução de instruções nesta máquina?

b) Qual o tempo perdido por causa do aparecimento de bolhas devido ao branch no final de

um laço de 10 instruções que executa 10.000 vezes? Calcule a % na queda de desempenho.

c) Qual seria o tempo perdido se a máquina utilizasse previsão estática de que o branch

sempre ocorre? Qual seria a dificuldade adicional do projeto para implementar esta previsão?

d) Qual a freqüência de execução de instruções nesta máquina?

e) Responda a letra (b) para previsão dinâmica, supondo que o compilador setou um flag de

que este desvio ocorre.

f) Mesmo que em (e), porém previsão dinâmica para instrução que não ocorre.

18

g) A gerência de desenvolvimento solicitou que a freqüência de execução de instruções seja

dobrada utilizando-se a mesma tecnologia. Para tanto decidiu-se transformar a máquina em

uma máquina “superpipelined” aumentando-se o número de estágios no pipeline. Foi

solicitado que se usasse um número mínimo de estágios na máquina superpipelined. Como

você modificaria a máquina acima para alcançar o objetivo de dobrar a freqüência de

execução de instruções? Qual seria a nova latência?

Capítulo 5

19

1. Numa implementação simplificada de um chip de memória, são necessários no mínimo

dois pinos para alimentação elétrica, usualmente chamados de Vcc e Gnd1, um v para indicar

se a operação é de escrita ou leitura (WE), um sinal para selecionar o chip de memória (CS),

e ainda um sinal para habilitar o chip de memória (ME), entre outros. Além destes sinais de

alimentação e controle, o chip necessita ter um determinado número de linhas de dados e

endereço de acordo com a sua configuração.

Na tabela abaixo, indique o número mínimo de pinos que os chips com as

configurações dadas podem ter. Indique também quantas linhas de endereço você utilizaria

para endereçar row e column, e qual o número total de portas AND utilizadas nos

decodificadores com a sua organização.

Organização

# Pinos

Linhas para

Row

Linhas para

Column

# Portas

AND

Capacidade

(bits)

4Mx4bits

1Mx4bits

2Mx8bits

256Kx16bits

16Mx1bit

512Kx8bits

2. Considere a implementação de um sistema de memória de 16 Mbytes organizado em

palavras de 16 bits utilizando o chip µPD4216400 que possui uma organização de 4Mx4bits.

Responda:

a) Quantos chips são necessários? Projete os bancos de memória.

b) Projete a organização do espaço de endereçamento de memória.

c) Quais linhas de endereçamento devem ser usadas para selecionar os bancos de

memória? Projete o multiplexador para os bancos supondo o sinal de chip select sendo ~CS.

3. Considere um chip de memória com organização de 64Mbytesx8bits. A equipe de projeto

deste chip está considerando as configurações abaixo para o número de linhas de endereço

utilizadas para o endereçamento de row e column. Indique na tabela a seguir o número total

de portas AND que seriam usadas nos circuitos decodificadores do chip para cada

configuração.

Sabendo-se que este é um chip DRAM, e assumindo a configuração do decodificador

de 13x13 abaixo, quantos transistores são necessários para implementar o array de células e a

lógica de decodificação?

Linhas de End. p/Row

13

14

15

Linhas de End. p/Column

13

12

11

1

# total de portas AND

Em vários manuais de fabricante, você poderá verificar que muitos chips possuem mais de um pino para Gnd e

Vcc. O uso de múltiplos pinos para alimentação é uma decisão feita pelos projetistas em função de restrições de

layout interno. Nós vamos considerar que apenas dois pinos sejam necessários para alimentação.

20

4. Considere a implementação de uma memória com 32 Mbytes organizada em palavras de 8

bits utilizando o chip µPD4216800 que possui uma organização de 8Mx4bits.

a) Quantos chips são necessários?

b) Quais linhas de endereçamento devem ser usadas para selecionar bancos de

memória?

Capítulo 6

21

1.

Porque a memória cache, sendo uma memória de muito pouca capacidade de

armazenamento, consegue acelerar o processamento de uma CPU de forma tão efetiva?

2. Qual a diferença entre as técnicas de atualização de dados na cache “escrita através”

(write through) e “escrita de volta” (write back)? Quais as vantagens e desvantagens de cada

uma delas?

3. Considere um computador com uma memória principal de 16 Mbytes e uma cache de 64

Kbytes. Construa um gráfico com os valores do espaço de gerenciamento e do tamanho da

cache (medido em bits) em função do tamanho do bloco da cache (considere blocos de 8, 16,

32, 64, 128, 256, 512 e 1024 bits).

4. Considere uma cache com mapeamento direto com 16 blocos. Cada bloco do tamanho de

uma palavra. Considere que a seguinte seqüência de palavras é acessada: 1, 4, 8, 5, 20, 17, 19,

56, 9, 11, 4, 43, 5, 6, 9, 17 (endereços expressos em decimal). Assuma que a cache está

inicialmente vazia. Identifique cada um dos acessos acima como um acerto ou uma falha.

Mostre o conteúdo de toda a cache ao final da seqüência de acessos.

5. Considere uma memória principal de 1MB e uma cache de 16 Kbytes, organizada em

blocos com tamanho de 2 bytes. Qual o ÍNDICE e o TAG do bloco (expresso em

hexadecimal) no qual o endereço 78FEC da memória principal é mapeado?

6. Considere uma cache de 64 Kbytes com mapeamento direto e organizada em blocos de 8

bytes, inserida em um computador com uma memória principal de 16 Mbytes. Quantos blocos

da memória principal são mapeados em um mesmo bloco da cache?

7. Considere uma pastilha de memória estática utilizada para implementação de memória

cache. Esta pastilha é organizada em blocos contendo 1 única palavra de 16 bits, e possui uma

capacidade de 256 palavras. Considere que esta memória cache é usada com esquema de

endereçamento completamente associativo em um sistema de memória cuja capacidade de 8K

palavras. Especifique os valores relacionados abaixo.

a) Capacidade da memória medida em bytes: ____________

b) Número de bits de endereço necessários para endereçar todas as palavras da

memória:_________

c) Número de palavras da memória principal que podem ser mapeadas na mesma posição da

cache:________

d) Suponha mapeamento direto na cache, e responda novamente a letra (c).

e) Suponha mapeamento com associatividade 2 na cache, e responda novamente a letra (c).

22

8. Considere uma cache de 4Kbytes, organizada em blocos de 8 bytes e operando em um

computador que possui uma memória principal de 4 Mbytes.

a) Quantos blocos da memória principal podem ser mapeados no bloco $0010 da

memória cache?

b) Quantos bits os campos de etiqueta (tag) e índice (index) esta cache possui?

c) Qual o valor do campo de etiqueta (tag) do byte armazenado no endereço $001A

BCDE da memória principal?

9. Considere um sistema computacional baseado em microprocessador com uma memória

principal de 16 Mbytes e uma memória cache de 4 Kbytes. Assuma que a cache é organizada

em blocos de 16 bits, que o mapeamento da memória principal para a memória cache é direto,

isto é, que existe uma única posição possível na cache para cada palavra armazenada na

memória principal, e que o processador trabalha com palavras de 1 byte. Assuma também que

os seguintes valores estão armazenados nas posições especificadas da memória principal.

15

$07F300

$07F302

$07F304

$07F306

$07F308

$07F30A

$07F30C

$07F30E

0

15

0

$7A8B

$080300

$048C

$1AB300

15

0

$FAFA

$8B9C

$080302

$159D

$1AB302

$FOFO

$9CAD

$080304

$26AE

$1AB304

$DED0

$ADBE

$080306

$37BF

$1AB306

$DAD0

$BECF

$080308

$48C0

$1AB308

$F0CA

$CFD0

$08030A

$59D1

$1AB30A

$FACE

$D0E1

$08030C

$6AE2

$1AB30C

$CAFE

$E1F0

$08030E

$7BF3

$1AB30E

$C0C0

A figura a seguir mostra uma porção da memória cache. Os valores numéricos nos

campos de índice, tag e validade estão expressos em binários. No campo de dados os valores

estão expressos em números hexadecimal.

Índice

0011 0000 000

0011 0000 001

0011 0000 010

0011 0000 011

0011 0000 100

Tag

0000 0111 1111

0110 1000 0100

0000 1001 0000

0000 1100 0000

0001 1010 1011

23

V

0

0

0

0

0

15

0

Dados

$FAFA

$FOFO

$DED0

$DAD0

$F0CA

0011 0000 101

0011 0000 110

0011 0000 111

0001 1010 1011

0001 1010 1011

0001 1010 1011

1 $FACE

1 $CAFE

1 $C0C0

a)

Indique abaixo o conteúdo dos campos de Tag, Validade e Dados na cache

após uma seqüência de acessos de leitura nos endereços abaixo. Indique os valores de Tag e

Validade em números binários e o campo de Dados em hexadecimal.

$07F302, $07F304, $07F306, $080304, $080304, $07F308, $1AB30A, $1AB30C, $07F302

Índice

0011 0000 000

0011 0000 001

0011 0000 010

0011 0000 011

0011 0000 100

0011 0000 101

0011 0000 110

0011 0000 111

15

V Dados

Tag

0

b.

Quantos acessos de leitura à memória principal são feitos durante a seqüência

de acessos acima? Explique.

Capítulo 7

24

1. Porque que não é possível utilizar a técnica de “escrita através” na implementação de

sistemas de memória virtual?

2. Qual a grande vantagem de um microprocessador que contém uma TLB?

3.

Porque a técnica de escrita-através (write-through) não é compatível com a

implementação de sistemas com memória virtual?

25