3º Teste de Arquitetura de Computadores

2º Semestre 2011/2012

IST - Taguspark

Duração: 45 minutos

NOME

23 maio 2012

NÚMERO

1. (3 valores) Suponha que está a executar um benchmark num computador e que o computador consegue

executá-lo 10 vezes por segundo. Esse programa gasta cerca de 40% do tempo a processar dados e os restantes

60% a ler/escrever dados de/para um disco. Quando está a processar não está a lidar com o disco e vice-versa.

Se duplicarmos a frequência de relógio do processador (assumindo que a memória suporta isto), quantas vezes

por segundo, aproximadamente, deverá o computador conseguir executar o mesmo benchmark? Justifique o

resultado.

Tempo original T = 0,4 T + 0,6 T

Novo tempo

Tn = 0,2 T + 0,6 T = 0,8 T

Irá conseguir executar o benchmark 10*T/Tn vezes/segundo, ou 10/0,8 = 12,5 vezes/seg

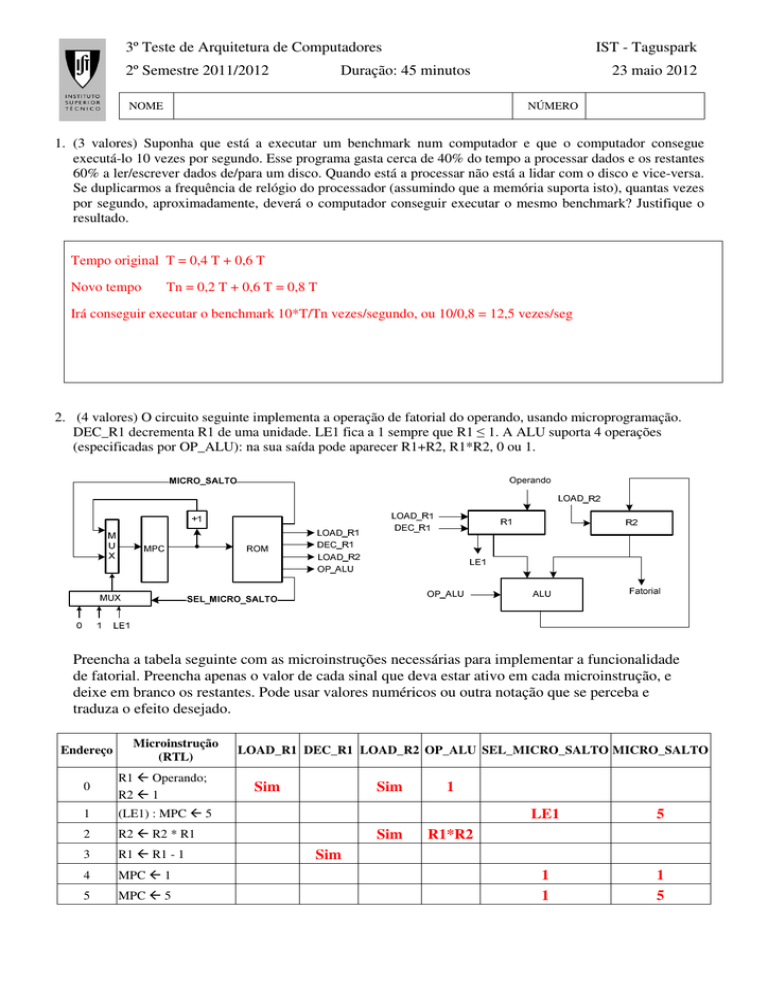

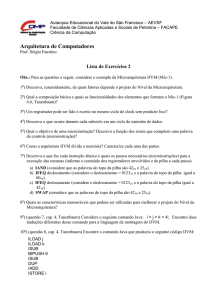

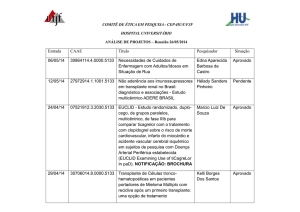

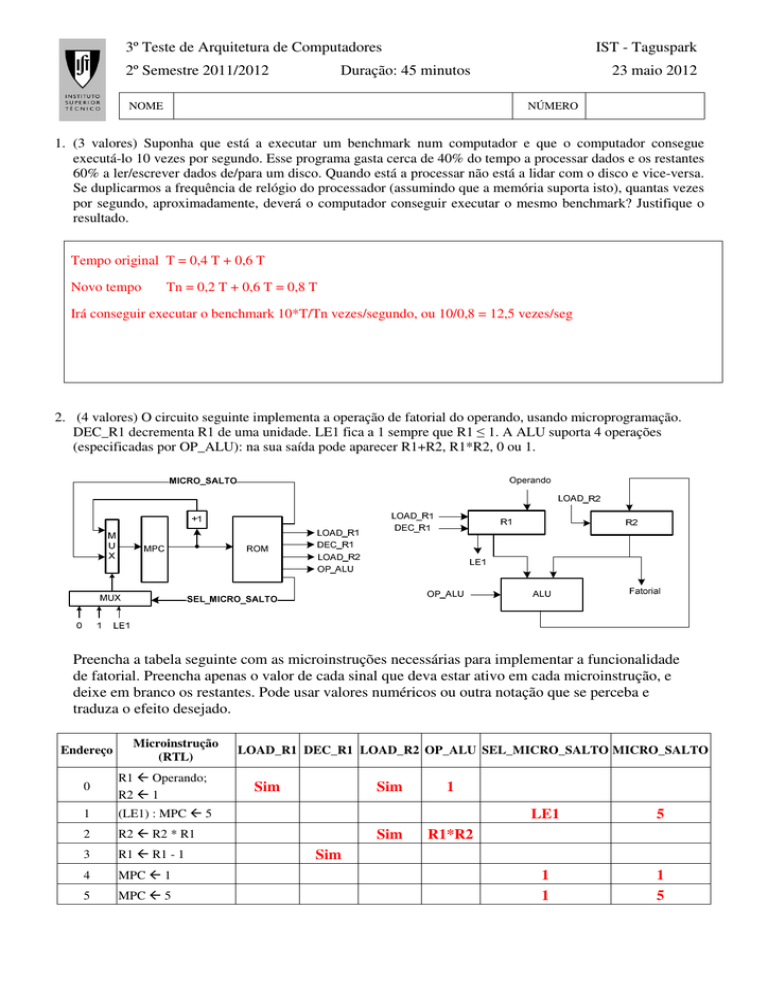

2. (4 valores) O circuito seguinte implementa a operação de fatorial do operando, usando microprogramação.

DEC_R1 decrementa R1 de uma unidade. LE1 fica a 1 sempre que R1 ≤ 1. A ALU suporta 4 operações

(especificadas por OP_ALU): na sua saída pode aparecer R1+R2, R1*R2, 0 ou 1.

Preencha a tabela seguinte com as microinstruções necessárias para implementar a funcionalidade

de fatorial. Preencha apenas o valor de cada sinal que deva estar ativo em cada microinstrução, e

deixe em branco os restantes. Pode usar valores numéricos ou outra notação que se perceba e

traduza o efeito desejado.

Endereço

Microinstrução

(RTL)

0

R1 Operando;

R2 1

1

(LE1) : MPC 5

2

R2 R2 * R1

3

R1 R1 - 1

4

MPC 1

5

MPC 5

LOAD_R1 DEC_R1 LOAD_R2 OP_ALU SEL_MICRO_SALTO MICRO_SALTO

Sim

Sim

Sim

1

LE1

5

1

1

1

5

R1*R2

Sim

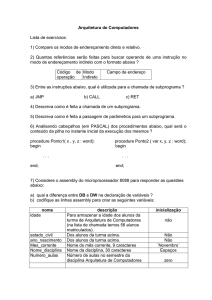

3. (2+3 valores) Suponha que a cache do PEPE (processador com 16 bits de endereço, endereçamento de byte) é

de mapeamento direto e tem uma capacidade de 64 palavras, organizadas em blocos de 8 palavras.

a) Indique o número de bits de cada um dos campos em que o endereço se divide para acesso à cache.

Etiqueta

Índice

Palavra dentro do bloco

Byte dentro da palavra

9

3

3

1

b) Suponha que a cache do PEPE tem 8 bits de etiqueta e 4 bits de índice, está inicialmente vazia e são feitos

os acessos em leitura aos endereços indicados na tabela e pela ordem com que aparecem. Para cada acesso,

indique o número da linha da cache que é usada, se foi hit (sim ou não) e qual o valor da etiqueta (em

binário) com que a linha fica após esse acesso.

Endereço acedido

32AH

564H

732H

56AH

328H

15AH

Linha da

cache

2

6

3

6

2

5

Hit

(S ou N)

N

N

N

S

S

N

Etiqueta

(em binário)

0000 0011

0000 0101

0000 0111

0000 0101

0000 0011

0000 0001

4. (4 valores) Imagine um processador com endereçamento de byte, capaz de endereçar um espaço virtual de

00000H até FFFFFH, enquanto o espaço de endereçamento físico vai de 0000H até FFFFH. As páginas têm

uma dimensão de 100H bytes. A TLB é totalmente associativa de 8 entradas. Após alguns acessos, a TLB

ficou como indicada. Preencha a tabela seguinte para este exemplo concreto.

Linha da Bit de

TLB

validade

0

1

2

3

4

5

6

7

0

1

1

1

0

0

1

0

N.º página

virtual

(hexadecimal)

C5E

3B

C5F

213

6A

A02

23

45

N.º página

física

(hexadecimal)

18

2B

6F

0E

23

2B

35

2B

Dimensão do espaço físico (em Bytes)

64K

Dimensão do espaço virtual (em Bytes)

1M

N.º páginas do espaço virtual

4K

Endereço físico que corresponde ao

endereço virtual 231AH

351AH

Endereço virtual que corresponde ao

endereço físico 0E76H

21376H

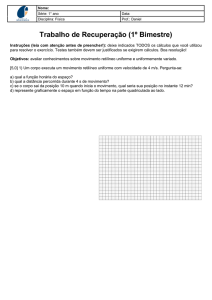

5. (2+2 valores) Considere que o PEPE é um processador com um pipeline de 4 estágios: B (Busca de Instrução),

D (Descodificação e Busca de Operandos), E (Execução da Instrução) e W (Escrita do Resultado). Os registos

entre estágios são read-after-write.

a) No programa seguinte, identifique todos os conflitos de dados, colocando um círculo à volta do registo

cujo valor depende, em conflito, de uma instrução anterior.

b) No espaço seguinte, refaça o programa, eliminando os conflitos por meio de uma solução em software.

MOV

MOV

ADD

OR

SUB

MOV

R1, 6

R2, 5

R2, R1

R1, R2

R1, 3

R1, 8

MOV

MOV

NOP

ADD

NOP

OR

NOP

SUB

MOV

R1, 6

R2, 5

R2, R1

R1, R2

R1, 3

R1, 8