Electrónica Geral

Mestrado em Eng. Biomédica

2ºSemestre, 2012/2013

Transístor metal- óxidosemicondutor: Inversor CMOS

Relatório do 2º Trabalho de Laboratório

Prof: João Costa Freire

Realizado por:

Joana Chim 69550

Mariana Costa 69939

Joana Morais 69946

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Índice

Introdução: .................................................................................................................................... 3

Introdução Teórica .................................................................................................................... 3

2. Estudo Analítico......................................................................................................................... 5

Pergunta 2.1 .............................................................................................................................. 5

Pergunta 2.2 .............................................................................................................................. 8

Pergunta 2.3 ............................................................................................................................ 10

3. Trabalho de Simulação ............................................................................................................ 13

Pergunta 3.1. ........................................................................................................................... 13

Pergunta 3.2. ........................................................................................................................... 14

Pergunta 3.3. ........................................................................................................................... 16

Pergunta 3.4. ........................................................................................................................... 18

4. Trabalho experimental ............................................................................................................ 22

Pergunta 4.1 ............................................................................................................................ 22

Pergunta 4.2. ........................................................................................................................... 23

Pergunta 4.3. ........................................................................................................................... 24

Conclusão .................................................................................................................................... 27

Considerações finais ................................................................................................................ 28

Referencias .................................................................................................................................. 29

2

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Introdução:

O intuito deste trabalho laboratorial é analisar as caracteristicas

principais que definem o funcionamento de um inversor CMOS, sendo

este formado por dois transístor complementares de esforço: NMOS e

PMOS, como indicado na figura 1.

Conforme indicado no enunciado, primeiro é efectuado um estudo

analítico em termos das grandezas caracteristicas do circuito, tendo

em conta apenas as relações teóricas clássicas iD(vGS, vDS), para cada

zona de funcionamento. Posteriormente, são verificadas por Figura 1: Circuito inversor

simulação computacional, com recurso ao software LTSpice, as

CMOS

condições de funcionamento do circuito de três formas distintas: excitação por acção de um

sinal forte (varrimento DC), por acção de uma onda sinusóidal em regime linear (AC) e por

acção de uma onda quadrada (comutação).

Por fim, é executada a parte experimental, onde são avaliadas as características reais do

circuíto e é comprovada a validade das suposições teóricas anteriores.

Introdução Teórica

Um transístor Metal Oxide Semiconductor Field-Effect Transistors (MOSFETs) é o tipo mais

comum de transístores de efeito de campo em circuitos tanto digitais como analógicos. Apesar

de ser formado por 4 terminais: Gate (Porta), Drain (Dreno), Body (Substrato) e Source (Fonte),

o substrato encontra-se, geralmente, ligado à fonte. Por esta razão, consideramos que o

MOSFET é constituido apenas por 3 terminais.

Figura 2: Estrutura e terminais de um transístor MOSFET: NMOS à esquerda e PMOS à direita

3

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Os transístores MOSFETs podem ser de dois tipos: NMOS e PMOS, devido ao isolamento entre

o terminal Gate e o substrato. Esta caracteristica leva a que a corrente iG seja nula.

Para transístor tipo N, os terminais Source e Drain assentam sobre regiões do tipo n e o Body

assenta num substrato tipo p. É criado um canal n entre a fonte e o dreno, devido ao efeito de

campo e esta característica verifica-se a partir do momento em que a tensão VGS ultrapassa a

tensão Vt.

Para o tipo P, este canal está assente num poço de substrato tipo n. Como o canal p e o

substrato n estão inversamente polarizados, não há passagem significativa de corrente entre

estas duas regiões, logo pode-se considerar que os dois transístores ficam isolados. Assim, a

corrente que sai do canal p é muito mais baixa do que a corrente do canal n. Para compensar

esta diminuição, o primeiro é ligeiramente maior que o n.

Como consequência, os transístores NMOS (tabela 1) e PMOS (tabela 2) podem operar em três

zonas de funcionamento distintas:

Corte

Tríodo

Saturação

Tabela 1: características do NMOS nas diferentes zonas de funcionamento

Corte

Tríodo

Saturação

Tabela 2: características do PMOS nas diferentes zonas de funcionamento

Para a análise em regime dinâmico (AC) recorremos ao esquema incremental do MOSFET

(modelo π Híbrido). Para o circuito desta actividade laboratorial consideramos r0 =

.

4

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Figura 3: Esquema incremental do NMOS à direita e do PMOS à

esquerda

Para a realização do trabalho experimental utilizámos os seguintes valores para os diversos

componentes:

VTon

-VTOp

VDD

VSS

1.6V

1.8V

9V

0V

Tabela 3: Valores das tensões usadas no circuito do trabalho laboratorial

2. Estudo Analítico

Pergunta 2.1

De forma a calcular os pontos onde há alteração do funcionamento de cada um dos

transístores e a traçar a característica de transferência, vo(vi), do circuito integrado monolítico

HEF4007, utilizam-se os dados fornecidos pelo protocolo experimental:

NMOS

PMOS

.MODEL N4007 NMOS (TOX=70N; KP=73u; .MODEL P4007 PMOS (TOX=70N; KP=16u;

VTO=1,6V;

ϒ=2.0;

CBD=0.2p;

MJ=0.75; L=5u; W=100u; λ=20m)

CBS=0.2p; VTO=-1,8V; ϒ =1.0; CBD=0.2p; CBS=0.2p;

MJ=0.75; L=5u; W=300u; λ=20m)

Tabela 4: especificações gerais dos modelos dos transístores do circuito integrado HEF 4007

[2.01]

[2.02]

Para o estudo da característica de transferência vo(vi), temos de ter em conta que devido à

geometria do circuito existem, no conjunto dos dois transístores,cinco zonas possíveis de

funciomento:

5

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

1ª Zona: NMOS cortado e

Como NMOS está cortado,

Como

e

,e

, então PMOS está em tríodo:

PMOS tríodo

Sendo

, então:

Estando NMOS em saturação:

Considerando PMOS em tríodo:

2ª Zona: NMOS saturação e

PMOS tríodo

Como as correntes de PMOS e NMOS são iguais, então:

Recorrendo às equações das zonas 1 e 3, obtemos os limites inferior e

superior de VI, respectivamente:

Nesta região, há que ter em conta que a característica tem declive

infinito, pois VI=constante.

3ª Zona: NMOS saturação e

PMOS saturação

Para NMOS em saturação:

Para PMOS em saturação:

Como

Pelos limites da região:

Para NMOS em tríodo:

PMOS em saturação:

4ª Zona: NMOS tríodo e PMOS

saturação

6

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Como

Recorrendo às equações das zonas 3 e 5, obtemos os limites inferior e

superior de VI, respectivamente:

Como

, então PMOS está cortado

e

5ª Zona: NMOS tríodo e PMOS

OFF

Sendo

Tabela 5: características das diferentes zonas de funcionamentos do inversor CMOS

Recorrendo ao programa Wolfram Mathematica e usando as equações das diferentes zonas da

tabela anterior, obtemos a seguinte característica de transferência.

Gráfico 1: Característica de transferência do circuito, obtida pela análise teórica

Em que :

Ponto A (1.6;9): limite direito da 1ª zona;

Ponto B (4.11;5.91): intersecção entre a 2ª e a 3ª zona;

Ponto C (4.11; 2.91): intersecção entre a 3ª e a 4ª zona;

7

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Ponto D (7.2;0): limite esquerdo da 5ª zona.

Figura 4: Característica de transferência esperada do circuito para uma tensão VDD=5V(à esquerda) e para uma

tensão VDD=10V(à direita)

A característica de transferência obtida no gráfico 1 (VDD=9V) está de acordo com o esperado

teoricamente. Também o podemos verificar comparando o gráfico obtido com os fornecidos

pelo fabricante(figura 4), já que a curva obtida está entre as duas situações acima

apresentadas.

A partir da comparação dos dois gráficos, retiramos que o gráfico obtido teoricamente é muito

próximo do que representa o real funcionamento do circuito em causa.

Pergunta 2.2

Nesta etapa pretendemos obter uma estimativa do ganho de tensão a meio da zona em que o

inversor pode trabalhar como amplificador, recorrendo a uma análise incremental em AC. Para

tal, subtituímos o circuito pelo seu modelo incremental equivalente, em que λ=0.02V-1.Assim, a

corrente no dreno depende da tensão entre o dreno e a fonte iD, quando o transístor está em

saturação.

Figura 5: Esquema incremental do circuito

8

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

[2.03]

[2.04]

[2.05]

Pela Lei de Ohm:

[2.06]

Como vgs=vi, então:

[2.07]

A zona onde o inversor opera como amplificador é a 3ª zona descrita na pergunta anterior,

onde os dois transístores estão em saturação. Assim, consideram-se os valores médios da zona

de característica de transferência desta zona:

Pela análise do circuito da figura 4:

Subtituindo as tensões obtidas nas equações 2.03-2.07:

9

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Assim,

Pela comparação da figura ao lado com os cálculos anteriores,

podemos verificar que estes não estão concordantes, pois

segundo a figura 6, para um VDD=9 obtém-se um ganho de

tensão

. Tal facto pode ser justificado tanto por os

modelos usados pelo fabricante serem diferentes do software e

da análise teórica, bem como o facto de que quanto menor a

tensão de alimentação, maior a discrepância obtida entre os

valores. Assim, pode ser desprezada esta diferença.

Figura 6: Curva do ganho de tensão do CMOS para

um VDD de 0 a 15V, fornecida pelo fabricante

Pergunta 2.3

Neste ponto, pretende-se obter graficamente, a partir da caracterítica

calculada na

pergunta 2.1, uma estimativa das margens de ruído do inversor, que são limitadas pelos

pontos da característica de transferência

:

e

. Para a análise, vamos

considerar que os transístores PMOS e NMOS estão nas regiões 2 ou 4, descritas

anteriormente.

Para além disso, e atendendo ao indicado no protocolo, vamos considerar

que mantém a saída no nível lógico 1 (

)e

o limite superior

o limite inferior que leva à saída

ao nível

lógico 0. Também iremos desprezar o efeito de λ (λ=0).

Para confirmar a validade da resolução gráfica, iremos, numa primeira instância, resolver

analiticamente esta pergunta:

Para o limite inferior da margem de ruído superior

, tem-se que o NMOS se

encontra em tríodo e o PMOS em saturação, logo pelas equações da região 4:

10

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Derivando ambos os membros em ordem a

, e utilizando

Para o limite superior da margem de ruído inferior

e

:

, tem-se que o NMOS se

encontra na zona de saturação e o PMOS em tríodo, logo pelas equações da região 2:

Derivando ambos os membros em ordem a

, e utilizando

e

:

Recorrendo ao programa Mathematica para resolver o sistema de equações:

Figura 7: Característica de transferência do circuíto inversor CMOS com margens de ruído assinaladas

11

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Como podemos observar, os valores calculados estão de acordo com o gráfico da Figura 8. E

como seria de esperar, as margens de ruido não apresentam o mesmo valor, que se deve ao

facto dos transístores não serem simétricos.

12

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

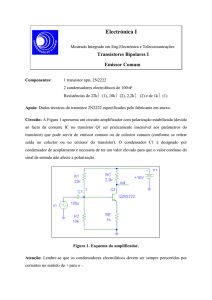

3. Trabalho de Simulação

Para o trabalho de simulação deste trabalho de laboratório, recorreu-se ao programa CAD

LTspice. Neste, tendo como base o circuito fornecido pelo procedimento, foram criados vários

circuitos portadores de alterações necessárias para a obtenção de gráficos e valores pedidos

em cada questão. Para este circuito utilizou-se um dos pares de transístores complementares,

NMOS e PMOS, existentes no circuito integrado (CI) monolítico HEF4007, para os quais foi

também preciso alterar algumas das suas características, nomeadamente as tensões VT.

A simulação serve para verificar resultados teóricos, e ainda para analisar o circuito a

alterações que lhe são impostas. No geral, obteve-se pontos de funcionamento em repouso,

ganhos de tensão através de respostas em frequência, tempos de subida e descida dos sinais e

ainda atrasos entre tensões de entrada e de saída. Como tal, para esta diversidade de

resultados é necessária uma análise com diferentes características, ou seja, recorrer a

diferentes funcionalidades do programa, nomeadamente de simulação, como DC Sweep, AC

analysis e Transient.

Pergunta 3.1.

Para o estudo do funcionamento DC do circuito da figura 8, selecionou-se o modo DC Sweep.

Este modo permite obter a tensão de saída, Vo, em função de um varrimento que é feito à

tensão de entrada, Vi, desde o valor 0 até à tensão de alimentação do transístor PMos, VDD.

Tendo-se obtido o gráfico da característica vo(vi), gráfico 2.

Figura 8: Circuito utilizado para análise em modo DC

13

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Gráfico 2: Característica vo(vi) para o funcionamento DC

Pergunta 3.2.

Utilizando o circuito da figura 5, analisou-se também a curva representativa da derivada da

tensão de saída, gráfico 3 e 4, adicionando ao gráfico anterior a derivada do sinal de saída. Em

ambos os gráficos é possível observar a existência de um patamar onde o ganho de tensão é

máximo, ou seja, há vários valores de

valor de ganho máximo obtido foi

para os quais a tensão de saída é mais elevada. O

para uma tensão

, valor que se encontra concordante com a análise teórica do circuito (

).

14

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Gráfico 3: Gráfico que relaciona a tensão de saída com a sua derivada

Gráfico 4: Ampliação do gráfico 3 na zona de ganho máximo

Nas condições para as quais VO é máximo, procedeu-se à análise do ponto de funcionamento

em repouso de ambos os transístores. Para isso procedeu-se à simulação no modo DC

Operating point do funcionamento do circuito da figura 9, no qual se substituiu o valor da

tensão de entrada para

, tendo-se obtido os seguintes resultados para as tensões

e correntes, figura 10.

15

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Figura 9: Circuito com fonte de tensão de entrada em modo DC (VI=4.086 V)

Figura 10: Ponto de Funcionamento em Repouso para VI=4.086V

No ponto de funcionamento em repouso, para transítores Mos, considera-se o seu

funcionamento na zona de saturação. Neste caso, observa-se que para uma tensão de entrada

muito semelhante

dos limites previstos,

(

), a tensão de saída encontra-se dentro

(

).

Pergunta 3.3.

Tendo em consideração o valor de ganho máximo em modo DC, analisou-se o ganho do

circuito para sinais fracos em função da frequência. Nomeadamente foi necessário alterar o

funcionamento do circuito para o modo AC, através da opção de simulação AC analysis (Type

of Sweep: Octave; Number of points: 1000; Start frequency: 1 e Stop Frquency: 10Meg), para

uma tensão de entrada com amplitude igual a 1V. Para além disso, foram adicionados ao

circuito da figura 9, 2 condensadores e uma resistência, com cargas capacitivas de 11pF e

16

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

100pF e resistiva de 1MΩ. Sendo que a adição dos componentes, condensador de maior

capacidade e resistência, pretendem ilustrar o efeito capacitivo e resistivo imposto pelos

instrumentos utilizados em laboratório, como os cabos axiais e o próprio osciloscópio.

Figura 11: Circuito obtido por adicionar os condensadores Cf e Cc e a resistência Rf.

Como já foi referido, esta simulação permitiu obter a resposta em frequência deste circuito

inversor, gráfico 5. É de salientar a inexistência de frequência de corte explicada pela ausência

de condensadores no circuito. O mesmo não se verifica para frequências elevadas, onde é

sentida a influência dos efeitos capacitivos dos componentes introduzidos.

Gráfico 5: Gráfico obtido pela razão entre a tensão de saída e a de entrada

O ganho de tensão, Av é obtido através da razão entre a tensão de saída e a de entrada. Como

se arbitrou a tensão de entrada para 1V, neste caso o ganho vai corresponder à tensão de

17

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

saída,

, valor concordante com o obtido na

alínea anterior.

Para descobrir o limite superior da banda de frequências, ou seja, a frequência a partir da qual

o ganho começa a diminuir significativamente (pólo da função de transferência), subtraiu-se

ao valor do ganho máximo 3 dB,

então uma frequência,

, a que corresponde

.

Pergunta 3.4.

Para o estudo dos tempos de subida e descida e os atrasos dos sinais das tensões de entrada e

saída, foi necessário fornecer ao circuito um sinal de forma trapezoidal. Esta onda é vista com

um Pulse, com uma amplitude correspondente a VDD (neste caso, de 0 a 9V) e é caracterizada

pelos seguintes parâmetros, Tdelay: 0s, Trise e Tfall: 1ns, Ton: 0.5µs e Tperiod: 1µs. O

funcionamento do circuito foi simulado através do modo Transient, que permite analisar a

resposta do circuito em função do tempo.

Figura 12: Circuito com os condensadores e resistência e uma tensão de entrada de forma trapezoidal

18

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Gráfico 6: Curvas para as tensões de entrada e saída em função do tempo

Gráfico 7: Curva ampliada para a subida de VO e descida de VI

19

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Gráfico 8: Curva ampliada para a subida de VI e descida de VO

No primeiro gráfico, estão representados os sinais de saída e de entrada, sendo possível

observá-las na totalidade, ilustrando a forma mais rectangular de VI e ligeiramente mais

arredondada de VO. Os gráficos F e G, ampliações do gráfico E, permitem o cálculo do tempo

que as curvas de tensão demoram a atingir quer o máximo, quer o mínimo dos seus valores.

Para ambas as ondas analisaram-se estas variações em apenas 80% do seu percurso, isto é, a

diferença de tempos foi calculada tendo em conta os valores de tensão para 10% e 90%, tal

como representado na tabela 6 e de acordo com o anexo [1].

Catálogo

(80%)

Tempo de subida

10%

90%

Vo

504.95

551.81

46.86

Vi

999.9

1000.7

0.8

Tempo de descida

10%

90%

Vo

1003

1031.7

28.7

Vi

501.08

501.92

0.84

Atraso

50% (Vo)

50% (Vi)

502.11

501.5

18.61

27.62

1012.8

1000.6

12.2

27.62

44.5

44.5

Tabela 6 Tempos de subida, descida e atraso para Vo e Vi

No caso do sinal de entrada, VI , dado que foram selecionados os parâmetros, sabe-se à priori

que para um funcionamento ideal, numa análise de 80% do sinal,

e

deveriam ser iguais

a 0.8µs, o que é possível comprovar pela tabela. Em relação ao sinal de saída foi necessário

comparar com as equações fornecidas pelo anexo, para as transições do sinal de saída utilizou20

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

se

e para os atrasos entre o sinal de saída e o de entrada,

Sendo que se utilizaram as equações para uma tensão VDD de

10V, mais próximo dos 9V, e como condensador de saída,

. Através da análise destas equações e dos valores obtidos em simulação, observaramse algumas diferenças, que se podem dever aos componentes utilizados pelo próprio software

e às aproximações das equações.

21

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

4. Trabalho experimental

Neste trabalho experimental foi testado o funcionamento de um protótipo de um circuito

integrado (CI) monolítico HEF4007 (com um circuito inversor CMOS), como indicado na figura

13 Dos instrumentos utilizados para análise constam um osciloscópio digital (modelo DSO-X2024 da Agilent), um gerador de funções (Centrad GF 467F), e ainda um multímetro e um

gerador de sinais (utilizado para alimentação DC).

Figura 13: Base de montagem TEE03

[2]

Pergunta 4.1

Para traçar a característica de transferência vO(vI) do circuito utilizado no laboratório, foi

necessário aplicar-lhe um sinal sinusoidal de frequência 100Hz com uma amplitude

correspondente a

. Sendo que a este se somou uma componente de tensão de

desvio (offset), para que a tensão de entrada, vI, pudesse então variar de 0V a 9V. Quanto às

tensões de alimentação DC, VSS foi utilizado como a referência e VDD com 9V. De modo a que se

pudesse observar esta característica, figura 14, recorreu-se ao modo XY do osciloscópio, em

que a entrada relativa a vI é aplicada na deflexão horizontal e a entrada de vO na deflexão

vertical.

22

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Figura 14: Característica de transferência vo(vi)

Nesta figura, tanto as escalas horizontal como vertical apresentam 2V/div, permitindo verificar

que quando vI é zero vO atinge os 9V, e vice-versa. Para além disso, observa-se também uma

mudança de concavidade para

aproximadamente nos 4.5V, como era de esperar.

Pergunta 4.2.

De seguida, alterou-se o gerador vI para uma onda quadrada com uma frequência de

aproximadamente 1MHz (período do sinal 1µs), ajustando o nível dos impulsos de forma a

serem iguais às tensões de alimentação DC, ou seja, VIH= VDD=9V e VIL= VSS= 0V. Obteve-se

então os sinais de entrada e saída em função do tempo, figura 15.

Figura 15 Sinais de entrada (canal 1) e saída (canal 2) (escalas com 5V/div)

A partir do gráfico da figura 15 e das funcionalidades do osciloscópio foi possível obter os

tempos de subida e descida (para as variações de 10% e 90% do sinal) e ainda os tempos de

23

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

atraso de propagação entre ambos sinais (para as variações a 50%), como indicado na tabela 7

e na figura 16. É ainda importante salientar que os tempos de subida e descida a ter em conta

para as conclusões foram obtidos através da subtracção entre o tempo correspondente ao

sinal de saída e o de entrada, uma vez que é necessário ter em conta que o sinal de entrada

fornecido ao circuito não é instantâneo, ou seja, o gerador não é suficientemente rápido para

gerar sinais ideais.

Tempo de subida

Experimental

Vo

60

Vi

28

Tempo de descida

Experimental

Vo

66

Vi

26

Atraso

Experimental

32

40

58

41

Tabela 7: Tempos de subida, descida e atraso dos sinais de entrada e saída

Figura 16 Sinais de entrada (canal 1) e saída (canal 2) (escalas com 5V/div) para os cálculos dos atrasos

Pergunta 4.3.

Para ter noção das dispersões de fabrico dos transístores, calculou-se os valores de Kn e Kp e

VTn e VTp para os circuitos na figura17.

24

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Figura 17: Montagens utilizadas no cálculo dos parâmetros dos transístores

Recorrendo a um multímetro em modo DC, medimos as resistências R1 e R2 bem como as

tensões aos terminais das mesmas (V1 e V2). Obteve-se os resultados apresentados na tabela8.

T1(NMOS)

T2(PMOS)

R1=101,3 kΩ

V1 =8,5 V

V1=7,8 V

R2=2,178 kΩ

V2=5,5 V

V2=4v

Tabela 8: Valores das resistencias e das tensões aos seus terminais obtidos experimenttalmente

Como vGD=0V ambos os transísteores encontram-se em saturação.

Resolvendo os seguintes sistemas de equações obtivemos os valores reais de ID, K e Vtpara

cada um dos transístores (resumidos na tabela 9):

Para transístor 1

Escolhendo

, pois se encontra em saturação:

Para transístor 2

25

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Grandeza

ID(mA)

Vt(V)

K(mA/V2)

T1 (NMOS)

2,525

0,96254

0,3922

T2(PMOS)

----------------

Tabela 9: Valores das grandezas ID Vt e K para cada transístor

Sendo que o transístor está em saturação, seria suposto obter um valor de Vt <0. No entanto

tal não se verificou em ambiente laboratorial. Deste modo os valores calculados para o

transístor PMOS não são viáveis.

26

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Conclusão

Este trabalho experimental tinha como objectivo a análise e simulação do funcionamento de

um circuito CMOS inversor e amplificador.

Relativamente às curvas de transferência vO(vI), observou-se que nos 3 casos, se encontram

bem delineadas as diferentes zonas de funcionamento do transístor (corte, saturação, tríodo),

e semelhantes entre si, demonstrando então um funcionamento similar. Do mesmo modo, o

ganho obtido para as 3 análises do circuito é aproximadamente igual

. No entanto, estes resultados não são concordantes com os fornecidos pelo anexo

do fabricante, provavelmente devido ao uso de um método de análise diferente e ainda a

aproximações analíticas aquando da utilização do modelo π-híbrido.

Tempo de subida

Simulação

Experimental

Vo

46.86

60

Vi

Tempo de descida

0.8

28

Simulação

Experimental

Vo

28.7

66

Vi

0.84

26

Atraso

Simulação

Experimental

18.61

58

12.2

41

Catálogo

(80%)

32

44.5

40

44.5

27.62

Tabela 10: Valores de simulação, experimentais e do catálogo para os tempos de subida, descida e atraso

No que diz respeito aos tempos de subida e descida das tensões de entrada e saída, tal como

se verifica pela tabela 8, existe uma grande diferença entre os vários valores. Nomeadamente

verifica-se que a nível experimental, tLH (tempo de subida) é superior a tHL (tempo de descida),

ao contrário do que indicado na simulação. Para se poder avaliar os tempos fornecidos pela

simulação foi necessário recorrer a fórmulas de extrapolação fornecidas no catálogo, de modo

a adequar os valores do fabricante ao condensador que efectivamente foi utilizado. Apesar

desta aproximação, constatou-se que apenas tLH é parecido com o valor fornecido.

O tempo de atraso é um parâmetro importante na caracterização de circuitos integrados ao

nível digital, e é preferencial que apresente valores baixos (inferior a 10 ns), no entanto

verifica-se que apenas a simulação se encontra perto destes valores.

27

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Estas variações nos resultados podem, mais uma vez, ser explicadas pela utilização de modelos

que não se adequam à realidade e por erros intrínsecos à montagem do circuito em estudo. É

ainda importante salientar as componentes internas dos componentes, como os cabos

coaxiais, o osciloscópio, o condensador e a resistência, que têm grande influência nos

resultados experimentais.

No trabalho experimental, aquando da análise da dispersão de fabrico dos componentes

electrónicos observou-se que estes efeitos existem e não podem ser desprezados, na medida

em que os valores de K e VT calculados são inferiores aos considerados na teoria, para o

transístor NMOS. No que toca ao transístor PMOS não podemos tirar conclusões, como já foi

referido. Tal pode dever-se a erros de medição ou ao comportamento dos componentes ser

diferente do esperado.

Considerações finais

A realização deste trabalho experimental permitiu aprofundar conhecimentos sobre os

transístores MOSFET’s (transístores de metal-óxido semicondutor de efeito de campo), de tipo

NMOS e PMOS. Nomeadamente o funcionamento de circuitos CMOS como inversores e

amplificadores, comprovado pelo ganho elevado e de valor negativo.

Mais uma vez constatou-se que os circuitos reais apresentam variações em relação às análises

teóricas e de simulação, devido às características dos materiais e aproximações do software

utilizado.

28

Trabalho Laboratorial 2: Transístor Metal-Óxido Semicondutor- Inversor CMOS

Referencias

[1]

Integrated circuits, HEF4007UB Data Sheet, January 1995

[2]

FREIRE, João Costa; Electrónica Geral - 2.º Trabalho de Laboratório – Transístores Metal-

Óxido-Semicondutor Inversor CMOS; 2.º Semestre 2012/13; IST-DEEC; Lisboa; 2013.

SEDRA, Adel S. e SMITH, Kenneth C., Microelectronic Circuits; 5ª ed.; Oxford; Oxford University

Press; 2004.

29