UNIVERSIDADE FEDERAL DO PARANÁ

JOÃO LUIZ GLOVACKI GRANEMAN DE MELO

PROJETO E IMPLEMENTAÇÃO DE UM FILTRO ATIVO PARALELO

MONOFÁSICO PARA CORREÇÃO DE DISTORÇÃO HARMÔNICA

DE CORRENTE

CURITIBA

2013

JOÃO LUIZ GLOVACKI GRANEMAN DE MELO

PROJETO E IMPLEMENTAÇÃO DE UM FILTRO ATIVO PARALELO

MONOFÁSICO PARA CORREÇÃO DE DISTORÇÃO HARMÔNICA

DE CORRENTE

Trabalho de Conclusão de Curso apresentado

à disciplina Projeto de Graduação, como

requisito parcial à conclusão do curso de

Engenharia Elétrica, Setor de Tecnologia,

Universidade Federal do Paraná

Orientador: Prof. Dr. João Américo Vilela

Júnior

CURITIBA

2013

JOÃO LUIZ GLOVACKI GRANEMAN DE MELO

Título: PROJETO E IMPLEMENTAÇÃO DE UM FILTRO ATIVO PARALELO

MONOFÁSICO PARA CORREÇÃO DE DISTORÇÃO HARMÔNICA DE CORRENTE

Trabalho de Conclusão de Curso apresentado como exigência parcial para obtenção do

grau de Engenheiro Eletricista com ênfase em Telecomunicações/Eletrônica, à Universidade

Federal do Paraná.

Data: 11 de dezembro de 2013

Prof. Dr. João Américo Vilela Junior

Orientador

Departamento de Engenharia Elétrica, UFPR

Prof. Dr. Ivan Eidt Colling

Departamento de Engenharia Elétrica, UFPR

Prof. Dr. Rogers Demonti

Departamento de Engenharia Elétrica, UFPR

Dedico este trabalho aos meus pais

Luis e Doralice, minhas referências, por toda a

educação e apoio que me dedicaram.

Sem eles, não teria conseguido

chegar até aqui.

“Se faltam máquinas, você pode

comprá-las. Se não há dinheiro, você toma

emprestado. Mas homens você não pode comprar,

nem pedir emprestado. E homens motivados por

uma ideia são a base do êxito."

— Eggon João da Silva

AGRADECIMENTOS

A Deus, pelo dom da vida.

Ao Prof. João Américo pela oportunidade concedida, orientação, apoio e incentivo,

além de todos os ensinamentos transmitidos que foram de grande valia para a conclusão desse

trabalho.

Aos colegas de faculdade: André “Pernambuco”, Daniel Ussuna, Douglas Prost,

Eugênio Heiss, Gilson Eggert, Ivanderson de Oliveira e Tiago Vinícius, pelo apoio, pelas

inúmeras horas de estudo e pelos momentos de lazer e descontração. E a todos os demais

colegas que de alguma forma contribuíram para que eu chegasse aqui hoje.

Aos colegas de estágio, SE Acesso GVT, R&D da Siemens Enterprise e R&D da

Landis Gyr, que sem sobra de dúvida foram fundamentais para meu crescimento e

desenvolvimento tanto pessoal quanto profissional.

Por fim agradeço à minha família e a minha namorada Viviane por todo o apoio,

compreensão e paciência.

vi

RESUMO

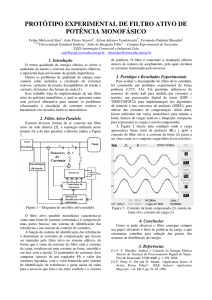

Este Trabalho de Conclusão de Curso apresenta o projeto e implementação um Filtro

Ativo Paralelo (FAP), controlado de forma digital com vistas à redução do conteúdo

harmônico de cargas não lineares advindas da rede elétrica com potência aparente de até

1kVA. O FAP funciona como uma fonte de corrente controlada, injetando/drenando corrente

no ponto onde está conectado, de forma que a corrente drenada da fonte pelo FAP mais a da

carga seja idealmente senoidal.

Primeiramente é realizado um breve estudo sobre as cargas não lineares e filtros

ativos, e as suas influências na qualidade da energia da rede. Em seguida será apresentada a

estrutura do FAP com sua modelagem matemática, a técnica de controle e modulação

utilizada.

Posteriormente são descritas as etapas da construção física do protótipo, apresentando

os cálculos para dimensionamento da carga não linear, banco de capacitores, indutores, placas

auxiliares e os sensores.

Na sequência será apresentado o desenvolvimento do controle digital e do firmware

implementado posteriormente no microcontrolador. Por último são mostrados os resultados

obtidos nos testes funcionais do protótipo.

vii

ABSTRACT

This work of course completion presents the design and implementation of one

Parallel Active Filter (FAP), digitally controlled in order to reduce the harmonic content of

nonlinear loads arising from the power grid with up to 1 kVA. The FAP serves as a current

source controlled by injecting/draining stream at the point where it is connected, so that the

current drawn from the source by the load plus the FAP is ideally sinusoidal.

First a brief study of non-linear loads and active filters, and their influences on the

quality of the power grid is performed. In the sequence will be presented the structure of FAP

with its mathematical modeling, technical control and modulation used.

Later stages of the physical construction of the prototype are described, presenting

calculations for sizing the nonlinear load, capacitors, inductors, sensors, and accessory cards.

In the sequence will be presented in the development of digital control firmware

implementation on a microcontroller. Finally the results obtained are shown in the functional

tests of the prototype.

viii

SUMÁRIO

RESUMO.................................................................................................................................. vi

ABSTRACT ............................................................................................................................ vii

LISTA DE FIGURAS.............................................................................................................. xi

LISTA DE TABELAS ........................................................................................................... xiv

LISTA DE SIGLAS ................................................................................................................ xv

LISTA DE SÍMBOLOS ........................................................................................................ xvi

1.

INTRODUÇÃO ................................................................................................................. 1

2. CARGAS NÃO LINEARES, FILTROS ATIVOS E A QUALIDADE DA ENERGIA

ELÉTRICA ............................................................................................................................... 5

2.1

A Qualidade da Energia Elétrica ............................................................................. 5

2.1.1

3.

Harmônicos ........................................................................................................... 6

2.2

As Cargas não Lineares ............................................................................................. 7

2.3

Filtros Ativos .............................................................................................................. 8

2.3.1

Classificação dos Filtros Ativos ........................................................................... 9

2.3.2

Filtro Ativo Paralelo ........................................................................................... 10

ESTRUTURA DO FAP, MODULAÇÃO E ESTRATÉGIAS DE CONTROLE ...... 12

3.1

Estrutura do Filtro Ativo Paralelo ......................................................................... 12

3.2

Modulação a Três Níveis ......................................................................................... 13

3.3

Estratégia de Controle ............................................................................................. 14

3.3.1

Modelagem do Inversor ...................................................................................... 16

3.3.2

Malha de Corrente .............................................................................................. 16

3.3.3

Malha de Tensão ................................................................................................. 17

ix

4.

5.

7.

PROJETO DOS ELEMENTOS PASSIVOS DO FAP ................................................ 20

4.1

Especificação do FAP .............................................................................................. 20

4.2

Projeto ....................................................................................................................... 21

4.2.1

Projeto da Carga ................................................................................................. 21

4.2.2

Indutor do FAP ................................................................................................... 22

4.2.3

Banco de Capacitores do FAP ............................................................................ 27

PROJETO DOS ELEMENTOS DE CONTROLE DIGITAL .................................... 29

5.1

FTMA de Corrente .................................................................................................. 30

5.2

Projeto do Compensador de Corrente Digital ...................................................... 31

5.3

Projeto do Compensador de Tensão Digital .......................................................... 35

COMPONENTES E CIRCUITOS AUXILIARES ...................................................... 41

7.1

FRDM-KL25Z ARM Cortex M0+ ......................................................................... 42

7.2

Sensor de Corrente ACS712 ................................................................................... 43

7.3

Senoide de Referência .............................................................................................. 44

7.4

MOSFET IRFP460 .................................................................................................. 45

7.5

Driver IR2104 ........................................................................................................... 45

7.6

Indutor

7.7

Banco de Capacitores FAP (

7.8

Banco de Capacitores da Carga

7.9

Circuito de Partida Suave (InRush) ....................................................................... 50

. ................................................................................................................ 46

.............................................................................. 49

.................................................................... 49

7.10 Fonte Auxiliar .......................................................................................................... 51

7.11 Buffer......................................................................................................................... 53

7.12 Filtro Anti-Aliasign .................................................................................................. 54

x

8.

9.

RESULTADOS OBTIDOS ............................................................................................ 55

8.1

Montagem do Protótipo........................................................................................... 55

8.2

Simulação do FTMF da Corrente e Tensão .......................................................... 60

8.3

Implementação do Protótipo................................................................................... 62

8.3.1

Nova Malha de Corrente..................................................................................... 63

8.3.2

Nova Malha de Tensão ....................................................................................... 66

CONCLUSÕES E PERSPECTIVAS ............................................................................ 69

REFERÊNCIAS ..................................................................................................................... 71

APÊNDICE A - Script MatLab Malha de Corrente............................................................ 76

APÊNDICE B - Script MatLab Malha de Tensão ............................................................... 77

APÊNDICE C – Firmware Controle Digital PSIM ............................................................. 78

APÊNDICE D – Diagrama Esquemático Entrada_127AC ................................................ 80

APÊNDICE E – Diagrama Esquemático RC_Load ............................................................ 81

APÊNDICE F – Diagrama Esquemático DC_Power_Supply ............................................ 82

APÊNDICE G – Diagrama Esquemático Controle ............................................................. 83

APÊNDICE H – Diagrama Esquemático Senoide Referência e Sensor de Corrente ...... 84

APÊNDICE I – Diagrama Esquemático Inversor ............................................................... 85

APÊNDICE J – ProcessorExpert.c ....................................................................................... 86

APÊNDICE K – Events.c ....................................................................................................... 89

APÊNDICE L – Tabela dos Custos dos Materiais do Protótipo ........................................ 90

xi

LISTA DE FIGURAS

Figura 1.1 – Forma de onda da corrente drenada pelo retificador com filtro capacitivo [4]...... 2

Figura 1.2 - Inversor de tensão (VSI). ........................................................................................ 3

Figura 1.3 - Inversor de corrente (CSI). ..................................................................................... 3

Figura 1.4 – Filtro ativo monofásico conectado paralelamente à rede e a carga não linear [4]. 4

Figura 2.1 – Retificador monofásico com filtro capacitivo. ....................................................... 7

Figura 2.2 – Tensão e corrente drenada da rede. ........................................................................ 8

Figura 2.3 - Filtro ativo série. ..................................................................................................... 9

Figura 2.4 – Filtro ativo paralelo. ............................................................................................... 9

Figura 2.5 – Princípio de funcionamento de um FAP. ............................................................. 10

Figura 2.6 - Corrente da rede, da carga e do FAP. ................................................................... 11

Figura 3.1 – Inversor de tensão em ponte completa (VSI-FB) [4]. .......................................... 13

Figura 3.2 – Modulação senoidal três níveis. ........................................................................... 14

Figura 3.3 – Monitoramento da corrente de rede. .................................................................... 15

Figura 3.4 – Diagrama de blocos da estrutura de controle. ...................................................... 15

Figura 3.5 – Estrutura de controle da malha de corrente. ......................................................... 16

Figura 3.6 – Diagrama de blocos para o controle da corrente do FAP..................................... 17

Figura 3.7 - Estrutura de controle da malha de tensão. ............................................................ 18

Figura 3.8 - Diagrama de blocos para o controle do FAP. ....................................................... 19

Figura 4.1 - Retificador monofásico de onda completa com filtro capacitivo. ........................ 21

Figura 4.2 - Tensão nos terminais ab do FAP. ......................................................................... 23

Figura 4.3 - Terminais a e b do Inversor de tensão em ponte completa [4]. ............................ 23

Figura 4.4 - Ondulação de corrente parametrizada [4]. ............................................................ 26

Figura 5.1 – FTMA da malha de corrente. ............................................................................... 30

Figura 5.2 – Diagrama de Bode do inversor e do filtro anti-aliasign. ..................................... 32

Figura 5.3 - Inserção dos ganhos da FTMA de corrente. ......................................................... 33

xii

Figura 5.4 – Ganho do compensador. ....................................................................................... 34

Figura 5.5 – Diagrama de Bode da FTMF de corrente. ............................................................ 34

Figura 5.6 – Gráfico do LR da FTMF de corrente do FAP com controle digital. .................... 35

Figura 5.7 - FTMA da malha de tensão. ................................................................................... 36

Figura 5.8 - Diagrama de Bode da FTMA de tensão................................................................ 37

Figura 5.9 – Ganhos associados a

. ................................................................ 37

Figura 5.10 – Inserção dos ganhos da FTMA de tensão. ......................................................... 39

Figura 5.11 – Ganho do compensador. ..................................................................................... 39

Figura 5.12 - Diagrama de Bode da FTMF de tensão. ............................................................. 40

Figura 5.13 - Gráfico do LR da FTMF de tensão do FAP com controle digital. ..................... 40

Figura 7.1 – Diagrama de blocos do protótipo do FAP. ........................................................... 41

Figura 7.2 - FRDM-KL25Z ARM Cortex M0+ [17]. .............................................................. 42

Figura 7.3 – Esquema de ligação do sensor de corrente ACS712 [20]. ................................... 43

Figura 7.4 – Circuito gerador da senoide de referência. .......................................................... 44

Figura 7.5 – Senoide de referência. ......................................................................................... 44

Figura 7.6 - Esquema de ligação do driver IR2104 [22]. ......................................................... 46

Figura 7.7 – Núcleo e carretel do tipo E [23]. .......................................................................... 46

Figura 7.8 – Banco de capacitores 600µF/420V. ..................................................................... 49

Figura 7.9 - Banco de capacitores 1500µF/200V. .................................................................... 49

Figura 7.10 – Circuito para acionamento do relé. .................................................................... 51

Figura 7.11 – Esquemático fontes auxiliares. ........................................................................... 52

Figura 7.12 –Buffer com AmpOp. ............................................................................................ 53

Figura 7.13 – Filtro anti-aliasign. ............................................................................................ 54

Figura 8.1 – Interruptor diferencial residual. ............................................................................ 55

Figura 8.2 – PCB da entrada AC com circuito de inrush. ........................................................ 56

Figura 8.3 – Fonte Auxiliar (Power Supply). ........................................................................... 56

Figura 8.4 – PCB controle. ....................................................................................................... 57

xiii

Figura 8.5 – PCB inversor. ....................................................................................................... 58

Figura 8.6 – Dimensionamento das trilhas de potência. ........................................................... 59

Figura 8.7 – Montagem final do protótipo do FAP. ................................................................. 59

Figura 8.8 – Simulação da malha de corrente e tensão do FAP controlado digitalmente. ....... 60

Figura 8.9 – Emulador do microcontrolador e PWM do PSIM................................................ 61

Figura 8.10 – Tensão da rede com a corrente de carga e a corrente gerada pelo FAP. ............ 61

Figura 8.11 – Tensão no banco de capacitores do FAP............................................................ 62

Figura 8.12 – Beans Processor Expert. .................................................................................... 62

Figura 8.13 – Setup para teste da malha de corrente. ............................................................... 64

Figura 8.14 – Corrente fornecida pelo FAP. ............................................................................ 64

Figura 8.15 – Corrente na carga não linear. ............................................................................. 65

Figura 8.16 – Corrente na carga linear. .................................................................................... 65

Figura 8.17 – Setup de teste do FAP. ....................................................................................... 66

Figura 8.18 – Tensão no barramento do protótipo. .................................................................. 67

Figura 8.19 – Corrente da carga não linear. ............................................................................. 67

Figura 8.20 – Corrente do FAP. ............................................................................................... 68

Figura 8.21 – Corrente da rede. ................................................................................................ 68

xiv

LISTA DE TABELAS

Tabela 4.1 - Especificação do FAP. ......................................................................................... 20

Tabela 4.2 - Especificação do retificador (carga proposta). ..................................................... 21

Tabela 4.3 – Parâmetros obtidos para o retificador. ................................................................. 22

Tabela 4.4 – Especificação dos componentes para o FAP. ...................................................... 28

Tabela 7.1 - Especificação do sensor de corrente ACS712. ..................................................... 43

Tabela 7.2 - Especificação do MOSFET IRFP460. ................................................................. 45

Tabela 7.3 - Especificação do driver IR2104. .......................................................................... 45

Tabela 7.4 – Parâmetro obtidos para a indutância

. ............................................................. 47

Tabela 7.5 - Especificação do relé SRD-S-12D ....................................................................... 51

Tabela 7.6 - Especificação do Amp Op LM324. ...................................................................... 53

xv

LISTA DE SIGLAS

Sigla

Significado

FAP

Filtro Ativo Paralelo

FAS

Filtro Ativo Série

THD

‘Total Harmonic Distortion’, Distorção Harmônica Total

PFC

‘Power Factor Correction’, Correção de Fator de Potência

VSI

‘Voltage Source Inverter’, Inversor de Tensão

FB-VSI

‘Full Bridge Voltage Source Inverter’, Inversor de Tensão em Ponte

Completa

CSI

‘Current Source Inverter’, Inversor de Corrente

CC

Corrente Contínua

CA

Corrente Alternada

FB

‘Full Bridge’, Ponte Completa

PWM

‘Pulse Width Modulation’, Modulação por Largura de Pulso

A/D

‘Analog-to-Digital’, Analógico-Digital

CI

Circuito Integrado

FTMA

Função de transferência de Malha Aberta

FTMF

Função de transferência de Malha Fechada

BP

Banda Passante

MF

Margem de Fase

AmpOp

Amplificador Operacional

RMS

‘Root-Mean-Square’, Média Quadrática

MOSFET

‘Metal-Oxide Semiconductor Field-Effetc Transistor’, Transistor de

Efeito de Campo

DSP

‘Digital Signal Processor’, Processador Digital de Sinais

MCU

Microcontrolador

PCB

‘Printed Circuit Board’, Placa de Circuito Impresso

FW

‘Firmware’

xvi

LISTA DE SÍMBOLOS

Unidade

Significado

compensador de corrente;

ganho do modulador PWM

função de transferência do inversor

ganho do sensor de corrente

ganho do divisor de tensão do sensor de corrente

ganho do filtro anti-aliasing

ganho do conversor A/D

referência da corrente

função de transferência da malha de corrente do inversor

função de transferência da planta de tensão

ganho do sensor de tensão

referência da tensão do barramento CC

Erro da malha de tensão

1

1. INTRODUÇÃO

A evolução tecnológica no campo da eletrônica tem propiciado inúmeros benefícios à

humanidade. Todos os dias, novos equipamentos e dispositivos eletrônicos são lançados no

mercado, tornando-se cada vez mais presentes e indispensáveis nas vidas das pessoas. Porém,

a grande e contínua proliferação destes equipamentos eletrônicos, tanto nas indústrias quanto

nas residências causam grande preocupação, uma vez que, por operarem de forma não linear,

drenam correntes distorcidas da rede elétrica. A eletrônica de potência tem um papel

fundamental neste processo, pois o processamento eficiente da energia é um tema de

relevância cada vez maior, em função da grande demanda de energia e dos aspectos

ambientais inerentes aos processos de geração.

Hoje em dia são apresentadas novas normas e recomendações [1] e [2], as quais

estabelecem padrões para a melhoria da qualidade da energia elétrica, principalmente em

relação ao fator de potência, taxa de distorção harmônica (THD) e emissão de ruídos (EMI).

A tendência é que estes padrões passem a ser exigidos pelas concessionárias de energia

elétrica, fazendo com que haja a necessidade de solucionar os problemas causados por cargas

não lineares.

Uma topologia comumente encontrada nos equipamentos eletrônicos é o retificador

com filtro capacitivo, estando presente no estágio de entrada de diversos equipamentos. Esta

estrutura drena da rede elétrica, correntes com elevadas conteúdo harmônico conforme

apresentado na Figura 1.1. A circulação de corrente harmônicas pelas impedâncias do sistema

distorce a tensão no ponto de acoplamento comum, e, portanto, podem afetar outras cargas

conectadas a este, além de comprometer o fator de potência [3].

2

Figura 1.1 – Forma de onda da corrente drenada pelo retificador com filtro capacitivo [4].

Uma solução de caráter corretivo para o problema da circulação de harmônicos no

sistema elétrico é a utilização de filtros passivos, que são estruturas constituídas por

elementos passivos, como indutores e capacitores, que quando associados operam como

filtros de bloqueio ou de confinamento de harmônicos. Embora sejam estruturas de baixo

custo, as mesmas apresentam algumas desvantagens, como por exemplo, elevado peso e

volume, possibilidade de ressonância com o sistema e a operação depende da impedância da

rede. Existe a alternativa da utilização de filtros híbridos (associação entre o filtro ativo e o

filtro passivo), porém não serão abordados, pois será dada uma atenção maior ao filtro ativo

que é o objetivo de estudo neste trabalho.

Qualquer inversor bidirecional em corrente pode ser utilizado como filtro ativo. As

diferentes formas de se conectar estes filtros à rede elétrica (série e paralelo) definem as

características do tipo de correção desejada. Segundo [4] e [5], a conexão em série do filtro

ativo é empregada para compensação da tensão da rede, isolando a carga de flutuações de

tensão e possíveis distorções harmônicas. A conexão em paralelo é utilizada para correções de

distorções na corrente.

3

Segundo [6], tanto os inversores de corrente como os de tensão podem ser utilizados

como filtro ativo. Nos inversores de tensão (VSI – Voltage Source Inverter - Figura 1.2) a

tensão do barramento (

) é mantida constante e superior à máxima tensão da fonte de

alimentação. Por dualidade, para o inversor de corrente (CSI – Current Source Inverter Figura 1.3) tem-se que a corrente de barramento (

) deve ser superior ao pico da corrente a

ser compensada pela rede de alimentação (corrente de carga), o que caracteriza elevadas

perdas no indutor de barramento e nos semicondutores. Além disso, o número de

semicondutores que conduz simultaneamente é o dobro do VSI, tendo em vista que o

interruptor possui um diodo em série, aumentando ainda mais as perdas por condução. Por

estas razões, a estrutura mais adequada e utilizada como filtro ativo é o inversor de tensão

(VSI).

Figura 1.2 - Inversor de tensão (VSI).

Figura 1.3 - Inversor de corrente (CSI).

Conforme comentado anteriormente, o filtro ativo paralelo (FAP) é empregado de

forma a compensar os harmônicos de corrente produzidas por cargas não lineares. Ele é

conectado em paralelo com a carga e com a rede, atuando como um dispositivo que injeta ou

drena corrente no ponto de conexão, de maneira que a corrente total drenada da rede elétrica,

composta pela corrente de filtro mais a corrente de carga, seja puramente senoidal e em fase

com a tensão da mesma (Figura 1.4). Desta forma, o conjunto carga não linear mais filtro

ativo possui um comportamento de carga resistiva para a rede elétrica, resultando em um fator

de potência muito próximo à unidade.

4

Figura 1.4 – Filtro ativo monofásico conectado paralelamente à rede e a carga não linear [4].

Com uma estratégia de controle adequada, o FAP também é capaz de compensar

reativo capacitivo ou indutivo produzido pelas cargas. Esta característica contribui para a

versatilidade do FAP.

O objetivo principal deste trabalho visa a implementar um Filtro Ativo Paralelo (FAP)

de 1 kVA, controlado de forma digital por um microcontrolador ARM, com vistas à redução

da distorção harmônica produzida pela carga não linear na rede elétrica.

5

2. CARGAS NÃO LINEARES, FILTROS ATIVOS E A QUALIDADE

DA ENERGIA ELÉTRICA

Neste capítulo serão apresentados os três principais pilares para o desenvolvimento

deste trabalho:

A qualidade da energia elétrica;

As cargas não lineares, especialmente retificadores não controlados, amplamente

utilizados em equipamentos eletrônicos que drenam correntes com elevado

conteúdo harmônicos;

Os filtros ativos de potência: em especial o filtro ativo paralelo (FAP), que se

apresenta como uma solução eficaz com vista à redução da distorção harmônica

de corrente causada pelas cargas não lineares.

2.1

A Qualidade da Energia Elétrica

A qualidade da energia elétrica tem sido alvo de constante preocupação e motivação

para novos estudos nas últimas décadas. A qualidade da energia elétrica não é mais vista

como uma questão unilateral, onde a única responsável é a concessionária de energia, uma

vez que diversos problemas têm origem no consumidor. Neste cenário, consumidores e

concessionárias de energia dividem responsabilidades que são pontuadas por normas

específicas.

Um problema de qualidade de energia são, por exemplo, desvios de tensão, corrente

ou frequência, que podem resultar em falhas ou mau funcionamento do equipamento. Assim,

para definir o que seja qualidade de energia elétrica, tem-se que tratar de vários problemas

que afetam os consumidores da energia elétrica ou os seus usuários indiretos. Esses problemas

vão desde os incômodos visuais provocados pela variação luminosa devido à má regulação da

tensão até a interferência em equipamentos eletrônicos sensíveis, causada por interrupções no

fornecimento de energia ou por fenômenos de mais alta frequência, sobreaquecimento de

máquinas elétricas devido às harmônicas, etc.

6

Podemos citar alguns fatores que motivam a preocupação com a qualidade da energia

da rede elétrica:

O aumento expressivo de cargas não lineares, tanto nas residências como nas

indústrias, que afetam a qualidade da energia da rede elétrica em função do alto

conteúdo harmônico das correntes drenadas por estas;

A maior compreensão por parte dos usuários dos fenômenos presentes na rede

elétrica, que por sua vez têm condições de exigir das concessionárias uma energia

de melhor qualidade;

A grande quantidade de equipamentos sensíveis conectados à rede, como por

exemplo, os equipamentos hospitalares, que dependem de uma energia de boa

qualidade para operarem corretamente.

2.1.1 Harmônicos

Os harmônicos são tensões com frequências múltiplas inteiras daquela dita

fundamental (frequência de operação do sistema, normalmente 50Hz ou 60Hz). Sendo assim

em um sistema com frequência nominal igual a 60Hz, teremos harmônicos nas frequências de

120Hz (2º harmônico), 180Hz (3º harmônico) e assim por diante.

Conforme comentado, a distorção harmônica é causada pela presença de cargas não

lineares no sistema. Nestes equipamentos a corrente drenada não é proporcional à forma da

tensão aplicada.

A circulação de correntes harmônicas no sistema elétrico implica diversos efeitos

indesejados [7], tais como:

Aumento da temperatura de operação e das perdas em capacitores, motores e

transformadores;

Atuação indevida de equipamentos de proteção;

Interferência e/ou falhas de operação em equipamentos sensíveis;

Excitação de ressonâncias nas impedâncias do sistema;

Distorção de tensão, em função da circulação de correntes harmônicas nas

impedâncias do sistema.

7

2.2

As Cargas não Lineares

As cargas mais prejudiciais ligadas ao sistema elétrico são as cargas do tipo não linear,

ou seja, que não drenam da fonte de alimentação uma corrente puramente senoidal. Pode-se

citar como este tipo de carga os aparelhos eletrônicos que necessitam um circuito especial na

entrada: fontes chaveadas, retificadores, gradadores, dentre outros. Estes tipos de carga

drenam da rede elétrica uma corrente altamente distorcida, com um número elevado de

harmônicas.

Os retificadores estão presentes em diversos equipamentos, e por ser o foco principal

deste trabalho, serão examinados de forma mais detalhada a seguir.

Como a tensão da rede é geralmente alternada, faz-se necessária a utilização de um

estágio inicial de processamento de energia, que converta a tensão alternada em tensão

contínua. A estrutura de potência comumente utilizada é o retificador monofásico a diodos

com filtro capacitivo. A Figura 2.1 ilustra esta estrutura.

Figura 2.1 – Retificador monofásico com filtro capacitivo.

Para que a tensão sobre a carga possa ser considerada uma fonte de tensão constante, é

necessário utilizar um capacitor com elevada capacitância. Como a transferência de energia da

fonte para o banco ocorre em pequenos espaços de tempo, as correntes de entrada do

conversor têm uma característica impulsiva, apresentando elevados picos, elevada distorção

harmônica e grande fator de crista (razão entre os valores de pico e eficaz).

O formato da corrente drenada por este tipo de carga é apresentado na Figura 2.2,

juntamente com a tensão de entrada (tensão da rede).

8

Figura 2.2 – Tensão e corrente drenada da rede.

2.3

Filtros Ativos

Os princípios básicos dos filtros ativos de potência foram apresentados em 1971, por

H. Sasaki e T. Machida. O cancelamento das correntes harmônicas da carga não linear era

feito através de injeção de correntes harmônicas de mesma amplitude e fase oposta através do

filtro. Como a estrutura de potência do filtro atuava como um amplificador linear, o

rendimento do mesmo era muito baixo e consequentemente impraticável para sistema de

potência [8].

O conceito de filtro ativo, tal qual é conhecido atualmente, foi introduzido em 1976

por Gyugyi e Strycula, os quais apresentaram uma família de filtros constituídos de

conversores PWM com transistores de potência [9].

Os filtros ativos foram inicialmente propostos para a redução de conteúdo harmônico

gerado por conversores utilizados nos sistemas de transmissão em corrente contínua (HVDC).

Como na década de 70 não existiam transistores de alta potência, o filtro não poderia ser

implementado em um sistema de potência real.

A evolução tecnológica dos dispositivos de potência (MOSFET, IGBT), bem como os

componentes de controle (Microcontroladores, DSPs, FPGAs, ARMs, sensores de efeito Hall)

tem sido um fator motivador para os pesquisadores da área. Ao longo dos anos, diversos

trabalhos foram publicados, com novas estratégias para a determinação dos sinais de

referência, técnicas de controle e estruturas de potência.

9

2.3.1 Classificação dos Filtros Ativos

Os filtros monofásicos têm sido pouco estudados, uma vez que seu emprego está

restrito a sistema de baixa potência ou aplicações específicas [10], mesmo assim, é importante

observar que os filtros ativos monofásicos constituem a melhor solução para a correção do

fator de potência em cargas de baixa potência, nas quais não se justifica a utilização de filtros

passivos ou pré-reguladores.

Gyugyi e Strycula [9] separam os filtros ativos em duas categorias, conforme a sua

conexão com a rede elétrica: tipo série (FAS) ou paralelo (FAP), comumente referenciado na

literatura como filtro shunt).

Figura 2.3 - Filtro ativo série.

Figura 2.4 – Filtro ativo paralelo.

10

Também existe uma terceira e quarta categorias denominadas como filtro híbrido e

filtro universal, que são nada mais do que associações dos filtros ativos e passivos e das

topologias série e paralelo respectivamente [4]. O objetivo de estudo deste trabalho está

focado nos filtros Ativos Paralelos.

2.3.2 Filtro Ativo Paralelo

O filtro ativo do tipo paralelo (FAP) é geralmente empregado para corrigir harmônicas

de corrente de cargas não lineares. Ele é conectado em paralelo com a rede e com a carga,

onde ele atua como um dispositivo que injeta ou drena uma corrente do ponto onde foi

conectado de forma que a corrente total drenada da rede elétrica (corrente da carga mais a

corrente do filtro ativo seja senoidal). Pela rede elétrica circula então apenas a componente

fundamental da corrente de carga, resultando para a rede elétrica um comportamento de carga

resistiva (carga não linear mais filtro ativo), como se pode observar na Figura 2.5.

Figura 2.5 – Princípio de funcionamento de um FAP.

Para facilitar o entendimento do princípio de funcionamento do FAP são apresentadas

na Figura 2.6 as correntes drenada da rede, drenada/injetada pelo FAP e drenada pela carga

para o FAP funcionando em paralelo com uma carga não linear do tipo retificador com filtro

capacitivo.

11

Figura 2.6 - Corrente da rede, da carga e do FAP.

Observando a Figura 2.6 verifica-se que a corrente drenada da rede (rosa) é a soma da

corrente drenada pela carga (amarelo) mais a corrente drenada/injetada pelo FAP (verde).

O FAP não processa potência ativa. Por ele circula apenas uma potência reativa para

compensar as harmônicas de corrente da carga ou o reativo de deslocamento da mesma. Desta

forma, as perdas no FAP são menores do que em relação às do FAS, visto que o último

processa toda a corrente de carga, como será visto adiante.

É importante salientar que não é necessário desconectar a carga para acrescentar o

FAP, pois o mesmo é conectado em paralelo com a rede, assim, caso o FAP deixar de operar,

a carga continua sendo alimentada normalmente pela rede, porém com um baixo fator de

potência, além disso, o FAP tem a capacidade de se adaptar a diferentes tipos de cargas (não

lineares e lineares) sem haver a necessidade de um conhecimento prévio das cargas, bastando

apenas respeitar os limites de potência para a qual o FAP foi projetado.

12

3. ESTRUTURA DO FAP, MODULAÇÃO E ESTRATÉGIAS DE

CONTROLE

Para realizar o projeto dos estágios de potência e controle de um filtro ativo paralelo,

conforme apresentado em [4], [6], [11] e [12], deve-se primeiro definir alguns tópicos

essenciais, como: estrutura do FAP, tipo de modulação que será utilizada e a estratégia de

controle.

A estrutura que possui mais características adequadas para operação como FAP

segundo Souza [5] é o inversor de tensão em ponte completa. Dentre elas podemos citar:

O FAP funciona como um caminho de baixa impedância para as harmônicas de

corrente, emulando uma carga linear;

Podem compensar a defasagem entre a tensão da rede e a corrente da carga;

Comparada com filtros passivos, possui um volume menor;

Não há problemas de ressonância com a rede;

Tem capacidade de se adaptar as modificações da carga;

Não é necessário um conhecimento prévio rede antes da instalação;

Esta estrutura permite o emprego de uma modulação PWM senoidal com três níveis,

que também será comentada neste capítulo. Serão apresentadas duas estratégias de controle

com suas respectivas características para o controle do FAP.

3.1

Estrutura do Filtro Ativo Paralelo

Conforme já comentado anteriormente, os inversores bidirecionais em corrente podem

ser empregados para operação como filtro ativo. Tanto os inversores de corrente como os de

tensão podem ser utilizados.

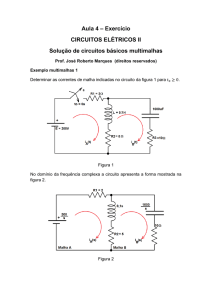

13

O inversor escolhido para compensar a carga proposta é o inversor de tensão em ponte

completa (VSI-FB – Voltage Source Inverter – Full Bridge apresentado na Figura 3.1. Apesar

deste inversor apresentar quatro interruptores, a máxima tensão sobre os mesmos é limitada

pela tensão de barramento que é proveniente de um capacitor ou um banco de capacitores, o

que facilita a malha de controle de tensão, além disso, existe a possibilidade de se aplicar uma

modulação PWM senoidal com três níveis. Por estas características este inversor é indicado

para potências médias (de 500 VA a 10 kVA).

Figura 3.1 – Inversor de tensão em ponte completa (VSI-FB) [4].

3.2

Modulação a Três Níveis

A modulação é um processo de variação de um sinal modulador, aquele que se deseja

reproduzir, através da influência de um sinal portador. A modulação empregada é, em geral, a

modulação por largura de pulso, conhecida por sua sigla em inglês PWM (pulse-width

modulation).

Será empregada para o controle do FAP a modulação PWM senoidal a três níveis, cuja

forma de geração é ilustrada pela Figura 3.2. Na modulação a três níveis, o valor da tensão na

saída será +Vf ,0 ou – Vf, conforme a onda moduladora senoidal apresente valor instantâneo

maior ou menor que a onda triangular respectivamente.

14

Figura 3.2 – Modulação senoidal três níveis.

3.3

Estratégia de Controle

Será utilizada a técnica de monitoramento da corrente da rede. Nesta técnica, faz-se

necessária a utilização de 3 sensores: um para monitoramento da corrente da rede, um para a

aquisição de uma senoide de referência da rede, e o terceiro para monitoramento da tensão de

barramento CC, conforme apresentado na Figura 3.3.

15

Figura 3.3 – Monitoramento da corrente de rede.

A estratégia de controle exige uma malha de corrente (rápida) e uma de tensão (lenta)

externa. Na Figura 3.4, são apresentados todos os elementos e ganhos das duas malhas de

controle.

Figura 3.4 – Diagrama de blocos da estrutura de controle.

A modelagem do conversor e a metodologia de projeto dos controladores para ambas

as malhas serão detalhados na sequência.

16

3.3.1 Modelagem do Inversor

Conforme apresentado por Souza [5], a equação (3.1) estabelece a função de

transferência do modelo de pequenos sinais da corrente de saída do inversor em função da

razão cíclica.

̂

̂

(3.1)

3.3.2 Malha de Corrente

A malha de corrente faz com que a corrente total drenada da rede elétrica siga uma

referência senoidal que é amostrada da rede pelo sensor de tensão CA. Esta malha deve ser

rápida para que o filtro ativo possa gerar as harmônicas de corrente desejadas. A estrutura de

controle da malha de corrente é apresentada na Figura 3.5.

Figura 3.5 – Estrutura de controle da malha de corrente.

Os blocos no domínio S, apresentados na Figura 3.5 representam:

– compensador de corrente;

- ganho do modulador PWM;

– função de transferência do inversor;

- ganho do sensor de corrente;

- ganho do divisor de tensão do sensor de corrente;

- ganho do filtro anti-aliasing (ver seção 7.12);

- ganho do conversor A/D;

– referência da corrente.

17

O diagrama de blocos do controle da corrente do FAP é apresentado na Figura 3.6.

Figura 3.6 – Diagrama de blocos para o controle da corrente do FAP.

A corrente da rede é monitorada e comparada com uma corrente de referência senoidal

e em fase com a tensão da rede. O resultado desta comparação (sinal de erro

) é tratado por

um compensador de corrente, o qual gera o sinal de controle. Este sinal é então comparado

com duas formas de onda dente de serra defasadas de 180º entre si, as quais darão origem à

modulação à três níveis desejada.

3.3.3 Malha de Tensão

A malha de tensão é responsável por garantir a tensão no barramento CC constante,

segundo [6] pelo menos 30% maior que a tensão de pico da rede, e com uma ondulação que

não ultrapasse a especificada para o projeto.

A malha de tensão deve ser bastante lenta, pois ela atua na amplitude da corrente

senoidal que é drenada da rede e, sendo assim, se esta malha for rápida ela fará com que a

18

corrente senoidal drenada da rede se distorça devido ao surgimento de picos de corrente de

diferentes amplitudes e de distorções na corrente de referência.

A função de transferência

, apresentada em [6], é expressa pela equação

(3.2).

(3.2)

A estrutura de controle da malha de tensão é apresentada na Figura 3.7.

Figura 3.7 - Estrutura de controle da malha de tensão.

Os blocos no domínio ‘s’, apresentados na Figura 3.5 representam:

– função de transferência da malha de corrente do inversor;

– função de transferência da planta de tensão;

- ganho do sensor de tensão;

- ganho do filtro anti aliasing;

- ganho do conversor A/D;

– referência da tensão do barramento CC.

O diagrama de blocos do controle da tensão do FAP é apresentado na Figura 3.8.

19

Figura 3.8 - Diagrama de blocos para o controle do FAP.

A tensão de barramento é amostrada através de um divisor resistivo ou sensor de efeito

Hall e comparada com uma tensão de referência

compensador de tensão, o qual gera um sinal

referência para o controle da corrente.

. O sinal de erro

é tratado por um

que determinará a amplitude da corrente de

20

4. PROJETO DOS ELEMENTOS PASSIVOS DO FAP

Neste capítulo serão apresentados os cálculos para os componentes do estágio de

potência do FAP (indutor e capacitor), bem como o projeto da carga não linear.

Será também apresentada uma metodologia para o projeto das malhas de controle de

tensão e corrente, especificando as frequências de cruzamento das respectivas malhas e os

ganhos relacionados aos sensores de tensão e corrente.

4.1

Especificação do FAP

Para o projeto do filtro ativo paralelo, as especificações das características de operação

devem ser feitas:

Tabela 4.1 - Especificação do FAP.

Especificação

Valor

Tensão Eficaz da Rede

Frequência de Operação da Rede (

127 V

)

Potência Aparente da Carga (S)

Potência Ativa da Carga (P)

Potência Reativa da Carga (Q)

Tensão no Barramento CC

Ripple de tensão no Barramento CC

Ripple de Corrente no Indutor do FAP

Frequência de Comutação dos Interruptores ( )

60 Hz

1000 VA

550 W

835,16 VAR

350 V

5 %

15 %

30k Hz

As ondulações de tensão e corrente no filtro estão estipuladas dentro da faixa

usualmente empregadas devido ao tamanho físico que os componentes assumiriam.

21

4.2

Projeto

4.2.1 Projeto da Carga

A ponte retificadora usada como carga (apresentada Figura 4.1) é projetada de modo

que a potência aparente total S demandada pela carga seja de 1kVA

Figura 4.1 - Retificador monofásico de onda completa com filtro capacitivo.

As especificações de projeto do retificador monofásico de onda completa com filtro

capacitivo estão apresentadas na Tabela 4.2.

Tabela 4.2 - Especificação do retificador (carga proposta).

Especificação

Tensão Eficaz da Rede

Frequência de Operação da Rede

Potência Aparente (S)

Ripple de Saída

Valor

127 V

60 Hz

1000 VA

10 %

Sabe-se que o fator de potência estimado para um retificador monofásico com filtro

capacitivo projetado para esta faixa de potência é de

(estimativa pessimista).

Assim, através da expressão, pode-se obter a potência ativa demandada pelo retificador.

(4.1)

22

Conhecendo a potência ativa do retificador, utilizou-se a metodologia apresentada em

[13] para realizar o projeto do retificador. Sabendo-se a ondulação da tensão de saída

podemos definir o valor do capacitor de saída

e o resistor de saída

do retificador como

sendo:

(4.2)

(4.3)

Onde

,

e

são obtidos através da tensão de pico da rede e da

ondulação de tensão do capacitor de saída

. Os parâmetros finais obtidos para o retificador

estão apresentados na Tabela 4.3.

Tabela 4.3 – Parâmetros obtidos para o retificador.

Componente

Valor

4.2.2 Indutor do FAP

Para determinar as características da corrente processada pelo FAP precisa-se

primeiramente estabelecer equações para a ondulação de corrente no indutor

. A forma de

onda da tensão sobre os terminais ab da ponte completa está apresentada na Figura 4.2.

23

Figura 4.2 - Tensão nos terminais ab do FAP.

Conforme verificamos na Figura 4.3, a tensão sobre o indutor

é a diferença entre a

tensão nos terminais ab e a tensão da rede.

Figura 4.3 - Terminais a e b do Inversor de tensão em ponte completa [4].

Na operação a três níveis a tensão

e

para

varia entre zero e

para

e zero

. Devido à simetria da forma de onda da tensão

, será analisada

apenas o primeiro intervalo.

A análise pode ser realizada quando os interruptores

e

estão conduzindo, de

acordo com a Figura 4.3. Assim, tem-se a equação (4.4):

(4.4)

24

Considerando que a tensão sobre o indutor, dentro do intervalo de análise, não varie, a

partir de (4.4) tem-se (4.5).

(4.5)

O intervalo de tempo

da equação (4.5), para uma modulação dente de serra, é

calculado de acordo com (4.6)

(4.6)

Como pelo FAP não deve circular potência ativa (apenas o suficiente para suprir as

perdas), pode-se considerar que a tensão

possui uma componente fundamental de mesma

amplitude, frequência e fase que a tensão da rede. Assim sendo, obtemos (4.7).

(4.7)

Em [6] é apresentado que:

(4.8)

Substituindo (4.7) em (4.8) obtém-se a razão cíclica instantânea para meio período de

operação (

), a qual é expressa por (4.9).

(4.9)

Substituindo (4.9) em (4.6), e o resultado em (4.5), obtém-se a equação de ondulação

no indutor do FAP para o semiciclo positivo da rede, conforme (4.10).

25

{

[

] }

(4.10)

A relação entre o pico da tensão da rede e o valor da tensão de barramento

conhecida como índice de modulação (

é

), de acordo com a equação (4.11). Para suprir a

demanda de corrente proveniente da carga, o valor da tensão de barramento deve ser (pelo

menos) 30% da tensão de pico da rede.

(4.11)

A ondulação de corrente parametrizada é apresentada em (4.12).

(4.12)

̅̅̅̅

Através da equação (4.13) e (4.12) em (4.10), tem-se a ondulação de corrente

parametrizada, em função de

e

, para o semiciclo positivo de operação (

̅̅̅̅

[

]

).

(4.13)

Através da equação (4.13) traça-se o gráfico da Figura 4.4, que apresenta a ondulação

de corrente parametrizada no indutor do FAP para diferentes valores do índice de modulação

(

), durante o intervalo

.

26

Figura 4.4 - Ondulação de corrente parametrizada [4].

De acordo com o gráfico da Figura 4.4, percebe-se que para a modulação a três níveis,

a ondulação máxima de corrente parametrizada é igual a 0,25 e é independente do índice de

modulação

e

.

Desta forma, a indutância do filtro ativo paralelo pode ser obtida através da expressão

(4.12), considerando a ondulação de corrente parametrizada definida pela Figura 4.4 e os

valores apresentados na Tabela 4.1. Assim, reescrevendo (4.12) obtém-se a expressão (4.14),

que será utilizada para o cálculo da indutância do FAP.

̅̅̅̅̅̅̅̅̅̅̅

(4.14)

Para a utilização da expressão (4.12), é necessário calcular o valor da ondulação

máxima de corrente permitida no indutor. A ondulação de corrente apresentada na Tabela 4.1

é uma porcentagem da corrente de pico da rede (corrente de entrada). Como esta corrente será

considerada senoidal e em fase com a tensão da rede, o valor da corrente eficaz drenada da

rede é obtida por (4.15).

(4.15)

A corrente de pico foi estimada através de simulação com o software PSIM [14]. O

valor da mesma é apresentado pela equação (4.16):

27

(4.16)

Com o valor da corrente de pico da rede, calcula-se a ondulação (10%) de corrente

máxima no indutor do filtro através de (4.17):

(4.17)

De acordo com a Figura 4.4, para o índice de modulação encontrado por (4.11),

, a máxima ondulação de corrente parametrizada é 0,25. Assim, através da equação

(4.13) e da Tabela 4.1 calcula-se a indutância necessária para o filtro ativo através de (4.18):

̅̅̅̅̅̅̅̅̅̅̅

(4.18)

4.2.3 Banco de Capacitores do FAP

Um valor inicial para o capacitor de barramento do FAP pode ser encontrado através

da relação (4.19), que calcula a capacitância de um retificador monofásico de onda completa

com filtro capacitivo, fornecida por [13].

(

A potência reativa do FAP (

)

) é, na verdade, a potência que será processada pelo

mesmo, ou seja, toda a potência reativa demandada pela carga (

√

(4.19)

√

) apresentada em (4.20):

(4.20)

28

Já os valores

e

são obtidos através da ondulação de tensão do

barramento apresentado na Tabela 4.1.

(4.21)

(

)

Vale lembrar que existem dois critérios para a escolha de capacitores: o critério de

ondulação da tensão apresentado pela equação (4.19) e o critério de capacidade de condução

de corrente.

A dificuldade de se encontrar capacitores com capacidade de corrente elevada faz com

que seja necessária a associação de capacitores em paralelo, reduzindo desta forma a

resistência série do barramento.

Os parâmetros obtidos para o filtro ativo estão apresentados na Tabela 4.4.

Tabela 4.4 – Especificação dos componentes para o FAP.

Especificação/Parâmetro

Valor

Índice de modulação

0,51

Máxima ondulação de corrente parametrizada no indutor

0,25

Capacitor

Indutor

(estimativa inicial)

29

5. PROJETO DOS ELEMENTOS DE CONTROLE DIGITAL

Para o projeto das malhas de controle de tensão e corrente deve-se analisar a função de

transferência de malha aberta (FTMA) do sistema. Todavia, para o correto dimensionamento

dos compensadores envolvidos, alguns conceitos devem ser reforçados, como por exemplo:

frequência de cruzamento, margem de fase e banda passante.

Função de Transferência de Malha Aberta (FTMA): é a composição no domínio

‘z´ de todos os blocos que representam a malha de controle em laço aberto, ou

seja, o modelo da planta, o compensador, o ganho dos sensores, considerados em

cascata sem que se realimente a malha. No domínio ‘z´, os blocos da FTMA são

multiplicados um a um;

Frequência de cruzamento

): é a frequência na qual o ganho da FTMA é 0dB.

Esta frequência determina a largura de banda passante;

Banda passante (BP): é a banda definida pela frequência de cruzamento, que

caracteriza a velocidade de resposta. Quanto maior a banda passante da FTMA,

mais rápida será a resposta do sistema;

Margem de fase (MF): a margem de fase expressa diretamente a robustez do

sistema a perturbações. Quanto maior a margem de fase da FTMA, mais estável

será o sistema em malha fechada. Sua definição é apresentada na equação (5.1):

(5.1)

Onde

representa a fase da FLMA na frequência de cruzamento.

Função de Transferência de Malha Fechada (FTMF): sistema cuja informação da

variável de saída é utilizada como argumento na determinação da variável de

controle.

Lugar das Raízes (LR): o método do lugar das raízes (LR) é um método gráfico

que permite esboçar a trajetória dos pólos de um sistema em malha fechada, em

função do ganho de um sistema.

O projeto consiste então em ajustar os parâmetros do circuito das malhas de corrente e

tensão, de tal forma que se tenha a velocidade de resposta desejada (largura da banda

passante) e que o sistema seja estável em malha fechada (margem de fase adequada).

30

5.1

FTMA de Corrente

A função de transferência de malha aberta (FTMA) digital de corrente é a composição

de todos os blocos que representam a malha de controle em laço aberto (ver Figura 5.1), no

domínio ‘z’, ou seja, a função de transferência que relaciona a corrente com a razão cíclica do

inversor (

corrente (

, o compensador de corrente (

, ganho do modulador PWM (

de transferência do filtro anti-aliasign (

, o ganho do amostrador de

, ganho do conversor AD (

, ganho do divisor resistivo (

, função

,

considerados em cascata sem que se realimente a malha. No domínio ‘z’, os blocos da FTMA

são multiplicados um a um, o que resulta na expressão (5.2):

(5.2)

Sendo:

*

(5.3)

Figura 5.1 – FTMA da malha de corrente.

A primeira etapa em um projeto de controle é determinar um modelo que represente de

modo satisfatório a função de transferência do inversor. Conforme descrito no capítulo

anterior (3.3.1), temos que a função de transferência do inversor é dada por (5.4).

(5.4)

31

Juntamente com a função de transferência do inversor, é acrescida a função de

transferência do filtro anti-aliasign. Segundo Bonfim [15], temos que a função de

transferência de um filtro é dada pela equação (5.5). Maiores detalhes sobre o filtro antialiasign são apresentados na seção 7.12.

(5.5)

Em seguida as duas funções no domínio ‘s’ (inversor e filtro) foram transformadas

para o domínio ‘z’ através da função ‘c2d’, ou ‘continuos to discrete’ do programa MATLAB

[16], que apresenta a sintaxe exibida em (5.6).

(5.6)

Foi utilizado período de amostragem ( ) igual a ⁄ com o método de transformada

de Tustin. As equações (5.7) e (5.8) apresentam respectivamente as funções transferências do

inversor e do filtro anti-aliasign no domínio ‘z’.

(5.7)

(5.8)

5.2

Projeto do Compensador de Corrente Digital

A equação (5.9) é obtida a partir do produto das equações (5.7) e (5.8).

(5.9)

32

Através da ferramenta SisoTool do Matlab é possível gerar o diagrama de Bode da

equação (5.9), apresentado na Figura 5.2.

Figura 5.2 – Diagrama de Bode do inversor e do filtro anti-aliasign.

Quanto maior a frequência, melhor será a resposta dinâmica do sistema. No entanto,

para evitar os efeitos do chaveamento sobre o sinal de controle, utilizou-se ⁄ da frequência

de chaveamento, ou seja,

. Segundo [4], a margem de fase (

usual para os

filtros ativos está em torno de 55°. Desta forma foram ajustados os pólos e zeros a fim de

garantir estas especificações.

A equação (5.3) apresenta o ganho

, como sendo o produto dos ganhos a seguir:

(5.10)

(5.11)

(5.12)

33

(5.13)

Logo teremos que:

(5.14)

*

Alocando os pólos e zeros do compensador com o auxílio do diagrama de Bode,

obteve-se o compensador apresentado na equação (5.15).

(5.15)

Na interface da ferramenta SisoTool são inseridos os valores da função de

transferência do inversor com o filtro, o ganho

compensador

e a função de transferência do

. A Figura 5.3 apresenta o menu onde são inseridos os ganhos da

FTMA.

Figura 5.3 - Inserção dos ganhos da FTMA de corrente.

Na sequência é inserido o ganho K (22) do compensador

visto na Figura 5.4.

, como pode ser

34

Figura 5.4 – Ganho do compensador.

O diagrama de Bode da FTMF obtido pode ser visto na Figura 5.5 e o gráfico do LR

na Figura 5.6. Verifica-se que a FTMF de corrente apresentou na frequência de cruzamento

(

) uma margem de fase de 54,3° para o sistema.

Figura 5.5 – Diagrama de Bode da FTMF de corrente.

35

Figura 5.6 – Gráfico do LR da FTMF de corrente do FAP com controle digital.

O script utilizado no MatLab está apresentado na Apêndice A.

5.3

Projeto do Compensador de Tensão Digital

A função de transferência de malha aberta (FTMA) de tensão é a composição no

domínio ‘z’ de todos os blocos que representam a malha de controle em laço aberto (ver

Figura 5.7), ou seja, os ganhos associados à função de transferência de malha fechada da

corrente (

tensão (

), o compensador de tensão (

), o modelo da planta (

função de transferência do filtro (

), o ganho da malha de

), o ganho do sensor de tensão (

ea

), considerados em cascata sem que se realimente

a malha. No domínio ‘z’, os blocos da FTMA são multiplicados um a um, o que resulta na

expressão (5.16):

(5.16)

Onde:

36

(5.17)

*

Figura 5.7 - FTMA da malha de tensão.

Para o projeto do compensador de tensão, será utilizada a mesma metodologia descrita

no compensador de corrente.

Primeiramente encontra-se a função de transferência

, apresentada em [6], e

expressa pela equação (5.18).

(5.18)

Em seguida a mesma foi discretizada com o comando ‘c2d’ do MatLab.

(5.19)

A função de transferência do filtro anti-aliasign em 60Hz é apresentada em (5.20).

(5.20)

A equação (5.9) é obtida a partir do produto das equações (5.7) e (5.8).

37

(5.21)

Através do SisoTool é possível gerar o diagrama de Bode da equação (5.21),

apresentado na Figura 5.8.

Figura 5.8 - Diagrama de Bode da FTMA de tensão.

Para a malha de tensão, sabendo-se que a mesma deve ser lenta quando comparada

com a malha de corrente, será adotada uma frequência de cruzamento de 2 Hz.

Como a malha de corrente está algumas décadas acima da frequência de corte da

malha de tensão, esta se comporta como um ganho para a malha de tensão. Este ganho está

dividido em duas parcelas: o valor de pico da referência senoidal de corrente e o ganho da

propriamente dito (

. Estes ganhos estão ilustrados na Figura

5.9.

Figura 5.9 – Ganhos associados a

.

A corrente de pico de referência senoidal é calculada de acordo com (5.22) arbitrandose um valor para o ponto de operação do compensador de tensão.

38

(5.22)

Escolhendo um valor de operação de ⁄ da resolução do AD para o ponto de

operação do compensador de tensão (

e dos outros ganhos conforme

apresentados na etapa anterior, através de (5.23) calcula-se o valor de pico da corrente de

referência senoidal.

(5.23)

O

é encontrado analisando a FTMA de corrente para baixas frequências.

Este ganho é dado por:

(5.24)

A finalidade do sensor de tensão é fornecer uma amostra da tensão do barramento.

Será utilizado um divisor resistivo, o qual apresentará um ganho conforme apresentado na

equação (5.25):

(5.25)

Desta forma obtemos o ganho

através da equação (5.26):

*

(5.26)

Alocando os pólos e zeros do compensador com o auxílio do diagrama de Bode,

obteve-se o compensador implementado pela equação (5.27).

39

(5.27)

No SisoTool é carregado os valores dos ganhos

, da FTMA de tensão,

e a função de transferência do compensador de tensão

. A Figura 5.10

apresenta o menu onde são inseridos os ganhos da FTMA.

Figura 5.10 – Inserção dos ganhos da FTMA de tensão.

Na sequência é inserido o ganho K (

) do compensador

, como pode

ser visto na Figura 5.11.

Figura 5.11 – Ganho do compensador.

O diagrama de Bode da FTMF obtido pode ser visto na Figura 5.12 e o gráfico do LR

na Figura 5.13. Verifica-se que a FTMF de corrente apresentou na frequência de cruzamento

(

) uma margem de fase de 70,4° para o sistema.

40

Figura 5.12 - Diagrama de Bode da FTMF de tensão.

Figura 5.13 - Gráfico do LR da FTMF de tensão do FAP com controle digital.

O script utilizado no MatLab está apresentado na Apêndice B.

41

7. COMPONENTES E CIRCUITOS AUXILIARES

Neste capítulo serão apresentados os componentes principais utilizados para a

implementação do protótipo do filtro ativo, bem como o projeto dos circuitos auxiliares

relevantes à construção do protótipo de 1kVA.

A Figura 7.1 apresenta um diagrama de blocos da estrutura do protótipo do FAP.

Figura 7.1 – Diagrama de blocos do protótipo do FAP.

42

7.1

FRDM-KL25Z ARM Cortex M0+

A estrutura de controle e comando do protótipo foi desenvolvida com o kit FRDM-

KL25Z ARM Cortex M0+ da Freescale [17]. A FRDM-KL25Z (Figura 7.2) é uma

plataforma de desenvolvimento composta pelo microcontrolador Kinetis ARM ® Cortex ™M0+ série L.

Foi escolhido entre os diversos softwares de desenvolvimento para a FRDM-KL25Z

o CodeWarrior [18] da Freescale. O CodeWarrior contempla o Processor Expert, que se trata

de um software de programação em alto nível, o que facilita a programação e configuração do

kit.

Figura 7.2 - FRDM-KL25Z ARM Cortex M0+ [17].

A FRDM-KL25Z oferece:

Microcontrolador ARM MKL25Z128VLK4 MCU - 48 MHz, 128 KB de

memória flash, 16 KB SRAM;

Fácil acesso ao MCU I/O

8 canais de PWM;

14 canais de AD de 16 bits;

Facilidade de programação com o Processor Expert;

Gravação OpenSDA [19];

Depuração USB.

43

7.2

Sensor de Corrente ACS712

O sensor de corrente ca deve fornecer uma amostra da corrente drenada da rede para

o controlador de corrente conforme apresentado na Figura 7.3.

A máxima corrente drenada da rede com o uso do FAP será de 13 ampères. Assim,

optou-se pelo sensor de corrente ACS712-20 [20], que permite a leitura de até 20 ampères

eficazes. As suas especificações podem ser vistas na Tabela 7.1

Tabela 7.1 - Especificação do sensor de corrente ACS712.

Especificação

Máxima Leitura de Corrente Bidirecional

Tensão de Alimentação

Valor

20 A

5 V

Sensibilidade

100 mV/A

Offset

2,5 V

Isolação

2,1k Vrms

FONTE: Datasheet ACS712.

O esquema de ligação deste sensor é apresentado na Figura 7.3.

Figura 7.3 – Esquema de ligação do sensor de corrente ACS712 [20].

44

7.3

Senoide de Referência

A função do circuito apresentado na Figura 7.4 é fornecer uma amostra da corrente

de entrada, para que esta siga a referência senoidal da rede.

O circuito consiste primeiramente de um transformador abaixador para gerar uma

réplica da senoide da rede, porém com amplitude menor. Como o ARM que será utilizado não

permite níveis de tensões negativos, foram inseridos dois diodos polarizados, a fim de gerar

uma tensão de 1,4V para deslocar o centro da senoide. O divisor resistivo formado por R1 e R2

condiciona o sinal aos níveis de tensão (Figura 7.5) suportados pelos conversores A/D do

ARM.

Figura 7.4 – Circuito gerador da senoide de referência.

Figura 7.5 – Senoide de referência.

45

7.4

MOSFET IRFP460

O MOSFET escolhido foi o IRFP460 [21], N_Channel da Fairchild Semiconductor.

As características de tensão e corrente deste MOSFET são muito maiores que as exigidas pelo

projeto, o que aumenta a margem de segurança necessária para o seu desenvolvimento. As

características deste componente são apresentadas na Tabela 7.2

Tabela 7.2 - Especificação do MOSFET IRFP460.

Especificação

Valor

Tensão Dreno-Source

500 V

Tensão Gate-Source

±20 V

Corrente Máxima

20 A

0,27 Ω

RDS

FONTE: Datasheet IRFP460.

7.5

Driver IR2104

O driver é o dispositivo responsável por fornecer os pulsos de comando aos

interruptores (MOSFETs) dos braços da ponte completa. Nas estruturas em ponte completa

estes pulsos, tensão entre gate-source, devem ser isolados, devido ao fato de alguns

interruptores não apresentarem o ponto de source em comum.

O driver escolhido é o IR2104 [22], da International Rectifier. As suas

características são apresentadas na Tabela 7.3.

Tabela 7.3 - Especificação do driver IR2104.

Especificação

V offset

Corrente de Entrada

Gate drive supply

Vcc máxima

Tempo on/off

Deadtime

FONTE: Datasheet IR2104.

Valor

600 V

130m/270m A

10-20 V

25 V

680&150n s

520n s

46

Figura 7.6 - Esquema de ligação do driver IR2104 [22].

7.6

Indutor

.

Com o valor da indutância

obtido na seção 4.2.2.1, e com as características da

corrente do FAP pode-se realizar o projeto físico do indutor

. A metodologia utilizada para

o projeto está apresentada em [13] e [23] e o tipo de núcleo o escolhido foi o tipo E-E.

Figura 7.7 – Núcleo e carretel do tipo E [23].

Onde

é a área da perna central e

é a área da janela do carretel.

A Tabela 7.4 apresenta os parâmetros obtidos para a indutância

. Para a corrente

eficaz e de pico obtidas pelas equações (4.15) e (4.16), foi acrescido um percentual de 20%

para que se possa garantir que o indutor não sature nem se superaqueça em qualquer condição

de carga.

47

Tabela 7.4 – Parâmetro obtidos para a indutância

.

Especificação/Parâmetro

Valor

Indutância

2,24m H

Corrente de Pico (

13 A

Corrente Eficaz (

Indução Magnética Máxima (

4,33 A

)

0,3 T

Densidade de Máxima de Corrente do Cobre (

Permeabilidade Magnética do Ar (

)

)

450 A/cm²

1,257 µH/m

Frequência de Comutação dos Interruptores ( )

30k Hz

Fator de Ocupação na Área da Janela (

0,7 --

)

A primeira etapa do dimensionamento do núcleo de ferrite consiste em calcular a

bitola necessária para conduzir a corrente eficaz demandada pelo FAP, que depende por sua

vez, da máxima densidade de corrente admitida pelo condutor. A expressão (7.1) apresenta o

cálculo da área do condutor

(7.1)

Com o valor obtido em (7.1) é possível associar através de uma tabela de fios

esmaltados uma bitola de 19 AWG, que corresponde a uma área de 0,006527 cm² e um

diâmetro de 0,091 cm.

A utilização de condutores em altas frequências deve levar em conta o efeito pelicular

(skin effect). É sabido que, à medida que a frequência aumenta, a corrente no interior de um

condutor tende a se distribuir pela periferia, ou seja, existe uma maior densidade de corrente

nas bordas e menor na região central. Esse efeito causa uma redução na área efetiva do

condutor. Em outras palavras, o efeito pelicular atua de maneira a limitar a área máxima do

condutor a ser empregado [23].

Segundo BARBI [13], o valor da profundidade de penetração pode ser obtido através

da equação (7.2).

48

(7.2)

√

√

Desta forma o condutor utilizado não deve possuir um diâmetro superior a

seja,

, ou

. De acordo com a tabela de fios esmaltados, para o diâmetro

referido deve-se usar um condutor com bitola de 21 AWG, que possui uma área de 0,004105

cm².

Como o diâmetro do condutor encontrado (0,091 cm) é superior ao limite fixado pelo

efeito pelicular, é necessário associar condutores em paralelo a fim de que se possa conduzir a

corrente sem superaquecimento dos fios condutores. O número de condutores pode ser

encontrado a partir da equação (7.3).

(7.3)

Conforme apresentado por BARBI [13], para a escolha do núcleo de ferrite, deve-se

encontrar o valor do produto das áreas conforme apresentamos na equação (7.4), e encontrar

um fabricante que forneça um modelo maior e próximo ao calculado.

(7.4)

Assim pode-se selecionar o modelo do núcleo de ferrite como sendo NEE-65/33/39

da Thorthon [24].

O entreferro possui uma relutância muito maior que a do núcleo, fazendo com o

valor de L seja inacessível às variações na permeabilidade do núcleo, desta forma, o indutor

pode operar com valores maiores de corrente sem que ocorra saturação do núcleo.

Constatou-se que com um entreferro de aproximadamente 0,8cm, densidade de fluxo

definida como parâmetro de projeto do indutor não deve ultrapassar 0,3T. Desta forma, a

partir da equação (7.5) é possível encontrar o número de espiras necessárias para ser montado

o indutor.

49

√

7.7

√

(7.5)

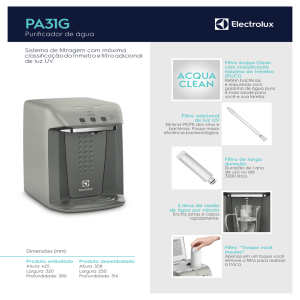

Banco de Capacitores FAP (

De acordo com a equação (4.21), será necessário um banco de capacitores de

1µF. Desta forma, optou-se por utilizar 4 capacitores 150µF/420V da Rubycon [25],

colocados em paralelo (Figura 7.8), alcançando assim um banco de 600µF/420V.

Figura 7.8 – Banco de capacitores 600µF/420V.

7.8

Banco de Capacitores da Carga

De acordo com a equação (4.2), será necessário um banco de capacitores de

Desta forma, optou-se por utilizar 6 capacitores 1000µF/100V da Rubycon [25],

colocados em série dois a dois (Figura 7.9), alcançando assim um banco de 1500µF/200V.

Figura 7.9 - Banco de capacitores 1500µF/200V.

50

7.9

Circuito de Partida Suave (InRush)

Um circuito de partida faz-se necessário para limitar a corrente de pré-carga do

capacitor de barramento do FAP, tendo em vista que este se comporta como um curto-circuito

quando descarregado. Para reduzir este efeito, utiliza-se um resistor de limitação de corrente

de pré-carga (

), que limita o pico da corrente de carga do capacitor. Este resistor deve

ser curto-circuitado quando a tensão dos capacitores atingir aproximadamente 180V (valor de

pico da senoide da rede).

O valor de

é definido de acordo com (7.6).

(7.6)

A corrente de pico (

deve ser estipulada para que não haja danos nos

FETs bem como no indutor de filtragem

. Assim sendo, o resistor

será calculado

para uma corrente máxima de aproximadamente 8A, o que não compromete os componentes

citados.

Logo, utilizando (7.6) teremos que:

(7.7)

Este resistor deve possuir uma capacidade de suportar corrente elevada (resistor de

potência), tendo em vista os níveis de corrente que circularam por ele. Serão utilizados

resistores em paralelo de

, resultando em uma impedância total de

Devido aos níveis de corrente que circularam pelo FAP, para curto-circuitar o

resistor de inrush será utilizado um relé. Foi escolhido o relé SRD-S-12D [26] da Sanyou. As

características deste relé estão apresentadas na Tabela 7.5:

51

Tabela 7.5 - Especificação do relé SRD-S-12D

Especificação

Max Corrente de Chaveamento

Max Tensão de Chaveamento

Tensão Nominal Bobina

Resistência Bobina

Valor

15 A

250 VAC

24 VDC

1600 Ω

FONTE: Datasheet relé SRD-S-12D.

Para realizar o acionamento do relé, foi utilizado um transistor NPN BC548-B [27] e

um transistor PNP BC558 [28], ambos da Fairchild, no modo de saturação. A Figura 7.10

apresenta o diagrama elétrico desenvolvido para o acionamento do relé.

Figura 7.10 – Circuito para acionamento do relé.

7.10

Fonte Auxiliar

Para a alimentação do ARM, drivers e sensor de corrente, foi necessário desenvolver

uma placa com fontes auxiliares, denominada “DC_Power_Supply” (Apêndice E), cuja

função é fornecer tensões de 3,3V, 5V e 24V.

As fontes estão divididas em quatro estágios: transformador abaixador, estágio de