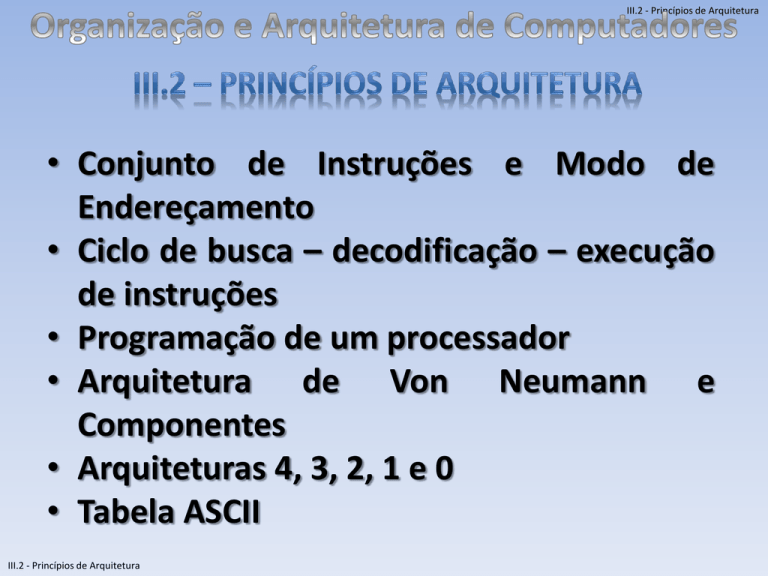

III.2 - Princípios de Arquitetura

• Conjunto de Instruções e Modo de

Endereçamento

• Ciclo de busca – decodificação – execução

de instruções

• Programação de um processador

• Arquitetura de Von Neumann e

Componentes

• Arquiteturas 4, 3, 2, 1 e 0

• Tabela ASCII

III.2 - Princípios de Arquitetura

• Conjunto de Instruções e Modo

de Endereçamento

III.2 - Princípios de Arquitetura

instrução: Conjunto de bits devidamente

codificados que indica ao computador que

sequência de microoperações ele deve

realizar.

Classificação: Semelhança de propósito e

formato. As mais comuns são:

• Transferência de dados

• Aritméticas e lógicas

• Teste de desvio

III.2 - Princípios de Arquitetura

• Conjunto de Instruções e Modo de Endereçamento

III.2 - Princípios de Arquitetura

Conjunto de instruções: é o conjunto de

todas as instruções que um computador

reconhece e pode realizar (equivalente ao

conjunto de palavras reservadas e uma linguagem de

alto nível).

Programa: qualquer sequência finita de

instruções de um determinado conjunto

de instruções.

Modos de endereçamento: são as diversas

forma de endereço de um operando

somadas as diversas formas de desvio.

III.2 - Princípios de Arquitetura

• Ciclo de busca – decodificação –

execução de instruções

III.2 - Princípios de Arquitetura

Busca: Leitura de uma instrução da memória.

Envolve:

• Copiar o apontador de programa (PC) para o

registrador de endereço de memória (REM);

• Leitura de uma instrução da memória (RDM);

• Copiar o registrador de dados da memória

(RDM) para o registrador de instruções (RI);

• Atualizar o apontador (PC).

III.2 - Princípios de Arquitetura

• Ciclo de busca – decodificação – execução de instruções

III.2 - Princípios de Arquitetura

Decodificação: Determinar qual a instrução a

ser executada. A decodificação é feita

geralmente por lógica combinacional.

Execução: Depende de qual instrução a ser

executada.

•

•

•

•

•

•

Cálculo do endereço de operandos

Busca de operandos na memória

Seleção de operação da ULA

Carga de registradores

Escrita de operandos na memória

Atualização do PC para desvios

III.2 - Princípios de Arquitetura

M

0001

R D0000

M

R E0001

0000

PC

0001

0000

III.2 - Princípios de Arquitetura

0001

R 0000

I

N|Z

ULA

A

AC

Unidade de Controle

001110001100101010001

III.2 - Princípios de Arquitetura

B

C

Posição

Conteúdo

0000 0001

0001 0000

0000 0010

0000 1101

0000 0011

0010 0000

0000 0100

0000 1110

0000 0101

0011 0000

0000 0110

0000 1111

0000 0111

1111 0000

0000 1000

0000 0000

0000 1001

0000 0000

0000 1010

0000 0000

0000 1011

0000 0000

0000 1100

0000 0000

0000 1101

0000 0101

0000 1110

0000 0011

0000 1111

0000 0000

5

3

0

• Programação de um processador

III.2 - Princípios de Arquitetura

Linguagem de máquina: É uma imagem

numérica (binária) que representa a

codificação do conjunto de instruções

de um computador.

Programa objeto: São representados

e armazenados em linguagem de

máquina.

III.2 - Princípios de Arquitetura

III.2 - Princípios de Arquitetura

• Programação de um processador

Devido à dificuldade do trabalho com esta

linguagem foram criados:

Mneumônicos associados às instruções:

Nomes dos operandos

Rótulos às posições

programa

ocupadas

pelo

Necessita de Tradução Montagem

Montador: programa que realiza a montagem (Tradutor);

Compilador: gera rotinas em linguagem de máquina para

cada instrução.

III.2 - Princípios de Arquitetura

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

Um Computado de Primeira Geração: O EDVAC

(Eletronic Discrete Variable Computer)

No ENIAC os programas e

armazenados separadamente.

dados

eram

O conceito de programa armazenado é atribuído

ao matemático húngaro John von Neumann

(1903-1957). Isto caracteriza a possibilidade de

mudança das próprias instruções.

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

Arquitetura do EDVAC.

• Programa armazenado

• Memória: 1024 palavras de 44 bits cada,

implementada através de linha de atraso

de mercúrio.

• 20 K palavras de memória secundaria

magnética.

• Representação interna em binário.

• Circuitos aritméticos binários seriais,

devido a entrada de dados serial.

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

...Arquitetura do EDVAC.

Unidade

Central de

Processamento

Unidade

Lógica e

Aritmética

Memória

Principal

Unidade de

Controle de

Programa

III.2 - Princípios de Arquitetura

Unidades de

Memória

Secundárias

Teletipo

Leitora de

cartões

Impressora e

Perfuradora

de Cartões

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

...Arquitetura do EDVAC.

Antes da execução do programa

Colocação de todas as instruções e

dados na memória principal.

Palavras de 44 bits permitem 4 campos

de 10 bits, um campo de 4 bits de

código de instrução.

Capacidade de 16 instruções

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

...Arquitetura do EDVAC.

Exemplo de Instrução Aritmética.

A1 A2 A3 A4 OP

• Executa OP conteúdos em posições cujos

endereços são A1, A2 e coloca o resultado

em A3.

• A4 especifica o endereço da próxima

instrução a ser executada.

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

...Arquitetura do EDVAC.

Exemplo de Instrução Condicional

A1 A2 A3 A4 C

Se o conteúdo de A1 for maior que o

conteúdo de A2 então execute a instrução da

posição A3 se não, da posição A4.

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

...Arquitetura do EDVAC.

Instrução de transferência de memória principal

para secundária.

A1 m,n A3 A4 OP

Significado:

m – modificador de operação

n – endereço do condutor

1. Se m=1 Transfira para o condutor n a sequência de palavras na

memória principal nas posições A1, A1+1, A1+2 .......,A3.

2. Se m=2 Transfira do condutor n a sequência de palavras para as

posições A1, A1+1, A1+2 .......,A3. na memória principal.

A4 endereço da próxima instrução.

Este computador ficou operacional em 1951.

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

...Arquitetura do EDVAC.

Principais Inconvenientes

Tempo de acesso muito longo comparado ao

tempo de processamento da UCP. O que levou a

o chamado “gargalo de von Neumann”.

•Possíveis soluções

Armazenar resultados na posição inicial de

um dos operandos.

Destinar um endereço de memória para

armazenar o resultado de determinada

operação.

Convencionar previamente o endereço da

próxima instrução.

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes

III.2 - Princípios de Arquitetura

Modelo de von Neumann: O computador IAS.

1946 (Princeton Institute for Advanced Studies)

Memória principal: Tubo de raios catódicos de

acesso randômico.

Instrução:

OP A

Arquitetura de um endereço

Blocos básicos

• UCP

• Unidade de controle de programa

• Memória principal de 4096 palavras de 40

bits: grava duas instruções de 20 bits ou

dados de 40 bits

• Unidade de E/S

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes ....O computador IAS

III.2 - Princípios de Arquitetura

AC–Acumulador na UCP –

atua como memória

rápida guardando os

resultados da ULA

MQ–Registrador Multiplicador quociente

DR-Registrador de dados de

40 bits

AR–Registrador de endereço

de 12 bits

IBR–Registra a instrução não

executada

imediatamente

PC – Registrador de endereço

IR–registra a instrução executada imediatamente.

Estrutura do IAS

III.2 - Princípios de Arquitetura

• Arquitetura de Von Neumann e Componentes ....O computador IAS

III.2 - Princípios de Arquitetura

Formato dos Dados

Binário, ponto fixo e complemento 2

01

39

primeiro bit é o de sinal

o ponto está implícito entre 0 e 1

Formato das instruções

0

78

operação

19 20

endereço

39

27 28

operação

endereço

há alterações em relação ao EDVAC

•Registradores pré-definidos na UCP

•Armazenamento sequencial do programa.

III.2 - Princípios de Arquitetura

•Arquiteturas 4, 3, 2, 1 e 0

4 endereços

III.2 - Princípios de Arquitetura

A=((B+C)*D+E-F)/(G*H)

OP E1 E2 E3 E4

E1 – fonte

e1 ADD B C A e2

E2 – fonte

e2 MUL A D A e3

E3 – destino

e3 ADD A E A e4

E4 – próxima inst.

e4 SUB A F A e5

e5 DIV A G A e6

e6 DIV A H A e7

e7 HALT

O quarto endereço é desnecessário pois os

programas eram escritos sequencialmente

III.2 - Princípios de Arquitetura

•Arquiteturas 4, 3, 2, 1 e 0

3 endereços

A=((B+C)*D+E-F)/(G*H)

OP E1 E2 E3

E1 – fonte

E2 – fonte

E3 – destino

e1 ADD B C A

e1+1 MUL A D A

e1+2 ADD A E A

e1+3 SUB A F A

e1+4 DIV A G A

e1+5 DIV A H A

e1+6 HALT

III.2 - Princípios de Arquitetura

III.2 - Princípios de Arquitetura

PC – criado para localizar a

próxima instrução

É necessário Jump–indica salto

Reduz o tamanho

da instrução mas

perde-se um grau

de liberdade

•Arquiteturas 4, 3, 2, 1 e 0

2 endereços

III.2 - Princípios de Arquitetura

A=((B+C)*D+E-F)/(G*H)

OP E1 E2

E1 – fonte/destino

E2 – fonte

e1 MOV A B

e1+1 ADD A C

e1+2 MUL A D

e1+3 ADD A E

e1+4 SUB A F

e1+5 DIV A G

e1+6 DIV A H

e1+7 HALT

III.2 - Princípios de Arquitetura

MOV – movimento de

memória

Evita-se a repetição do

destino.

•Arquiteturas 4, 3, 2, 1 e 0

1 endereços

III.2 - Princípios de Arquitetura

A=((B+C)*D+E-F)/(G*H)

E1 – memória

e1 LDA B

e1+1 ADD C

e1+2 MUL D

e1+3 ADD E

e1+4 SUB F

e1+5 DIV G

e1+6 DIV H

e1+7 STA A

e1+8 HALT

III.2 - Princípios de Arquitetura

OP E1

AC – Acumulador substitui

o fonte e o destino

LDA–move da memória

para o acumulador LoaD

STA–move do acumulador

para a memóriaSTore

Economia de acesso à memória

•Arquiteturas 4, 3, 2, 1 e 0

A=((B+C)*D+E-F)/(G*H)

0 endereços

OP

E1 – memória

Pilha

Equação escrita em

notação polonesa

reversa.

Equação fica:

HGFEDCB+*+-//

e1 PUSH H

e1+1 PUSH G

e1+2 PUSH F

e1+3 PUSH E

e1+4 PUSH D

e1+5 PUSH C

e1+6 PUSH B

III.2 - Princípios de Arquitetura

e1+7 ADD

e1+8 MUL

e1+9 ADD

e1+10 SUB

e1+11 DIV

e1+12 DIV

e1+13 POP A

e1+14 HALT

PUSH – colocar no topo da pilha

POP – enviar do topo da pilha para a memória

III.2 - Princípios de Arquitetura

Não há grande vantagem em relação a anterior

•Tabela Ascii

III.2 - Princípios de Arquitetura

III.2 - Princípios de Arquitetura

III.2 - Princípios de Arquitetura

III.2 - Princípios de Arquitetura