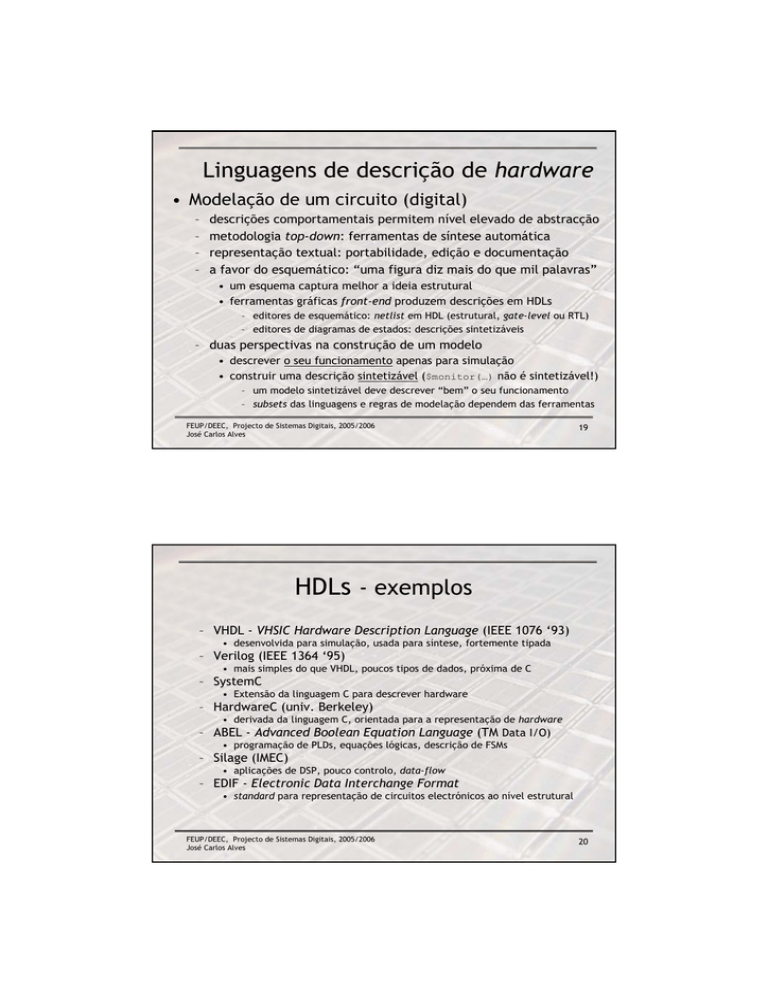

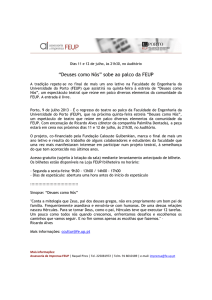

Linguagens de descrição de hardware

• Modelação de um circuito (digital)

–

–

–

–

descrições comportamentais permitem nível elevado de abstracção

metodologia top-down: ferramentas de síntese automática

representação textual: portabilidade, edição e documentação

a favor do esquemático: “uma figura diz mais do que mil palavras”

• um esquema captura melhor a ideia estrutural

• ferramentas gráficas front-end produzem descrições em HDLs

– editores de esquemático: netlist em HDL (estrutural, gate-level ou RTL)

– editores de diagramas de estados: descrições sintetizáveis

– duas perspectivas na construção de um modelo

• descrever o seu funcionamento apenas para simulação

• construir uma descrição sintetizável ($monitor(…) não é sintetizável!)

– um modelo sintetizável deve descrever “bem” o seu funcionamento

– subsets das linguagens e regras de modelação dependem das ferramentas

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

19

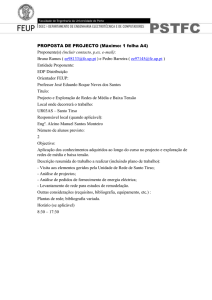

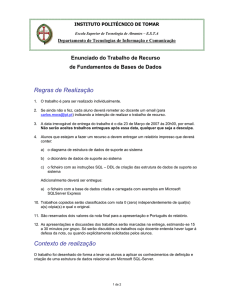

HDLs - exemplos

– VHDL - VHSIC Hardware Description Language (IEEE 1076 ‘93)

• desenvolvida para simulação, usada para síntese, fortemente tipada

– Verilog (IEEE 1364 ‘95)

• mais simples do que VHDL, poucos tipos de dados, próxima de C

– SystemC

• Extensão da linguagem C para descrever hardware

– HardwareC (univ. Berkeley)

• derivada da linguagem C, orientada para a representação de hardware

– ABEL - Advanced Boolean Equation Language (TM Data I/O)

• programação de PLDs, equações lógicas, descrição de FSMs

– Silage (IMEC)

• aplicações de DSP, pouco controlo, data-flow

– EDIF - Electronic Data Interchange Format

• standard para representação de circuitos electrónicos ao nível estrutural

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

20

Verilog vs. VHDL - história

•VHDL

– ‘80: por necessidade de normalização, documentação e portabilidade, e DOD funda

projecto para criar linguagem de “programação” para descrever hardware

– ‘83: início do desenvolvimento do VHDL (IBM, Texas, Intermetrics)

– ‘87: o DOD impõe que todos os SDs fossem descritos em VHDL; standard IEEE 1076;

os sistemas electrónicos do F-22 foram um dos primeiros projectos em VHDL

– ‘93: VHDL é revisto e adoptado como o standard IEEE 1076 ’93

– ‘96: adopção generalizada por ferramentas EDA; package para ferramentas de síntese (IEEE

1076.3); modelação de bibliotecas para ASIC e FPGA (IEEE 1076.4)

•Verilog

–

–

–

–

–

‘81: Gateway Design Automation, Philip Moorby cria GenRad HDL e o simulador HILO

‘83: Gateway lançou a linguagem Verilog HDL e um simulador de Verilog

‘85: linguagem e simulador são enriquecidos (Verilog-XL)

‘87: Synopsys adopta Verilog como formato de entrada para ferramentas de síntese

‘89/’90: Cadence compra Gateway e separa o simulador da linguagem; a linguagem é

libertada para o domínio público; é criado o OVI (Open Verilog International)

– ‘93: neste ano, de todos os circuitos submetidos a fundições de silício, 85% foram

desenvolvidos e submetidos em Verilog.

– ‘95: Verilog é revisto e adoptado como o standard IEEE 1364

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

21

Verilog e VHDL - comparação

• capacidade de modelação

–

–

–

semelhante para modelos estruturais

VHDL oferece melhor suporte para modelos abstractos e modelos de atrasos

Verilog tem melhores construções para modelar ao nível lógico e primitivas

de bibliotecas de ASICs e FPGAs

• tipos de dados

–

–

VHDL suporta tipos de dados abstractos criados pelo utilizador

em Verilog os tipos são muito simples e mais próximos do hw (wire e reg)

• aprendizagem

–

–

VHDL é fortemente tipada, menos intuitiva, mais verbosa (baseada em

ADA)

Verilog é mais simples e menos verbosa (baseada em C)

• parametrização

–

–

VHDL tem construções para parametrizar número de bits, replicar

estruturas e configurar modelos

Verilog suporta apenas modelos com parâmetros, instanciação com

redefinição de parâmetros

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

22

VHDL-Verilog (comportamental)

Verilog

VHDL

library IEEE;

use IEEE.STD_Logic_1164.all;

entity MUX_2_1 is

port(S1,A1,B1,S2,A2,B2,S3,A3,B3:in std_logic;

Y1,Y2,Y3:out std_logic);

end entity MUX_2_1;

module MUX_2_1(S1,A1,B1,Y1,

S2,A2,B2,Y2,

S3,A3,B3,Y3);

input S1,A1,B1,S2,A2,B2,S3,A3,B3;

output Y1,Y2,Y3;

reg Y2,Y3;

architecture COND_DATA_FLOW of MUX_2_1 is

begin

Y1 <= A1 when S1=‘1’ else B1;

TWO_2_1_MUXES:

process(S2,A2,B2,S3,A3,B3)

begin

Y2<=B2;

if (S2=‘1’) then

Y2<=A2;

endif;

if (S3=‘1’) then

Y3<=A3;

else

Y3<=B3;

endif;

end process TWO_2_1_MUXES

end architecture COND_DATA_FLOW;

assign Y1=S1?A1:B1;

always

@(S2 or A2 or B2 or S3 or A3 or B3)

begin

Y2=B2;

if (S2)

Y2=A2;

if (S3)

Y3=A3;

else

Y3=B3;

end

endmodule

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

23

VHDL-Verilog (estrutural)

VHDL

library IEEE;

use IEEE.STD_Logic_1164.all;

entity HALF_ADDER is

port(a,b:in std_logic;

sum,carry:out std_logic);

end entity HALF_ADDER;

Verilog

module HALF_ADDER(a,b,sum,carry);

input a,b;

output sum,carry;

xor X1(sum,a,b);

and A1(carry,a,b);

endmodule

architecture STRUCT of HALF_ADDER is

component xor2

port(a,b:in std_logic; c:out std_logic);

end component;

component and2

port(a,b:in std_logic; c:out std_logic);

end component;

begin

X1: xor2 port map(a=>a,b=>b,c=>sum);

A1: and2 port map(a=>a,b=>b,c=>carry);

end STRUCT;

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

24

Modelação em HDL

• Modelo sintetizável vs. modelo não sintetizável

– ferramentas de síntese automática inferem uma estrutura

• o modelo (comportamental ou estrutural) vai ser hardware

• regras, restrições e recomendações das ferramentas de síntese

– como é interpretado e traduzida a descrição em HDL

– simulação e implementação devem concordar

– construções específicas da tecnologia de implementação

– modelos não sintetizáveis

• não são traduzidos para hardware

• definem estímulos para simulação; monitorização de sinais

• modelam o comportamento de outros circuitos só para simulação

– circuito de relógio

– memórias ou CPUs

– circuitos de interface (por exemplo conversores A/D ou D/A)

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

25

Modelação em HDLs

recomendações gerais

• Antes de iniciar a construção do modelo

– definir a arquitectura e estruturação do projecto (particionamento)

– ferramentas de síntese não processam bem circuitos muito grandes!

• Problemas de optimização são NP-completos

• Escrever o código de modo a reflectir a arquitectura

– estruturado em módulos e funções, ter em mente a reusabilidade

– favorecer a legibilidade: nomes, comentários, parêntesis, parâmetros

• Garantir a precisão da simulação

– deve traduzir fielmente o comportamento do hardware gerado

– modelar correctamente o comportamento das partes não sintetizáveis

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

26

Verilog HDL

(Hardware Description Language)

• Linguagem de descrição de hardware (digital)

–

–

–

–

–

Suporta modelação em diferentes níveis de abstracção

criada para modelação e simulação de circuitos digitais

actualmente usada como fonte para ferramentas de síntese

modelos estruturais e modelos comportamentais

não é uma linguagem de programação!

• Unidade básica de um modelo em Verilog:

– module: um sub-circuito definido por:

• interface (entradas e saídas)

q

preset

clear

qbar

preset

• implementação (modelo do circuito digital)

clear

q

qbar

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

27

Verilog - introdução

• Modelo estrutural de uma latch SR com portas NAND:

atraso

primitiva

module ffnand(preset,clear,q,qbar);

input preset, clear;

output q, qbar;

interface

nand #1 nand1(q, qbar, preset),

nand2(qbar, q, clear);

implementação

instância

endmodule

saída

• Circuito:

preset

clear

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

entradas

q

qbar

28

Verilog - introdução

• Simulação do módulo ffnand

escala temporal

`timescale 1ns/100ps

fios

module top_ffnand;

wire q, qb;

reg pre, clr;

registos

ffnand ffnand1(pre,clr,q,qb);

instância

initial

begin

$monitor($time,

“ preset=%b, clear=%b, q=%b, qbar=%b”,

pre, clr, q, qb);

espera 10ns

#10

#10

#10

#10

#10

pre=0; clr=1;

pre=1;

clr=0;

clr=1;

$finish;

monitor

de sinais

estímulos

de simulação

end

endmodule

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

29

Verilog - introdução

• Modelo completo para simulação (testbench)

– reunião dos módulos ffnand e top_ffnand

• Resultados da simulação

– produzidos pela função $monitor(...)(system task)

• sempre que algum dos sinais declarados muda de estado

– análise das formas de onda de sinais relevantes

0

10

11

12

20

30

31

32

40

preset=x

preset=0

preset=0

preset=0

preset=1

preset=1

preset=1

preset=1

preset=1

clear=x

clear=1

clear=1

clear=1

clear=1

clear=0

clear=0

clear=0

clear=1

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

q=x

q=x

q=1

q=1

q=1

q=1

q=1

q=0

q=0

qbar=x

qbar=x

qbar=x

qbar=0

qbar=0

qbar=0

qbar=1

qbar=1

qbar=1

valor lógico

desconhecido

30

Verilog - introdução

• Um contador de 4 bits (counter)

–

–

–

–

estruturação em 3 módulos: c16, Dff e clockgen

clockgen produz o sinal de relógio

contador c16 usa instâncias do módulo Dff (flip-flops tipo D)

hierarquia do modelo:

counter

c16

Dff

clockgen

Dff

Dff

Dff

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

31

Verilog - introdução

• Modelo do contador c16

module c16(value, clock, fifteen, ten);

input clock;

output [3:0] value;

output fifteen, ten;

Dff

D1(value[0],

D2(value[1],

D3(value[2],

D4(value[3],

clock,

clock,

clock,

clock,

vector de bits

saídas de 1 bit

~value[0]),

value[1] ^ value[0]),

value[2] ^ &value[1:0]),

value[3] ^ &value[2:0]);

assign fifteen = &value;

assign ten = value[3] & ~value[2] & value[1] & ~value[0];

operadores

endmodule

saída ten vale 1 quando value = 1010

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

32

Verilog - introdução

• Modelo (comportamental) do Dff

module Dff(q, clock, d);

input clock, d;

output q;

reg

q;

initial

q = 0;

always

@ (negedge clock)

#10 q = d;

q é reg porque “segura” um valor

no início da simulação (t=0)

sempre que clock

endmodule

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

33

Verilog - introdução

• Gerador de relógio (clockgen)

module clockgen(clock);

output clock;

reg

clock;

initial

#5 clock = 1;

always

#50 clock = ~clock;

para sempre...

sinal clock gerado:

endmodule

t=0

5

unidades de tempo reais: ‘timescale 1ns/100ps

50

50

arredondamento

dos cálculos

unidade de atraso

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

34

Verilog - introdução

• O circuito completo (módulo counter)

module counter;

wire [3:0] count;

wire clock, ten, fifteen;

c16

contador( count, clock, fifteen, ten);

clockgen clock( clock );

initial

$monitor($time, “ Clk=%b, Count=%d, is_10=%b, is_15=%b”,

clock, count, ten, fifteen);

endmodule

FEUP/DEEC, Projecto de Sistemas Digitais, 2005/2006

José Carlos Alves

35