ANGEL MARÍA GÓMEZ ARGÜELLO

ESTUDO E PROJETO DE UM SINTETIZADOR DE FREQÜÊNCIA PARA RF

EM TECNOLOGIA CMOS DE 0,35µm

Dissertação apresentada à Escola

Politécnica da Universidade de São Paulo

para obtenção do Título de Mestre em

Engenharia Elétrica

São Paulo

2004

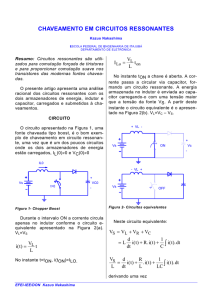

ANGEL MARÍA GÓMEZ ARGÜELLO

ESTUDO E PROJETO DE UM SINTETIZADOR DE FREQÜÊNCIA PARA RF

EM TECNOLOGIA CMOS DE 0,35µm

Dissertação apresentada à Escola

Politécnica da Universidade de São Paulo

para obtenção do Título de Mestre em

Engenharia Elétrica.

Área de concentração:

Microeletrônica.

Orientador:

João Navarro Soares Junior

São Paulo

2004

FICHA CATALOGRÁFICA

Gómez, Argüello Angel María

Estudo e projeto de um sintetizador de freqüência para RF em

tecnologia CMOS de 0,35µm / Angel María Gómez Argüello-- São

Paulo, 2004.

104 p.

Dissertação (Mestrado) – Escola Politécnica da Universidade

de São Paulo. Departamento de Engenharia de Sistemas

Eletrônicos.

1. Microeletrônica 2. Circuitos integrados MOS

3. Telecomunicações (Aplicações) 4. Osciladores I. Universidade

de São Paulo. Escola Politécnica. Departamento de Engenharia

de Sistemas Eletrônicos II.t

A mi madre, Valentina

A mi padre, Angel María

A mi hermano, Milson

A mi novia, Catalina

AGRADECIMENTOS

Agradeço a meu orientador, o Dr. João Navarro Soares Jr., pelos seus valiosos conselhos

durante a elaboração deste trabalho. Também ao professor Wilhelmus A. M. Van Noije.

Agradeço ao Conselho Nacional de Desenvolvimento Científico e Tecnológico (CNPq) que

mediante o Programa de Estudantes-Convênio de Pós-Graduação (PEC/PG), me deu a bolsa para

minha estadia no Brasil. Também à Fundação de Amparo à Pesquisa do Estado de São Paulo

(FAPESP) que financiou a fabricação dos circuitos integrados.

Agradeço ao pessoal do DMPSV, colombianos e brasileiros por sua companhia e ajuda nestes

anos. Ao pessoal do Laboratório de Medidas de Microondas.

Agradeço especialmente a Alfredo e a Rodrigo por terem me ajudado a chegar aqui.

RESUMO

A implementação de um Sintetizador de Freqüência CMOS para RF em 2,4 GHz (faixa ISM –

Industrial, Scientific and Medicine), utilizando uma tecnologia CMOS de 0,35 µm (quatro níveis

de metal e dois níveis de polisilicio) é descrita. O Sintetizador utiliza a arquitetura com PLL tipo

integer-N e permite selecionar entre 16 diferentes freqüências. Os blocos que compõem o circuito

são completamente integrados e incluem: um oscilador controlado por voltagem (VCO), um

divisor de freqüência, um detector de fase e freqüência, uma bomba de carga e um filtro passa

baixos. A maior parte destes blocos têm requerimentos de projeto que devem ser seguidos para

assegurar a correta operação do circuito. Particularmente, o dual-modulus prescaler, um dos

blocos mais exigentes em termos de velocidade e consumo de potência, foi implementado usando

a técnica Extended True Single Phase Clock e, como resultado, se obteve para este bloco altas

freqüências de operação com razoável consumo de potência.

Alem das descrições dos blocos e os layouts, detalhes de alguns problemas do sistema

completo são apresentados e discutidos, como por exemplo: a necessidade de amplificar a saída

do VCO antes de ser aplicada à entrada do prescaler para a correta operação; o ripple gerado na

bomba de carga que corrompe a voltagem de controle do VCO e, em conseqüência, degrada as

características de ruído de fase, etc.

Finalmente, foi fabricado o circuito integrado e elaborados os testes sobre ele, sendo preciso

elaborar uma placa de teste para tal fim.

ABSTRACT

The implementation of a CMOS Frequency Synthesizer for RF in 2.4 GHz (ISM – Industrial,

Scientific and Medicine – band), using 0.35 µm CMOS technology (four metal levels and two

polysilicon levels) is described. The Synthesizer employs the integer-N architecture and PLL, and

it is able to select sixteen different frequencies. The blocks composing the circuit are fully

integrated and they include: a voltage controlled oscillator (VCO), a frequency divider, a phase

frequency detector, a pump charge, and a low pass filter. Most of these blocks have design

requirements that should be followed to assure the circuit correct operation. Particularly, the dualmodulus prescaler, one of the most demanding blocks in terms of speed and power consumption,

was implemented using the Extended True Single Phase Clock Technique, and as result we

obtained for this block high operation frequencies with reasonable power consumption.

In addition to the block descriptions and layouts, details of some system problems were

presented and discussed, as for example: the need of amplifying the VCO output before applying

it in the prescaler input to have the correct operation; the ripple generated in the charge pump that

corrupts the VCO control voltage and, in consequence, degrades the phase noise characteristics,

etc.

Finally, the integrated circuit was fabricated and tested, being necessary to elaborate one test

board for this objective.

SUMÁRIO

1. INTRODUÇÃO........................................................................................................................... 1

1.1. MOTIVAÇÃO...................................................................................................................... 1

1.2. OBJETIVOS......................................................................................................................... 3

1.3. ORGANIZAÇÃO DO DOCUMENTO ............................................................................... 3

2. ASPECTOS TEÓRICOS DO SINTETIZADOR DE FREQÜÊNCIA ....................................... 4

2.1. PLL (PHASE LOCKED LOOP) .......................................................................................... 4

2.2. SINTETIZADOR DE FREQÜÊNCIA PARA RF ............................................................... 5

2.3. ARQUITETURAS PARA SINTETIZADORES DE FREQÜÊNCIA................................. 5

2.3.1. Arquitetura Integer-N .................................................................................................... 5

2.3.2. Arquitetura Fractional-N............................................................................................... 7

2.3.3. Arquitetura Dual-Loop .................................................................................................. 8

2.3.4. Arquitetura de Síntese Digital Direta (DDS)................................................................. 9

2.4. ANÁLISE LINEAR DE SINTETIZADORES COM PLL ................................................ 10

2.5. RUÍDO DE FASE E TONS ESPÚRIOS NA SAÍDA DO SINTETIZADOR ................... 12

2.6. CARACTERÍSTICAS DE RUÍDO DO SINTETIZADOR ............................................... 15

2.7. BLOCOS CONSTRUTIVOS DO SINTETIZADOR DE FREQÜÊNCIA........................ 17

2.7.1. Detector de Fase (PD) ................................................................................................. 17

2.7.1.1. PD analógicos ou Multiplicadores........................................................................ 18

2.7.1.2. Porta OU Exclusiva .............................................................................................. 18

2.7.1.3. Latch ..................................................................................................................... 19

2.7.1.4. Detector de Freqüência e Fase (PFD)................................................................... 19

2.7.2. Bomba de carga e filtro do loop .................................................................................. 21

2.7.3. Osciladores controlados por voltagem ........................................................................ 24

2.7.4. Divisores de freqüência ............................................................................................... 25

2.7.4.1. Contadores ou divisores programáveis................................................................. 26

2.7.4.2. Prescalers ............................................................................................................. 26

3. IMPLEMENTAÇÃO DO CIRCUITO SINTETIZADOR DE FREQÜÊNCIA ....................... 28

3.1. ESPECIFICAÇÕES DO PROJETO................................................................................... 28

3.1.1. Freqüência de saída e resolução .................................................................................. 28

3.1.2. Ruído de fase ............................................................................................................... 28

3.1.3. Nível do tom espúrio na saída do VCO....................................................................... 29

3.1.4. Tempo de comutação................................................................................................... 29

3.2. OSCILADOR CONTROLADO POR VOLTAGEM (VCO) ............................................ 29

3.2.1. Buffer VCO-Prescaler................................................................................................. 34

3.2.2. Layout do buffer VCO-Prescaler ................................................................................. 36

3.2.2. Constante de transferência do VCO ............................................................................ 36

3.3. DIVISOR DE FREQÜÊNCIA ........................................................................................... 37

3.3.1. Prescaler...................................................................................................................... 37

3.3.2. Contador Principal....................................................................................................... 42

3.3.3. Swallow Counter ......................................................................................................... 43

I

3.3.4. Lógica de Controle ...................................................................................................... 43

3.3.5. Layout do divisor de freqüência .................................................................................. 45

3.4. DETECTOR DE FASE E FREQÜÊNCIA ........................................................................ 47

3.4.1. Entrada de clock de referência..................................................................................... 48

3.4.2. Layout do circuito Detector de Fase e Freqüência ...................................................... 49

3.5. BOMBA DE CARGA E FILTRO PASSA BAIXOS ........................................................ 50

3.5.1. Layout da bomba de carga e do filtro passa baixos ..................................................... 53

3.6. CIRCUITO DE TESTE DA SAÍDA DO VCO.................................................................. 55

3.7. RESULTADOS DE SIMULAÇÕES GERAIS.................................................................. 60

3.8. COMPARAÇÃO DESTE TRABALHO COM OUTROS................................................. 63

4. RESULTADOS EXPERIMENTAIS ........................................................................................ 64

4.1. LAYOUT DOS CIRCUITOS INTEGRADOS (C.I.s) UTILIZADOS PARA TESTES ... 64

4.1.1. Versão 1....................................................................................................................... 65

4.1.2. Versão 2....................................................................................................................... 65

4.2. MONTAGEM DO CIRCUITO INTEGRADO PARA TESTE ......................................... 66

4.3. RESULTADOS OBTIDOS NOS TESTES........................................................................ 70

4.3.1. Resposta do VCO ........................................................................................................ 70

4.3.2. Resposta geral do sintetizador de freqüência .............................................................. 72

4.3.2.1. Primeira versão do C.I. ......................................................................................... 72

4.3.3.2. Segunda versão do C.I. ......................................................................................... 73

4.3.3. Consumo de potência do Sintetizador de Freqüência.................................................. 75

4.4.4. Curva Freqüência de Oscilação do VCO versus Voltagem de Controle..................... 75

5. CONCLUSÕES E RECOMENDAÇÕES ................................................................................. 76

APÊNDICE A: PARÂMETROS TÍPICOS DE SIMULAÇÃO (CMOS ELDO BSIM3V3

LEVEL=53) ................................................................................................................................... 79

REFERÊNCIAS BIBLIOGRÁFICAS .......................................................................................... 87

II

Lista de figuras

Figura 1. Transceptor genérico de RF. ............................................................................................ 2

Figura 2. PLL básico. ...................................................................................................................... 4

Figura 3. Arquitetura integer-N. ...................................................................................................... 6

Figura 4. Arquitetura Fractional-N. ................................................................................................ 7

Figura 5. Uso de um dual-modulus prescaler como pulse remover................................................ 8

Figura 6. Arquitetura dual-loop....................................................................................................... 8

Figura 7. Síntese Digital Direta. ...................................................................................................... 9

Figura 8. Modelo linear do sintetizador de freqüência.................................................................. 10

Figura 9. Espectro de saída de: (a) um oscilador ideal; (b) um oscilador real. ............................. 12

Figura 10. Efeito do ruído de fase do LO num receptor; (a) sinal de entrada, (b) espectro do

oscilador e (c), espectro do sinal após passar por mixer........................................................ 13

Figura 11. Efeito do ruído de fase do LO num transmissor. ......................................................... 13

Figura 12. Exemplo do ruído de fase de um oscilador local (para o sistema GSM). .................... 14

Figura 13. Loop de controle utilizado para analisar o ruído num PLL. Neste esquema G(s)

representa a função de transferência do detector de fase, do loop filter e do VCO. ............. 15

Figura 14. Densidade espectral de potência do ruído em um sintetizador de freqüências: (a) ruído

do VCO e seu efeito na saída do sintetizador; (b) ruído da fonte de referência e seu efeito na

saída do sintetizador. ............................................................................................................. 17

Figura 15. (a) Detector de fase XOR; (b) Operação; (c) Curva de transferência do valor médio da

saída. T é o período do sinal A e τ é a diferença de fase entre A e B.................................... 18

Figura 16. (a) Detector de fase tipo latch; (b) Operação; (c) Curva de transferência do valor

médio da saída. ...................................................................................................................... 19

Figura 17. (a) Detector de freqüência e fase; (b) Operação; (c) Curva de transferência do valor

médio da saída. ...................................................................................................................... 20

Figura 18. Característica de transferência do PFD com “zona morta”......................................... 21

Figura 19. Sintetizador com bomba de carga. ............................................................................... 21

Figura 20. Adição de um zero a uma bomba de carga. ................................................................. 22

Figura 21. Adição de C2 no filtro do loop para suprimir o ripple. ................................................ 24

Figura 22. Topologias de osciladores LC: (a) Par cruzado NMOS; (b) Par cruzado CMOS; (c)

Colpitts. ................................................................................................................................. 25

Figura 23. Oscilador em anel......................................................................................................... 25

Figura 24. (a) Divisor de freqüência síncrono; (b) Formas de onda.............................................. 26

Figura 25. (a) Divisor de freqüência assíncrono; (b) Formas de onda. ......................................... 26

Figura 26. Prescaler dual-modulus divisor 4/5. Quando Modo=”1” o prescaler dividirá por 4;

quando Modo=”0” o prescaler dividirá por 5. ..................................................................... 27

Figura 27. Diagrama esquemático do circuito oscilador LC. ........................................................ 30

Figura 28. Modelo tipo π do indutor gerado por ASITIC. ............................................................ 31

Figura 29. Diodos varactores: (a) Esquema elétrico; (b) Estrutura física. .................................... 31

Figura 30. Modelo de um terminal do oscilador. .......................................................................... 32

Figura 31. Circuito para o cálculo da impedância do par cruzado. ............................................... 32

Figura 32. Primeira alternativa de buffer amplificador para ligar o VCO e o prescaler............... 34

Figura 33. Segunda alternativa: Buffer inversor auto polarizado. ................................................. 35

Figura 34. Layout do buffer pré-amplificador auto-polarizado. (dimensôes: 85µm x 180µm)..... 36

III

Figura 35. Resultado da simulação do VCO: Freqüência de oscilação vs. Voltagem de controle.

ELDO 5.6 Modelo MOS BSIM3v3 e parâmetros típicos (Vide Apéndice A)...................... 37

Figura 36. Diagrama esquemático do Dual-Modulus Prescaler (divisor por 32/33).................... 38

Figura 37. (a) Diagrama de transição, e (b) diagrama de tempo do contador divisor-por-4/5

síncrono. ................................................................................................................................ 39

Figura 38. (a) Esquemático dos transistores do D-FF básico configurado como contador divisorpor-2, com dimensões em µm, e (b) diagrama de tempos..................................................... 40

Figura 39. Resultados da simulação para o D-FF básico. O ELDO 5.6, modelo do transistor

BSIM3v3 e parâmetros típicos foram usados. O D-FF atingiu uma freqüência máxima de

2,75 GHz................................................................................................................................ 40

Figura 40. Esquemático do prescaler. O esquema detalhado dos transistores da parte síncrona ,de

um D-FF da parte assíncrona e da porta NAND são mostrados (a largura de canal do

transistor ou, quando o comprimento é diferente de 0,35 µm, a relação largura/comprimento

de canal em µm também é indicado). Comparar com a Figura 36. ....................................... 41

Figura 41. Simulação do divisor por 4/5 (ELDO 5.6, modelo do transistor BSIM3v3, parâmetros

típicos). .................................................................................................................................. 42

Figura 42. Simulação do contador divisor-por-8 assíncrono (ELDO 5.6, modelo do transistor

BSIM3v3, parâmetros típicos). O sinal sm=”alto”. ............................................................. 42

Figura 43. Contador Principal. ...................................................................................................... 43

Figura 44. Esquema do Swallow Counter. .................................................................................... 43

Figura 45. Esquema da lógica de controle..................................................................................... 44

Figura 46. Simulação dos sinais da lógica de controle (ELDO 5.6, modelo do transistor

BSIM3v3, parâmetros típicos)............................................................................................... 45

Figura 47. Layout do divisor de freqüência (dimensões: 200µm x 30µm).................................... 45

Figura 48. Layout do prescaler (dimensões: 70µm x 30µm). ....................................................... 46

Figura 49. Layout do (a) Contador Principal (dimensões: 15µm x 30µm), (b) Multiplexor

(dimensões: 15µm x 15µm), e (c) Porta lógica OR de 4 entradas (dimensões: 15µm x 15µm).

............................................................................................................................................... 46

Figura 50. Layout do Swallow Counter (dimensões: 85µm x 30µm)............................................ 47

Figura 51. Detector de Fase e Freqüência convencional. .............................................................. 47

Figura 52. (a) D-FF Svenson Original, (b) Esquema do circuito D-FF modificado para o detector

de fase e freqüência. .............................................................................................................. 48

Figura 53. (a) Esquema elétrico do Detector de Fase e Freqüência (PFD), (b) Simulação postlayout do PFD, (c) Detalhe do atraso entre a aparição de up e dn e a geração do sinal de reset

(só se mostra dn por claridade).............................................................................................. 49

Figura 54. Layout do circuito detector de fase e freqüência (dimensões: 50µm x 25µm). ........... 50

Figura 55. Esquema da bomba de carga básica (as dimensões dos transistores em µm também

estão indicadas). .................................................................................................................... 51

Figura 56. Esquema da bomba de carga melhorada (as dimensões dos transistores em µm também

estão indicadas). .................................................................................................................... 53

Figura 57. Esquema do amplificador OTA (as dimensões dos transistores em µm também estão

indicadas)............................................................................................................................... 53

Figura 58. Layout da bomba de carga e o filtro passa baixos (dimensões: 300µm x 280µm). ..... 54

Figura 59. Layout das fontes de corrente junto com as chaves e o amplificador (bomba de

carga)(dimensões: 90µm x 85µm). ........................................................................................ 55

Figura 60. Buffer tipo seguidor de fonte........................................................................................ 56

IV

Figura 61. Esquema elétrico do buffer para teste (as dimensões dos transistores em µm também

estão indicadas). .................................................................................................................... 56

Figura 62. Layout do sintetizador de freqüência sem incluir o VCO (dimensões: 375µm x

355µm)................................................................................................................................... 58

Figura 63. Layout do chip sintetizador completo (dimensões:1450µm x 1145µm). ..................... 59

Figura 64. Simulação da resposta da voltagem de controle contra o tempo, para medir o tempo de

comutação do sintetizador de freqüência (ELDO 5.6 Modelo MOS BSIM3v3 e parâmetros

típicos). .................................................................................................................................. 60

Figura 65. Simulação do sintetizador com diversos fatores de divisão: 515, 525, 524 e 520. (a)

mostra o sinal de controle do VCO; (b) saída do oscilador; (c) entrada do buffer VCOPrescaler; (d) saída do buffer VCO-Prescaler (ELDO 5.6 Modelo MOS BSIM3v3 e

parâmetros típicos). ............................................................................................................... 61

Figura 66. Buffer VCO-Prescaler. Mostram-se os sinais simulados e apresentados na Figura 65.61

Figura 67. Simulação de ruído de fase do sintetizador de freqüência para 2,4 GHz: -126 dBc/Hz

@ 3 MHz. (ELDO 5.6 Modelo MOS BSIM3v3, parâmetros típicos)................................... 62

Figura 68. Primeira versão do circuito integrado enviado para fabricação. O sintetizador está

localizado na porção inferior direita do C.I........................................................................... 65

Figura 69. Segunda versão do circuito integrado enviado para fabricação. O sintetizador está

localizado na porção inferior direita do C.I........................................................................... 65

Figura 70. Montagem para o teste do circuito integrado............................................................... 66

Figura 71. Montagem do C.I., das pontas secas e da ponta cascade GSG. ................................... 67

Figura 72. Primeira versão da placa de teste para a primeira versão do C.I.................................. 69

Figura 73. Segunda versão das placas de teste. a) placa para a primeira versão do C.I.; b) placa

para a segunda versão do C.I. ................................................................................................ 69

Figura 74. a) Fotografia da placa de teste e do C.I. (segunda versão); b) detalhe do C.I., microsoldas e trilhas de ouro; c) microfotografia do Circuito Sintetizador de Freqüências. ......... 70

Figura 75. Saída do VCO no analisador de espectro (IOSC=2,7mA, SPAN=400 MHz, RBW=1,0

MHz). Resultados obtidos com a primeira versão do C.I. e com a segunda placa................ 71

Figura 76. Saída do VCO no analisador de espectro (IOSC=2 mA, SPAN=25 MHz, RBW=300

KHz). Resultados obtidos com a primeira versão do C.I. e com a segunda placa. ............... 71

Figura 77. Curva caracterítica típica de um inversor CMOS. ....................................................... 72

Figura 78. Saída do divisor obtida no pad VFB. ............................................................................. 73

Figura 79. Saída do divisor de freqüência (acima) e entrada do sinal de referência (abaixo) para 4

MHz (a) e 4.5 MHz (b).......................................................................................................... 74

Figura 80. Saída do VCO para: fref=4 MHz. a) N=512; b) N=527. Span= 1 GHz. ....................... 74

Figura 81. Saída do VCO para: fref=4,5 MHz. N=512. Span=10 MHz. Sespúrio{4,5 MHz} ≈ -20 dBc

> -61 dBc (da especificação). ............................................................................................... 75

Figura 82. Comparação dos resultados experimentais e simulados da Freqüência de Oscilação

versus Voltagem de Controle do VCO. ................................................................................. 75

Figura 83. Oscilador LC com topologia complementar. ............................................................... 77

V

Lista de tabelas

Tabela 1. Bandas de freqüência de padrões de telefonia sem fio e celular. .................................... 5

Tabela 2. Especificações de Sinais Bloqueadores (Bluetooth [26]) .............................................. 29

Tabela 3. Resumo das características do Sintetizador projetado (simulação) comparado com

outros trabalhos desenvolvidos em tecnologia CMOS.......................................................... 63

Tabela 4. Equipamento utilizado para o teste do circuito integrado. ............................................ 67

Tabela 5. Valores iniciais de correntes e tensões para o teste do circuito integrado..................... 68

VI

Lista de símbolos

/lo

∆ø

∆P

∆ω

1/f

1/Tp

A

A(t)

A1

A2

Ad

BW

ck

ckassyncr

ckin

ckn16

ckn32

ckn8

div8

Dn

dn2

f

F(s)

fLO

fosc

fref

fref1

fref2

G(s)

H(s)

I

IA,IB,IC,ID

IC

IF

KF

Klf

KPD

KPFD

KVCO

L{∆ω}

M

N

N(s)

ndn

ndn2

nup

nup2

out32/33

Sinal de controle do swallow counter

Diferenca de fase detectada no detector de fase num PLL

Valor do incremento no acumulador do sintetizador de síntese digital direta

Offset de freqüência ao redor da freqüência central de um oscilador real (rad/seg)

Variação do ruído de fase para offsets pequenos ao redor da freqüência central

Freqüência do comando remove na arquitetura Fractional-N

Amplitude de oscilação de um oscilador ideal (V)

Amplitude de oscilação de um oscilador real (V)

Amplitude de oscilação de um sinal 1

Amplitude de oscilação de um sinal 2

Amplitude de oscilação do sinal de saída de um multiplicador

Bandwith

Sinal de relógio do acumulador do sintetizador de síntese digital direta

Entrada de clock do divisor assíncrono

Sinal de clock do divisor síncrono do dual modulus prescaler

Saída do segundo flip-flop do divisor assíncrono do dual-modulus prescaler

Saída do terceiro flip-flop do divisor assíncrono do dual-modulus prescaler

Saída do primeiro flip-flop do divisor assíncrono do dual-modulus prescaler

Sinal de controle do divisor 4/5 do dual modulus prescaler

Sinal de controle da fonte de corrente inferior da bomba de carga

Sinal ndn negado

Freqüência (Hz)

Função de transferência do loop filter do sintetizador

Freqüência central de oscilação de um oscilador local (LO)

Freqüência de saída do sintetizador de freqüência (Hz)

Freqüência de entrada do sintetizador de freqüência (Hz)

Freqüência de referência do PLL1 (arquitetura dual-loop)

Freqüência de referência do PLL2 (arquitetura dual-loop)

Ganho do detector de fase usado para simular os comportamentos de ruído de fase do

sintetizador

Função de transferência de loop fechado do sintetizador

Componente em fase da saída do VCO (arquitetura dual-loop)

Dados digitais de entrada do swallow counter

Corrente de carga ou descarga do nó de controle do VCO

Freqüência intermediária

Forward Gain do PLL

Ganho constante do filtro

Ganho do detector de fase

Ganho do detector de fase e freqüência

Ganho do VCO do sintetizador

Densidade unilateral de ruído espectral [dBc/Hz]

Fator de divisão do sintetizador PLL1 na arquitetura dual-loop

Fator de divisão geral do sintetizador de freqüência (arquitetura Integer-N) e do PLL2 na

arquitetura dual-loop

Função de transferência do divisor de freqüência do sintetizador

Sinal dn negado

Sinal dn2 negado

Sinal up negada

Sinal up2 negado

Saída do dual modulus prescaler

VII

P

Q

QA,QB,QC,QD

RF

S

s

sm

SNR

t

T

t

Tp

Up

up2

V

vc

vd

ve

Vfb

Vout(t)

Vref

wc

x(t)

y(t)

ζ

θ

θ(t)

θ1

θ2

θe

θfb

θnref

θnvco

θout

θref

Σ

ω

ω1

ω2

ωLO

ωn

Valor fixo no contador principal

Componente em quadratura da saída do VCO (arquitetura dual-loop)

Dados digitais de saída do swallow counter

Radio Freqüência

Valor programável do swallow counter

Freqüência complexa para análise de freqüência (Transformada de Laplace)

Signal modulus (Seleciona se o dual modulus prescaler divide por V ou por V+1)

Signal Noise Ratio

Variável independente de tempo

Período do sinal de entrada num detector de fase

Diferença de fase entre os dois sinais de um detector de fase

Período do comando remove na arquitetura Fractional-N

Sinal de controle da fonte de corrente superior da bomba de carga

Sinal nup negado

Valor nominal do dual-modulus prescaler

Tensão de controle do VCO (ve, depois de pasar pelo filtro do loop)

Sinal de saída de um multiplicador

Erro de fase expressado como um valor de voltagem

Sinal de saída do divisor de freqüência do sintetizador

Voltagem de saída de um oscilador ideal (V)

Sinal de referência do sintetizador de freqüência

Freqüência de cross-over do sintetizador

Sinal de referencia do PLL

Sinal de saída do PLL

Fator de amortecimento do PLL

Referência de fase arbitrária para um oscilador ideal

Referência de fase arbitrária de um oscilador real

Fase de referência arbitrária de um sinal 1

Fase de referência arbitrária de um sinal 2

Erro de fase = θref - θfb

Fase do sinal de saída do divisor do sintetizador de freqüência

Ruído de fase do sinal de referência

Ruído de fase gerado dentro do próprio VCO

Fase do sinal de saída do VCO do sintetizador de freqüência

Fase do sinal de referência do sintetizador de freqüência

Somatória

Freqüência angular (rad/seg)

Freqüência central de um sinal 1 [rad/seg]

Freqüência central de um sinal 2 [rad/seg]

Freqüência de saída de um oscilador ideal (rad/seg)

Freqüência natural do PLL

VIII

1. INTRODUÇÃO

1.1. MOTIVAÇÃO

A área das telecomunicações tem avançado muito nos últimos anos devido, em parte, à

miniaturização dos componentes eletrônicos utilizados. Destes componentes, aqueles destinados

à área da Radio Freqüência (RF) também têm evoluído muito. Graças a esta miniaturização é

cada vez maior o número de usuários finais que podem fazer uso de produtos com comunicação

RF, principalmente portáteis. Outros fatores, tais como baixo peso, consumo de potência e custo,

influenciam este aumento.

Os circuitos transceptores (transmissor e receptor num circuito único) de RF eram,

inicialmente, implementados por meio de componentes discretos, passaram, posteriormente, a ser

implementados com diversos circuitos integrados e alguns componentes externos e, agora, são

desenvolvidos com no máximo dois circuitos integrados (um para a parte analógica e outro para a

parte digital) mais componentes externos [1]. A tendência futura é implementar tais circuitos em

um único circuito integrado (C.I.) que também inclui os componentes externos.

Antigamente as tecnologias mais usadas para implementar circuitos RF de alta velocidade

eram as tecnologias Bipolar e GaAs; atualmente a tecnologia CMOS (Complementary Metal

Oxide Silicon) começa a ser utilizada neste tipo de aplicação, com vantagens como menor custo,

menor dissipação de potência e, principalmente, alto nível de integração que permite a integração

completa de transceptores e mesmo blocos digitais para tratamento de informações

Um exemplo simplificado do chamado circuito front-end de um transceptor de RF é

apresentado na Figura 1. O circuito front-end é responsável pela translação do sinal recebido para

baixas freqüências e do sinal transmitido para altas freqüências, fazendo os devidos ajustes nos

níveis de potência. Os blocos básicos aqui são o amplificador de baixo ruído (LNA, Low Noise

Amplifier), que amplifica o sinal de entrada, o misturador (mixer), que faz uma multiplicação e

1

desloca um sinal para altas, upconverter, ou para baixas freqüências, downconverter,

o

amplificador de potência, power amplifier, que fornece à saída a potência necessária para

transmissão do sinal, e o sintetizador de freqüências.

O sintetizador de freqüências serve para definir a freqüência central de operação do canal do

usuário tanto no caminho de recepção como no caminho de transmissão. Seu projeto é exigente

pois ele é composto por diversos blocos, alguns operando a alta velocidade, outros sensíveis a

qualquer fonte de ruído externa, que ainda são fontes potenciais de ruído para o resto do

transceptor. Há no sintetizador blocos analógicos, tais como o oscilador, fontes de corrente e

filtros, e blocos digitais tais com o divisor de freqüência, flip-flops, estáticos e dinâmicos, e

diferentes portas lógicas. Observemos que o sintetizador de freqüência é um circuito ideal para

testar a funcionalidade da tecnologia CMOS na integração de blocos analógicos junto com blocos

digitais, pois possui ambos os blocos.

Low-Noise

Amplifier

downconversion

Sinais

recebidos

Filtro

Passa-Banda

Filtro

Duplexor

Sintetizador de

Freqüência

Power

Amplifier

LO

Filtro

Passa-Banda

Sinais

transmitidos

upconversion

Figura 1. Transceptor genérico de RF.

O circuito Sintetizador de Freqüências na tecnologia CMOS é objeto deste documento e este

deverá fazer parte de um circuito transceptor completo que vem sendo desenvolvido dentro do

grupo Divisão de Métodos de Projeto de Sistemas VLSI (DMPSV) da Escola Politécnica da

Universidade de São Paulo, que vem pesquisando aplicações de circuitos integrados,

particularmente na área de RF. Cada um dos outros blocos do transceptor está sendo

desenvolvido separadamente e, depois de se ter um maior conhecimento sobre eles, será

implementado um sistema completo. Atualmente os protótipos têm sido implementados na

2

tecnologia CMOS 0,35 µm da foundry AMS [2], [3], com quatro camadas de metal e duas de

silício policristalino.

Com o fim de ter um conhecimento particular sobre o circuito sintetizador se decidiu

implementar um protótipo numa das bandas ISM [4] (Industrial, Scientific and Medicine: faixas

de uso livre), a de 2,4 GHz a 2,5 GHz, e com freqüências sintetizadas com espaçamento de 4 a 5

MHz. O objetivo deste trabalho, portanto, não está preso a um padrão comercial específico, o que

permite maior liberdade e possibilidades de experimentação.

1.2. OBJETIVOS

•

Projetar um sintetizador de freqüência em tecnologia CMOS para trabalhar a 2,4 GHz;

•

Realizar o layout do sintetizador utilizando uma tecnologia CMOS de 0,35 µm, quatro

camadas de metais e duas camadas de silício policristalino [2], [3] (ferramenta para projeto da

MENTOR GRAPHICS)

•

Simular o comportamento elétrico do circuito (MENTOR-ELDO);

•

Fabricar e fazer testes experimentais sobre o circuito integrado (CI).

1.3. ORGANIZAÇÃO DO DOCUMENTO

Este documento foi divido em cinco capítulos da seguinte forma: no primeiro capítulo será

apresentada a introdução deste trabalho; no segundo capítulo se tratará dos aspectos teóricos a ter

em conta para projetar o sintetizador de freqüência; no terceiro capítulo se detalhará o trabalho

realizado em sua fase de projeto, simulação e layout; no quarto capítulo se expõe o referente aos

testes sobre o circuito fabricado; no quinto capítulo se apresentam as conclusões obtidas e se

fazem recomendações para novos projetos.

3

2. ASPECTOS TEÓRICOS DO SINTETIZADOR DE FREQÜÊNCIA

2.1. PLL (PHASE LOCKED LOOP)

Um PLL é um circuito onde um sistema em particular segue outro. Mais especificamente, é

um circuito que sincroniza um sinal (saída), gerado por um oscilador, com um sinal de referência

(entrada), tanto em freqüência como em fase. No estado sincronizado (chamado locked), o erro de

fase entre o sinal de saída do oscilador e o sinal de referência é igual ou muito próximo de zero

[5].

Um PLL básico (ver Figura 2) consta de um detector de fase (PD), um filtro passa-baixos

(LPF) e um oscilador controlado por voltagem (VCO).

x(t)

Detector de

Fase (PD)

∆ø

Filtro PassaBaixos (LPF)

VCO

y(t)

Figura 2. PLL básico.

Na condição locked o PLL operará da seguinte forma: o PD serve como amplificador da

diferença de fase entre os sinais x(t) de entrada e y(t) de saída, ∆ø ou erro no loop de retroalimentação, e produz uma saída cujo valor em DC é proporcional a ∆ø. O filtro passa-baixos

suprime componentes de alta freqüência da saída do PD, permitindo que seu valor DC controle a

freqüência do VCO. O VCO então oscila com uma freqüência igual à freqüência do sinal de

entrada e com uma diferença de fase igual a ∆ø. Como resultado da operação dos blocos, ∆ø

ficará constante no tempo e as freqüências dos sinais de entrada e de saída serão iguais.

4

2.2. SINTETIZADOR DE FREQÜÊNCIA PARA RF

Como pode ser visto na Figura 1, que apresenta o esquema básico de um receptor/transmissor

(transceptor) genérico, o sintetizador de freqüência gera os sinais periódicos requeridos pelo

mixer para transladar o sinal transmitido para alta freqüência (upconversion), ou transladar o sinal

recebido para baixa freqüência (downconversion). O sintetizador apresenta internamente um PLL

o que permite que sinais com freqüências muito bem definidas sejam produzidos, uma

característica importante para muitas aplicações (para GSM a freqüência do sinal deve variar em

menos de 0,1 ppm enquanto para DECT, menos de 25 ppm) [6].

Além de bem definida, a freqüência do sintetizador deve poder ser ajustada em intervalos

pequenos e precisos para sintonizar canais diferentes de uma banda de recepção/transmissão. Na

Tabela 1 estão mostradas as bandas de recepção/transmissão de alguns padrões de telefonia sem

fio e celular além da largura dos respectivos canais [6].

Tabela 1. Bandas de freqüência de padrões de telefonia sem fio e celular.

Padrão

Banda TX

Banda RX

Largura do Canal BW

IS-54

824-849 MHz

869-894 MHz

30 KHz

IS-95

824-849 MHz

869-894 MHz

1.25 MHz

GSM

890-915 MHz

935-960 MHz

200 KHz

DECT

1.88-1.9 GHz

1.88-1.9 GHz

1.728 MHz

2.3. ARQUITETURAS PARA SINTETIZADORES DE FREQÜÊNCIA

2.3.1. Arquitetura Integer-N

Um PLL incorporando um divisor programável no caminho de retro-alimentação pode operar

como um sintetizador. A arquitetura integer-N é mostrada na Figura 3 e utiliza um divisor do tipo

pulse swallow na retro-alimentação. Este divisor consiste de um dual-modulus prescaler, um

swallow counter programável e um contador principal.

5

Sinal de referência

fref

VCO

LPF

PD

Sinal de saída

fosc

÷N

N=VP+S

Contador Principal

Prescaler

÷P

÷(V+1)/ ÷V

÷S

Modulus

Control

Swallow

Counter

Divisor pulse swallow

Channel

Select

Figura 3. Arquitetura integer-N.

O funcionamento deste sintetizador é descrito a seguir: inicialmente os dois contadores, o

contador principal e o swallow counter, são carregados com os valores iniciais P e S

respectivamente, onde S ≤ P, e o sinal Modulus Control é alto, fazendo o prescaler dividir por

(V+1). Nesta situação o contador principal e o swallow counter recebem como clock o sinal de

saída do VCO dividido por (V+1), e são decrescidos até que o swallow counter chegue a zero,

alterando o sinal Modulus Control. O prescaler então passa a dividir por V, o contador principal

recebe como clock a saída do VCO dividido por V e é decrescido até chegar também à zero.

Neste instante ambos contadores sofrem o reset e o processo recomeça. Deste modo o prescaler

divide o sinal de saída do VCO por (V+1) por S vezes, e divide por V por (P-S) vezes. O fator de

divisão total do divisor pulse swallow será N = (V+1)S +V(P-S) = VP + S. Assim, quando o

sintetizador estiver locked, sua freqüência de saída fosc será:

fosc= N fref =(VP + S)fref.

onde fref é a freqüência do sinal de referência.

Desta forma, programando o valor S podemos controlar a freqüência de saída do sintetizador.

Por sua simplicidade esta arquitetura é bastante popular, embora tenha algumas desvantagens

[6], tais como:

• a freqüência de referência nesta arquitetura deve ser igual ao espaçamento entre os canais

que se deseja sintonizar. Como a largura de banda do loop deve ser normalmente inferior a

6

fref /10, devido a considerações de estabilidade [7], podemos ter um tempo de comutação

entre canais muito longo;

• o loop não suprime o ruído de fase do VCO para offsets de freqüência maiores que

aproximadamente fref /10 [1], o que pode ser ruim já que o ruído 1/f do oscilador é bastante

significativo em offsets de algumas centenas de KiloHertz;

• a freqüência máxima do sistema pode ser limitada pela velocidade do dual-modulus

prescaler que tem que operar com a mesma freqüência do VCO.

2.3.2. Arquitetura Fractional-N

Na topologia fractional-N (Figura 4) um divisor por N e um pulse remover, um circuito que

bloqueia um pulso de entrada depois de receber um comando específico, aparecem na retroalimentação.

fref

PD

LPF

÷N

Y

fosc

VCO

Pulse

Remover

X

Remove

VX

VY

t

Figura 4. Arquitetura Fractional-N.

O funcionamento do sintetizador é descrito a seguir: o circuito pulse remover recebe um

comando de remove na freqüência 1/Tp. Quando o sintetizador estiver locked, a saída do pulse

remover tem uma freqüência média igual a Nfref e o sinal de saída tem fosc = Nfref + 1/TP.

Podemos, portanto, controlar a freqüência de saída através do período TP que é gerado a partir de

um circuito de controle. Veja que nesta arquitetura fref não depende da largura do canal e pode

estar na faixa de dezenas de megahertz. Com isto a largura de banda do loop pode ser de alguns

MegaHertz, originando um transiente de estabilização menor, assim como suprimindo maior

ruído de fase do VCO. Na prática, o pulse remover é construído junto com o divisor.

7

Na Figura 5, se ilustra como implementar esta arquitetura mediante um contador dualmodulus. Se a saída do VCO é dividida por V durante algum tempo e (V+1) durante outro tempo,

o fator de divisão médio pode ser estabelecido entre V e (V+1).

fREF

PD

fout

VCO

LPF

÷V/(V+1)

Modulus Control

Figura 5. Uso de um dual-modulus prescaler como pulse remover.

A principal desvantagem associada com sintetizadores de freqüência fractional-N é a

existência de espúrios fracionais na saída do VCO devido a manipulações dos sinais no tempo

por parte do dual-modulus. Estes espúrios podem ser compensados usando varias técnicas:

compensação análoga DAC, compensação digital usando DSP, etc. ([8], [9], [10], [11]).

2.3.3. Arquitetura Dual-Loop

A relação entre o espaçamento entre canais e a freqüência de referência dos sintetizadores

integer-N pode ser também alterada utilizando dois ou mais loops. Uma forma simples de gerar

passos finos de freqüência é utilizar um sintetizador de freqüência baixa e variável e outro de

freqüência alta, porém fixa [12] (Figura 6).

fref1

I

PD

LPF

VCO

Q

PLL1

fref2

fosc

÷M

I

PD

LPF

VCO

Q

SSB Mixer

÷N

PLL2

Channel

Select

Figura 6. Arquitetura dual-loop.

8

Nesta técnica utiliza-se o PLL1 para gerar a freqüência de portadora e o PLL2 para produzir

incrementos iguais a fref2. Variando o fator de divisão de PLL2, originam-se os passos finos

requeridos na freqüência de saída. A soma das duas freqüências é realizada por meio de um

single-sideband (SSB) mixer.

A principal vantagem desta arquitetura sobre a topologia integer-N é que a largura de banda

do PLL1 pode ser maior diminuindo o ruído de fase na saída do VCO1. O ruído de fase na saída

do VCO2 é muito menor devido a menor freqüência central [13]. A maior desvantagem aqui é

que se devem gerar fases em quadratura bastante precisas, em ambos PLLs, para conseguir um

bom funcionamento dos mixers. Além disso deve-se ter bons casamentos e linearidades nestes

mixers. Em vista disto é difícil garantir que bandas laterais, produzidas por problemas de

quadratura, casamento e linearidade, estejam entre 60 e 70 dB abaixo da portadora (valores

normalmente desejáveis) [7].

2.3.4. Arquitetura de Síntese Digital Direta (DDS)

Aqui o sinal desejado é produzido no domínio digital e utilizam-se conversores

digitais/analógicos e filtros para construir a forma de onda no domínio analógico. Como se ilustra

na Figura 7, a DDS utiliza um acumulador, uma memória só-de-leitura, ROM look-up, um

conversor digital/analógico e um filtro passa baixos. Uma boa referência sobre este tema se

encontra em [14].

Acumulador

∆P

CK

Adder

t

Register

ROM

DAC

LPF

t

t

Figura 7. Síntese Digital Direta.

9

O acumulador gera a rampa digital que é mapeada numa senóide pela ROM. Quando o valor

do incremento, ∆P, cresce, também aumenta a taxa com que o acumulador percorre a memória

ROM e, portanto, a senóide apresenta um período menor.

O DDS oferece varias vantagens sobre as arquiteturas com PLL: menor ruído de fase, passos

de freqüência mais finos e maior velocidade de mudança entre canais. Por outro lado, aspectos de

velocidade, tanto de conversores como de memória, têm limitado seu uso na faixa de RF.

2.4. ANÁLISE LINEAR DE SINTETIZADORES COM PLL

Embora um PLL seja um sistema altamente não-linear, ele pode ser descrito com um modelo

linear se está no estado locked e, neste caso, os sinais de saída e de referência têm a mesma

freqüência (Figura 2). Um sintetizador usando PLL pode ser representado pelo circuito da Figura

8 que apresenta um bloco divisor na realimentação. O modelo da Figura 8 servirá de base para a

análise linear desenvolvida aqui. O sintetizador será considerado estando no estado locked e,

neste caso, o sinal de saída do sintetizador tem a freqüência N vezes maior do que aquela do sinal

de referência.

Detector de fase

θref

+

Σ

θe

ve

KPD

VCO

Loop Filter

F(s)

vc

KVCO/s

θout

θfb

1/N

Divisor de loop

Figura 8. Modelo linear do sintetizador de freqüência.

Será procurada a função de transferencia do sintetizador:

H(s) = θout(s) / θref(s)

onde θout(s) é a fase do sinal de saída e θref (s) é a fase do sinal de referência.

O detector de fase obtém a diferença entre a fase do sinal de referência, θref(s), e a fase de

retro-alimentação, θfb(s), para obter o erro de fase θe(s). Esta diferença é amplificada com um

ganho KPD, para produzir uma voltagem de erro, Ve(s), igual a

Ve(s) = KPD[θref(s)- θfb(s)] = KPD θe(s).

10

Este erro de voltagem é filtrado pelo loop filter para produzir a voltagem de controle do VCO

que é igual a

Vc(s) = Ve(s)F(s)

onde F(s) é a função de transferência do loop filter.

A freqüência do sinal de saída do VCO será dado pelo produto

fosc(s)=Vc(s)KVCO

onde KVCO é um fator de ganho.

O VCO pode ser modelado como um integrador, onde a fase de saída, θout(s), é igual à integral

da freqüência, ou

θ

out

(s) =

Vc(s) KVCO

s

O sinal fase de saída é retro-alimentado e passa através do divisor do loop onde é dividido por

um fator N para gerar a fase de retro-alimentação igual a

θ fb ( s) =

θ out ( s)

N

A função de transferência do sintetizador, H(s), será então igual a

H ( s) =

θ out ( s)

K PD KVCO F ( s)

=

θ ref ( s ) s + K PD KVCO F ( s)

(1)

N

A função de transferência do erro de fase é igual, por sua vez, a

s

θ e (s)

=

K

K

θ ref ( s) s + PD VCO F ( s )

(2)

N

A função de transferência do sintetizador tem uma característica passa-baixos com um ganho

N. Isto significa que para variações lentas (baixa freqüência) na fase de referência, o loop seguirá

o sinal de entrada e produzirá uma fase de saída que é N vezes maior do que a fase de referência.

A freqüência de saída, que é a derivada da fase de saída, é N vezes maior do que a freqüência da

entrada de referência.

A função de transferência do erro de fase tem uma característica passa-altos. Isto significa que

para variações lentas na fase de referência, o erro de fase será pequeno; as variações rápidas (alta

freqüência) na fase de referência, por outro lado, não serão filtradas e passarão como erro de fase.

11

2.5. RUÍDO DE FASE E TONS ESPÚRIOS NA SAÍDA DO SINTETIZADOR

Para um oscilador ideal operando na freqüência ωc, a saída pode ser expressa como

Vout(t)=A.sin(ωLOt + θ)

onde A é a amplitude e θ é uma referência de fase arbitrária, mas fixa.

Seu espectro tem a forma de um impulso de Dirac [Figura 9 (a)]. Em um oscilador real, por

outro lado, a saída tem uma expressão mais geral:

Vout(t)=A(t).sin[ωLOt + θ(t)]

onde A(t) e θ(t) são agora funções do tempo.

Devido às flutuações aleatórias representadas por A(t) e θ(t), o espectro de saída tem agora

bandas laterais ao redor da freqüência da oscilação ωLO [Figura 9 (b)], que são o ruído de fase.

Oscilador ideal

Oscilador real

∆ω

ωLO

(a)

ω

ωLO

ω

(b)

Figura 9. Espectro de saída de: (a) um oscilador ideal; (b) um oscilador real.

O ruído de fase de um oscilador real é quantificado da seguinte forma: considera-se uma

largura de banda unitária a um offset ∆ω da freqüência de oscilação ωLO [Figura 9 (b)], calcula-se

a potência do sinal nessa banda e divide-se o resultado pela potência do sinal na freqüência ωc.

Isto representa a densidade unilateral de ruído espectral em unidades de deciBell carrier per

Hertz [dBc/Hz]:

potência do ruído numa l arg ura de banda de 1 Hz a uma freqüência de ω LO + ∆ω

L{∆ω } = 10. log

potência da portadora

Por exemplo, se a potência da portadora é -2 dBm e a potência do ruído medido numa largura

de banda de 1 KHz a um offset de 1 MHz é igual a -70 dBm, então o ruído de fase é igual a: -70

dBm + 2 dBm – 30 dB = -98 dBc/Hz, onde -30 dB = -10log (1x103 Hz) é devido à banda de 1

KHz.

12

Interferência

Sinal

desejado

(a)

RF

ω

(b)

LO

ωLO

Sinal

desejado

(c)

ω

Interferência

IF

ω

Sinais downconverted

Figura 10. Efeito do ruído de fase do LO num receptor; (a) sinal de entrada, (b) espectro do oscilador e (c), espectro

do sinal após passar por mixer.

Para compreender a importância do ruído de fase num receptor sem fio considere a Figura 10.

Chegam ao receptor dois sinais, um o sinal desejado de pequena potência e outro um sinal não

desejado com um nível de potência maior (Figura 10 (a)). O sinal do oscilador local (LO) real

considerado para o downconversion tem um espectro como aquele da Figura 10 (b). Quando os

dois sinais são misturados com a saída do LO para fazer o downconversion, o sinal de saída será

formado pela superposição de dois espectros e o sinal desejado sofrerá uma considerável

degradação (Figura 10 (c)).

O efeito do ruído de fase num transmissor é ligeiramente diferente. Considere um receptor que

deve detectar um sinal na freqüência ω2 e um circuito transmissor próximo dele gerando outro

sinal na freqüência ω1. Caso seja utilizado no transmissor um oscilador com ruído de fase

considerável, o seu sinal de saída apresentará um espectro como mostra a Figura 11. Este sinal

apresenta uma potência considerável em ω2 e acaba por corromper o sinal que deve ser detectado

pelo receptor.

Transmissor

próximo

Sinal desejado

ω1

ω2

Figura 11. Efeito do ruído de fase do LO num transmissor.

13

Com o fim de dar uma idéia das especificações de ruído de fase requeridas num sistema de

telefonia celular moderna, tomemos como exemplo os sistemas GSM e DCS-1800.

Sinais bloqueadores

-23 dBm

-33 dBm

-43 dBm

Potência

do sinal

Saída do

oscilador

local

f

fLO+3 MHz

fLO

fLO+1,6 MHz

-99 dBm

fLO+0,6 MHz

Sinal

desejado

sinal

LO

Sx(f)

-118 dBc/Hz

(ruído de

fase)

fLO

Vout

SNR

f

Energia do

sinal da

interferência

Sinal

desejado

Tom espúrio

BW

fLO+fref f

Figura 12. Exemplo do ruído de fase de um oscilador local (para o sistema GSM).

Para o sistema GSM, que tem canais de 200 kHz, um sinal com potência tão pequena quanto a

de -99 dBm deve ser detectável (vide Figura 12), quando um sinal bloqueador de -43 dBm está

presente à distância de 600 kHz (três canais). Para manter um BER (Bit Error Rate) de 10-3

devemos ter um SNR (Signal-to-Noise Ratio) de 9 dB na saída do receptor (consideramos, para

exemplificar, como saída do receptor a saída do downconverter). Nessa situação o ruído de fase

permitido no oscilador será:

LGSM{∆ω} < Sdesejado - Sbloqueante – SNRespecificação – 10log(BW)

LGSM{600 kHz} < -99dbm - (-43 dBm) – 9dB – 10log(200 kHz) = -118 dBc/Hz.

Para o sistema DCS-1800, um sinal com potência de -97 dBm deve ser detectável com um

sinal de bloqueio de -43 dBm a 600 KHz também. Um cálculo similar nos leva a

LDCS-1800{600 kHz} < -116 dBc/Hz.

A tensão de controle do VCO num sintetizador de freqüência (particularmente na arquitetura

integer-N) apresenta o problema de modulação devido ao sinal de referência, seja por

acoplamento via substrato ou por espúrios não suficientemente filtrados no filtro passa baixos. Na

Figura 12 está representado na saída do oscilador local o tom espúrio a um offset de fref, onde fref é

a freqüência do sinal de referência usado no sintetizador de freqüência. A derivação da

14

especificação para o tom espúrio é similar à especificação para o ruído de fase, só que não é

considerada a largura de banda neste caso. A especificação do tom espúrio será portanto:

Sespúrio < Sdesejado - Sbloqueante – SNRespecificação, então, para offsets maiores de 3 MHz:

SespúrioGSM{>3 MHz} < -99 dBm – (-23 dBm) – 9 dB = -88 dBc.

2.6. CARACTERÍSTICAS DE RUÍDO DO SINTETIZADOR

Basicamente o ruído na saída de um PLL estará determinado por duas fontes de ruído [1], [7]:

ruído do sinal de referência, θnref , e o ruído gerado dentro do próprio VCO, θnvco. A Figura 13

modela o efeito destas duas fontes de ruído. Neste modelo G(s) representa a função de

transferência do detector de fase, do loop filter e do VCO, podendo ser escrito como

G(s)=KPDF(s)KVCO/s

onde as quantidades N, Kpd, Kvco , s e F(s) foram definidas na Figura 8.

N(s), por sua vez, representa o divisor e escrevemos

N(s)=1/N.

θnvco

θnref

+

Σ

G(s)

+

+

Σ

θnout

N(s)

Figura 13. Loop de controle utilizado para analisar o ruído num PLL. Neste esquema G(s) representa a função de

transferência do detector de fase, do loop filter e do VCO.

A resposta do loop fechado ao sinal de ruído do VCO é:

θ nout ( s)

1

N. s

=

=

θ nvco ( s) 1 + G ( s) N ( s ) N . s + K pd . F ( s ) . K vco

(3)

enquanto a resposta do loop fechado ao sinal de ruído da referência é:

N . K pd . F ( s ) . K vco

θ nout ( s)

G ( s)

=

=

θ nref ( s) 1 + G ( s) N ( s) N . s + K pd . F ( s) . K vco

(4)

15

Supondo inicialmente que o filtro do loop tenha uma função de transferência constante, ou

seja, F(s)=Klf, a função de transferência do loop aberto será:

G ( s) N ( s) =

K pd . K lf . K vco

N .s

=

KF

N .s

onde KF é o forward gain do PLL e tem unidades de s-1.

Logo, as equações anteriores, ( 3 ) e ( 4 ), se reduzem a

θ nout ( s)

1

s

=

=

θ nvco ( s) 1 + K F /( Ns) s + ω c

(5)

θ nout ( s) N ( K F / Ns )

ωc

=

=N

θ nref ( s) 1 + K F /( Ns )

s + ωc

(6)

onde ωc é definida como a freqüência de cross-over ω c =

KF

, ou seja, a freqüência em que o

N

ganho de loop aberto tem uma magnitude igual a um.

Das equações anteriores é possível obter as seguintes conclusões:

•

a função de transferência do ruído do VCO para a saída tem uma característica passa-altos

com freqüência de corte de 3 dB em ωc. Neste caso o ruído em altas freqüências passa nãoatenuado (a ação de retro-alimentação do loop é demasiado lenta para suprimir esses

componentes de ruído), e o ruído em baixas freqüências sofre atenuação, maior quanto menor

for a freqüência. Na Figura 14 (a) se ilustra as curvas de densidade espectral de potência do

ruído no oscilador e na saída do sintetizador. Nesta figura a linha sólida representa a típica

densidade espectral do ruído na saída de um oscilador [13]. Três regiões podem ser

apontadas: a primeira, em altas freqüências, constitui-se de um piso de ruído plano; a

segunda, a mais importante, é aquela onde a densidade espectral do ruído diminui com o

quadrado da freqüência de offset (ω-2). O ruído nesta região se origina de fontes de ruído

branco (normalmente ruído térmico); a terceira, é aquela onde a densidade espectral do ruído

diminui com o cubo da freqüência de offset (ω-3). Este ruído se origina do ruído de baixa

freqüência 1/f que é upconverted à freqüência da saída pelas não-linearidades do oscilador. A

linha pontilhada representa a densidade espectral do ruído de saída do sintetizador, resultado

do efeito do ruído do oscilador sobre a equação (5) (lembremos que para determinação da

densidade de ruído na saída devemos considerar a função de transferência ao quadrado).

•

o ruído da referência tem uma função de transferência passa-baixos [1] com a mesma

freqüência de corte de 3 dB, ωc. As curvas de densidade espectral de potência do ruído no

16

sinal de referência, linha continua, e na saída do sintetizador, linha pontilhada, são ilustradas

na Figura 14 (b). O ruído da referência tem a mesma forma do ruído do VCO porém, devido à

alta qualidade das fontes normalmente utilizadas, com menor magnitude. Esta vantagem se

perde pelo fato que o ruído da fonte de referência é multiplicado por N para freqüências

menores que ωc.

Sθ(ω)

Sθ(ω)

ω-2

ω-3

ω0

θnout

θnvco

θnout

θnref

ω

ωc

(a)

ωc

ω

(b)

Figura 14. Densidade espectral de potência do ruído em um sintetizador de freqüências: (a) ruído do VCO e seu

efeito na saída do sintetizador; (b) ruído da fonte de referência e seu efeito na saída do sintetizador.

2.7. BLOCOS CONSTRUTIVOS DO SINTETIZADOR DE FREQÜÊNCIA

Os blocos que veremos aqui são o detector de fase, a bomba de carga e o filtro de loop, o

oscilador controlado por voltagem e os divisores de freqüência.

2.7.1. Detector de Fase (PD)

Existem basicamente três categorias de detectores de fase [1]:

• Os PD analógicos ou multiplicadores baseados no componente DC que resulta da

multiplicação de dois sinais senoidais da mesma freqüência;

• Circuitos seqüenciais, como portas XOR e latches, que operam na informação contida no

cruzamento por zero dos sinais de entrada;

• Detector de fase e freqüência que é realmente um circuito seqüencial mas que também

oferece sinais sensíveis à freqüência para ajudar à aquisição quando o PLL não está locked.

17

2.7.1.1. PD analógicos ou Multiplicadores

Se ambas entradas do PD são senoidais pode-se utilizar um mixer ou multiplicador para

detectar a fase. Quando aplicamos os sinais de entrada A1sin(ω1t + θ1) e A2cos(ω2t + θ2) num

multiplicador, resulta um sinal de saída

vd = Ad .{sin[(ω1 – ω2)t + θ1 - θ2] + sin[(ω1 + ω2)t + θ1 + θ2]}

Quando o sintetizador está locked, ambas as freqüências, ω1 e ω2, são iguais e o componente

DC da saída do multiplicador é igual a Ad sin(θ1 - θ2). Este fator é proporcional à diferença de

fase para pequenos valores de (θ1 - θ2) e é o componente útil na saída do PD. Outros componentes

não-desejados estarão também presentes na saída: a componente na freqüência (ω1+ω2) para o

multiplicador ideal, como pode ser visto pela relação acima e componentes em freqüências

múltiplas de ω1 e ω2, devido ao acoplamento entre entrada e saída e não linearidades, para um

multiplicador real. Estes componentes devem ser atenuados ou eliminados pelo filtro do loop.

O PD com multiplicadores é especialmente útil em aplicações onde a freqüência de referência

é muito alta para outras categorias de PDs e onde a largura de banda do loop é o suficientemente

pequena para atenuar os componentes não-desejados [1], [5].

2.7.1.2. Porta OU Exclusiva

Uma porta OU exclusiva pode também ser utilizada como PD [Figura 15 (a)]. A forma de

onda da saída da porta para dois sinais de entrada A e B é mostrada na Figura 15 (b) e seu valor

médio é proporcional à diferença de fase como indicado na Figura 15 (c). Observe que neste caso

o valor médio de C é linear para erros de fase de até meio período.

A

B

(a)

C

τ

T

(b)

A

B

C=A

(c)

B

Valor médio

de C

-1

-0.5

0

0.5

1

τ /T

Figura 15. (a) Detector de fase XOR; (b) Operação; (c) Curva de transferência do valor médio da saída. T é o

período do sinal A e τ é a diferença de fase entre A e B.

18

2.7.1.3. Latch

A operação de um latch como um detector de fase é mostrada na Figura 16. Pulsos estreitos

em ambas entradas A e B fazem o set (forçam a saída C para nível alto) e o reset (forçam a saída

C para nível baixo). O valor médio de C tem a forma de dente-de-serra, com uma faixa linear

para erros de fase de até um período. Esta é precisamente a vantagem deste PD.

(a)

A

S

B

R

C

Q

τ

T

(b)

A

B

C

(c)

Valor

médio de C

τ /T

-1

-0.5

0

0.5

1

Figura 16. (a) Detector de fase tipo latch; (b) Operação; (c) Curva de transferência do valor médio da saída.

2.7.1.4. Detector de Freqüência e Fase (PFD)

O PFD é também um PD seqüencial mas contém uma função de memória que lhe permite dar

informações sobre a freqüência quando o PLL não está locked [15]. Usualmente se implementa

com uma bomba de carga, como se ilustra na Figura 17, que é responsável por gerar uma tensão

de saída.

O PFD propriamente dito tem duas saídas, Up e Dn, que abrem ou fecham as duas fontes de

corrente da bomba de carga. Há quatro possíveis estados de funcionamento: no primeiro estado,

um sinal ativo em Up faz com que a fonte de corrente superior seja conectada a saída, resultando

numa corrente de saída Ic positiva. Esta corrente causa o aumento na voltagem de saída C. Este

estado é o estado de pump-up; no segundo estado, um sinal ativo em Dn faz com que a fonte de

corrente inferior seja conectada, resultando numa corrente de saída Ic negativa. Esta corrente

causa a diminuição da voltagem de saída C. Este é o estado de pump-down; no terceiro possível

estado nenhum dos sinais Up ou Dn está ativo. A corrente de saída é zero e o nó C é um nó de

alta impedância; no quarto estado ambas as fontes de corrente estão ativas e nunca deve acontecer

19

devido a um mecanismo de reset. A corrente de saída em cada momento é convertida em

voltagem na impedância Zlf .

1

(a)

Vref

Vfb

1

VDD

Q

D

D-FF

CLK

R

reset

Up

I

R

CLK

D-FF

Q

D

C

Zlf

I

Dn

T

τ

(b)

IC

Vref

Vfb

IC

(c)

Valor

medio de

C

-1 -0.5

0

0.5

1

τ /T

Figura 17. (a) Detector de freqüência e fase; (b) Operação; (c) Curva de transferência do valor médio da saída.

O principio de operação do PFD é mostrado na Figura 17 (b). Uma borda de subida no pulso

de referência faz com que o sinal Up seja ativado e com isso a tensão na saída comece a

aumentar; similarmente, uma borda de subida na saída do divisor de loop faz com que o sinal Dn

seja ativado e com isso a tensão na saída comece a diminuir. Quando ambos os sinais, Up e Dn,

estão simultaneamente ativos, uma porta AND faz com que estes sinais sejam desativados (reset

nos dois D-flip-flops). A saída média da voltagem em função da fase é mostrada na Figura 17 (c).

A faixa de trabalho linear é para erros de fase de até dois períodos.

O problema mais importante neste circuito tem relação com a chamada “zona morta”, que

aparece perto da região de erro de fase zero [16], [17], [18]. Se ambos pulsos, o de referência e o

do divisor, aparecem em instantes próximos (diferença de fase pequena) o reset do PFD pode ser

ativado sem que nenhuma das fontes de corrente tenha conduzido (dependendo dos atrasos do

circuito). Com isso, valores pequenos de erro de fase não serão corrigidos. A Curva de

transferência do valor médio da saída do PFD tem uma resposta plana, a“zona morta”, perto da

20

diferença de fase zero (ver Figura 18). O PLL está aí efetivamente aberto, já que Kpd é zero, e o

espectro da saída reflete isto.

“zona morta”

(comprimento

exagerado)

Valor

médio de C

-1

-0.5

0

1

0.5

τ /T

Figura 18. Característica de transferência do PFD com “zona morta”.

Este fenômeno é remediado de diversas formas [16], [17], [18]. Uma solução simples é não

permitir o reset antes que um pulso de largura mínima seja aplicado à bomba de carga. Desta

forma, mesmo se não houver uma diferença de fase entre ambas entradas do PFD, ambas as

saídas Up e Dn estarão ativas durante um intervalo curto de tempo [1].

2.7.2. Bomba de carga e filtro do loop

Já foi visto na seção anterior como funciona uma bomba de carga e a sua utilização dentro do

sintetizador. Agora será mostrada sua influência e a do filtro do loop na função de transferência

da resposta de todo o sintetizador. Partindo da configuração mostrada na Figura 19, é possível

fazer uma análise da resposta do circuito geral.

VDD

I

Up

x(t) [θref(s)]

PFD

IC

VCO

Dn

I

[θfb(s)]

y(t) [θout(s)]

CP

1/N

Figura 19. Sintetizador com bomba de carga.

Uma bomba de carga provê um ganho infinito para uma diferença de fase estática [7] na

entrada do PFD, já que mesmo para erro de fase pequeno, se teria uma acumulação indefinida de

carga em CP; por outro lado, a resposta de um PFD/Bomba de carga a um degrau de fase é uma

21

rampa linear. Estas duas observações nos indicam que a função de transferência do PFD/Bomba

de carga deve ser modelada por uma função de um pólo na origem, ou seja como

Ve(s)= KPFD[θref(s)- θfb(s)]/s

onde KPFD é o ganho do PFD, θref(s) é a fase do sinal de referência, θfb(s) é a fase de retroalimentação e Ve(s) a voltagem de erro do PFD/Bomba de carga para aplicar no VCO.

Sendo assim a função de transferência de loop fechado do sintetizador, sem o filtro, é dado por

K PFD K VCO

θ (s)

s

s

H ( s ) = out

=

K PFD K VCO 1

θ ref ( s)

1+

s

s N

H (s) =

K PFD KVCO

K K

s 2 + PFD VCO

N

onde θout(s) é a fase do sinal de saída.

Veja que nesta função aparecem dois pólos no eixo imaginário nas freqüências

ω =±j

K PFD K VCO

, o que torna o sistema potencialmente instável. Para evitar a instabilidade,

N

deve-se agregar um zero à função de transferência de loop aberto. Isto contrasta com a análise

anterior, onde o detector de fase era modelado como um amplificador. Naquela situação a função

de transferência (1), é um filtro passa-baixos independente do loop filter, sendo estável sem

necessidade de acrescentar zeros ([1], [7]). O zero estabilizador num sintetizador com bomba de

carga é realizado colocando um resistor em série com o capacitor CP (vide Figura 20), e este

conjunto passará a ser o filtro do loop.

VDD

I

Vout

CP

I

R

Figura 20. Adição de um zero a uma bomba de carga.

22

A operação de comutação da bomba de carga faz deste sintetizador um sistema de tempo

discreto, embora, se a largura de banda do loop for muito menor que a freqüência da entrada de

referência, seja possível estudá-lo como um sistema continuo [19].

Calculemos agora a nova função de transferência para o PFD/bomba de carga (baseado na

implementação da Figura 20). Para um erro de fase de [θref - θfb] a corrente média carregando o

capacitor é dada por I [θref - θfb]/(2π) [19], e a variação média na voltagem de controle do VCO é

igual a

Ve ( s) = Vc ( s ) =

I (θ ref − θ fb )

2π

(R +

1

)

CP s

Obtém-se a partir desta equação a seguinte função de transferência para o loop fechado.

I

( RCP s + 1) KVCO

2π CP

H (s) =

1

I 1

I

s2 +

KVCO Rs +

KVCO

2π N

2π CP N

A freqüência natural do circuito será

ωn =

K VCO

I

(7)

2π C P N

(independente do R), com um fator de amortecimento dado por:

ζ =

R

2

IC P K VCO ω n RC P

=

(8)

2π N

2

Por questão de estabilidade do loop, o fator de amortecimento ζ normalmente escolhido é igual

a 0,7 [20].

A largura de banda do loop anterior pode ser encontrada e tem a seguinte forma [21]:

[

ω 3dB = ω n 2ζ 2 + 1 + (2ζ 2 + 1) 2 + 1

]

1

2

(9)

onde ω3dB é a freqüência onde o ganho do loop fechado cai de 3 dB.

Em muitas aplicações é desejável maximizar a largura de banda do loop, por exemplo, para

diminuir o tempo levado para chegar ao estado locked ou para melhorar a resposta ao ruído de

fase do circuito. Por outro lado, a medida que a largura de banda do loop começa a ser

comparável com a freqüência de entrada, a aproximação de tempo continuo utilizada aqui não

vale e é preciso utilizar análise de tempo discreto.

23

Gardner derivou um limite superior para ωn [19] para garantir estabilidade, fazendo uma

análise discreta. Em projetos típicos, a largura de banda do loop é fixada em um décimo da

freqüência de entrada para garantir tal estabilidade [7].

A comutação das fontes de corrente da bomba de carga causa uma grande quantidade de

ripples na voltagem de controle do VCO. Estes ripples podem ser suprimidos agregando um

pequeno capacitor C2 em paralelo ao filtro do loop como mostrado na Figura 21.

VDD

I

Voltagem de controle do VCO

CP

I

R

C2

Figura 21. Adição de C2 no filtro do loop para suprimir o ripple.

A adição deste capacitor C2 agrega outro pólo à função de transferência e converte o sistema

num sistema de terceira ordem. Por outro lado, se o capacitor é pequeno o suficiente (C2 < 0,1 CP)

o sistema pode continuar a ser analisado como um sistema de segunda ordem [22].

2.7.3. Osciladores controlados por voltagem

Um oscilador controlado por voltagem (VCO) gera um sinal periódico com freqüência

dependente de uma voltagem de controle. Os osciladores mais utilizados em PLLs integrados são

os osciladores LC e os osciladores em anel.

O oscilador LC tem tido a preferência nos últimos anos por seu melhor desempenho quanto ao

ruído de fase. Topologias típicas de osciladores LC são: o oscilador de par cruzado NMOS, o

oscilador de par cruzado CMOS e o oscilador Colpitts. Os diagramas esquemáticos dos circuitos

são mostrados na Figura 22. Os osciladores de par cruzado NMOS e CMOS possuem o mesmo

princípio de operação, porém, a última delas, apresenta um maior número de fontes de ruído

(maior número de transistores). A topologia de oscilador com par cruzado NMOS tem sido usada

nas publicações recentes devido a este fato. O oscilador Colpitts é raramente aplicado devido ao

fato de ser um circuito single-ended, o que o faz mais sensível ao ruído da fonte de alimentação e

ao ruído do substrato.

24