SINTETIZADOR DE FREQÜÊNCIAS PARA TRANSCEPTOR DE RF CMOS EM

SISTEMA EM CHIP

Rafael R. P. Soares, Pablo R. O. Vogel, José C. da Costa

Universidade de Brasília – Departamento de Engenharia Elétrica – LPCI (Lab. de Proj. de Circuitos

Integrados) Caixa Postal 4386 – Brasília – DF – 70919-970

[email protected], [email protected]

SUMMARY

The design of a 0,35 µm CMOS PLL-based Frequency Synthesizer for a System-on-Chip RF transceiver is

presented. The circuit operates in the 915 – 927 MHz range and uses 50 KHz channels for communication. The

circuit was designed aiming reduced area and power consumption constraints. The voltage-controlled oscillator

uses a ring-based topology. The PLL feedback network uses a dual-modulus prescaler, a fixed modulus divider,

and a programmable modulus divider. The proposed application for the circuit is a node for wireless sensor

network in a system for irrigation control on crope.

RESUMO

O projeto de um Sintetizador de Freqüências utilizando uma topologia PLL (Phase-Locked Loop) para um

transceptor de RF em Sistema em Chip é apresentado. O circuito opera na faixa de 915 – 927 MHz e as

transmissões são realizadas em canais de 50 KHz. O projeto foi realizado com o objetivo de minimizar a área e

o consumo de potência. O oscilador controlado por tensão utiliza uma topologia em anel para minimizar a área.

O módulo da divisão da realimentação do PLL é dado por um prescaler de módulo duplo, um divisor de

módulo fixo e um divisor de módulo programável. A aplicação proposta para o sistema é um nó de uma rede

sem-fio de sensores para um sistema de controle de irrigação. A tecnologia utilizada é 0,35 µm CMOS.

SINTETIZADOR DE FREQÜÊNCIAS PARA TRANSCEPTOR DE RF CMOS EM

SISTEMA EM CHIP

Rafael R. P. Soares, Pablo R. O. Vogel, José C. da Costa

Universidade de Brasília – Departamento de Engenharia Elétrica – LPCI (Lab. de Proj. de Circuitos

Integrados) Caixa Postal 4386 – Brasília – DF – 70919-970

[email protected], [email protected]

ABSTRACT

O projeto de um Sintetizador de Freqüências utilizando

uma topologia PLL (Phase-Locked Loop) para um

transceptor de RF em Sistema em Chip é apresentado. O

circuito opera na faixa de 915 – 927 MHz e as

transmissões são realizadas em canais de 50 KHz. O

projeto foi realizado com o objetivo de minimizar a área e

o consumo de potência. O oscilador controlado por tensão

utiliza uma topologia em anel para minimizar a área. O

módulo da divisão da realimentação do PLL é dado por

um prescaler de módulo duplo, um divisor de módulo fixo

e um divisor de módulo programável. A aplicação

proposta para o sistema é um nó de uma rede sem-fio de

sensores para um sistema de controle de irrigação. A

tecnologia utilizada é 0,35 µm CMOS da AMS.

1. INTRODUÇÃO

O desenvolvimento das tecnologias de fabricação de

circuitos integrados (CI) tem possibilitado uma verdadeira

revolução nas aplicações de dispositivos eletrônicos. As

técnicas de escala muito alta de integração (VLSI) e os

avanços na implementação de sistemas completos em um

único chip (SoC), colocando seções de RF, banda básica e

digitais em uma mesma pastilha de semicondutor vêem

abrindo novos caminhos e barateando custos de projeto.

As comunicações sem fio são uma área que vem se

beneficiando sobremaneira desse avanço tecnológico.

Dispositivos cada vez menores, de melhor desempenho e

de menor custo são desenvolvidos e incorporados a

sistemas de telecomunicação, medição, biomedicina,

entretenimento, entre outros.

A Empresa Brasileira de Pesquisa Agropecuária

(EMBRAPA), em parceria com diversos institutos de

pesquisa de todo o Brasil, incluindo a Universidade de

Brasília (UnB), vem desenvolvendo uma aplicação para

monitoramento e controle de umidade do solo, baseada em

um SoC que adquire dados dos sensores de umidade,

processa e transmite a uma central de comando, que pode,

assim, interferir sobre as condições de irrigação da

plantação. Tal aplicação tem por objetivo a redução do

desperdício de água e energia, enquanto melhora a

produtividade.

O sistema em chip em desenvolvimento é composto

por estruturas como processador, memória, conversores

AD/DA, transceptor, entre outras. O presente trabalho se

refere ao projeto de um sintetizador de freqüências,

componente do transceptor do sistema.

O transceptor irá operar em banda ISM, na faixa de

915 a 927,7 MHz, em modulação OOK, em esquema

Half-Duplex, e fará a comunicação entre os nós e a central

do sistema de irrigação. A alimentação será garantida por

uma fonte de 3,3V

O sintetizador de freqüências tem por função gerar as

freqüências de transmissão e recepção do sistema a partir

de uma freqüência de referência. A referência é dada por

um oscilador com cristal externo. A saída é determinada

por um Oscilador Controlado por Tensão (VCO) e tem a

fase relacionada com o sinal de referência externo e sua

freqüência de oscilação como um múltiplo da freqüência

de referência.

Esse projeto foi implementado em tecnologia CMOS,

0,35µm, duas camadas de poli e quatro camadas de metais.

2. TOPOLOGIA DO SINTETIZADOR DE

FREQÜÊNCIAS

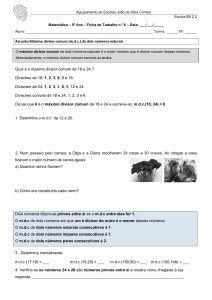

A topologia para o sintetizador de freqüências pode ser

visualizada na Figura 1 [5][6]. Ela é uma topologia do tipo

Phase-Locked Loop (PLL) que tem como vantagens a

utilização de componentes digitais e a facilidade de

integração. Essa topologia foi escolhida devido à

1

Figura 1 – Topologia do sintetizador de freqüências implementado

necessidade de sintetizar canais de 50 KHz em uma

freqüência de 915 MHz. O divisor M é utilizado para

ajustar a freqüência de front-end enquanto o divisor F é

utilizado para ajustar os canais de 50 KHz. Ao utilizar

um sinal de referência de 50 KHz, é possível sintetizar

canais com essa largura sem a necessidade de realizar

divisões fracionárias, reduzindo a complexidade do

circuito.

O valor da freqüência sintetizada é determinado pelos

divisores N, M e F de acordo com as equações abaixo:

f VCO = f ref × [N × (M − F ) + F × ( N + 1)]

f VCO = f ref × (M × N + F )

(1)

O valor de Fref é igual ao valor da largura dos canais

que serão sintetizados (50 KHz). O circuito é iniciado

com o divisor de módulo duplo ajustado para divisão por

N+1 e permanecerá com esse módulo durante F ciclos de

divisão. Ao final dos F ciclos, o módulo é alterado para

divisão por N e assim permanecerá por (M – F) ciclos.

Para o funcionamento correto do circuito, é necessário

que o divisor F tenha módulo menor que o divisor M.

O Detector de Fase-Freqüência (PFD) é utilizado

para que o sinal de saída esteja em fase com o sinal de

referência do circuito. A saída do PFD é um sinal digital

relacionado com as diferenças de fase e freqüência dos

seus sinais de entrada. O filtro recebe o sinal digital do

PFD e transforma em um sinal analógico adequado para

o controle da freqüência do VCO. O filtro deve prover

um zero de modo a promover a estabilidade do PLL. As

baixas freqüências de operação do filtro resultam em

capacitores de grandes dimensões, fato que justifica um

esforço de projeto para otimizar esse bloco visando

reduzir a sua área.

A

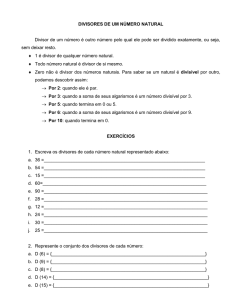

Figura 2 – VCO em anel de 5 estágios

Nesse trabalho, foram projetados os blocos que

compõe o sintetizador de freqüências, com exceção do

filtro, que está em fase de desenvolvimento. Os blocos

projetados foram enviados para prototipagem para serem

testados isoladamente e formando o PLL completo. Para

a realização do teste do PLL completo será utilizado um

filtro externo.

3. PROJETO DOS BLOCOS DO PLL

3.1. Oscilador Controlado por Tensão

A topologia escolhida para o VCO está mostrada na

Figura 2 [6]. Ela é baseada em um oscilador em anel de

5 estágios formado por inversores. Osciladores em anel

são freqüentemente utilizados em sintetizadores de

freqüência integrados por não precisarem de indutores,

que normalmente ocupam grandes áreas na integração.

Essa topologia apresenta área reduzida, baixa

complexidade e o seu controle de freqüência não causa

grande impacto na freqüência de oscilação,

possibilitando atingir freqüências próximas da freqüência

máxima que teria apenas o oscilador em anel, porque o

controle da freqüência não está inserido em série entre os

estágios inversores [6].

Tabela 1 – Características do VCO

Característica

VCO

2

Faixa de operação

Ganho

Área

Potência consumida

Controle da freqüência

897 – 970 MHz

3,65 MHz/100 mV

1900µ2

2,7 mW

um sinal

Fref

Up

Reset

Down

Fvco

Figura 4 – Detector de Fase-Freqüência

3.2. Detector de Fase-Freqüência

Figura 3 – Resposta simulada do VCO a 917 MHz

O controle da freqüência é determinado por um

resistor variável controlado por tensão e um capacitor

conectado entre cada estágio inversor de modo a

fornecer um incremento na constante de tempo RC. A

Tabela 1 resume as características do VCO projetado. A

resistência variada é formada por um transistor NMOS.

O sinal de porta desse transistor é proveniente do filtro

do PLL e é responsável pelo controle da freqüência de

oscilação do VCO ao ajustar a constante de tempo RC

entre os estágios inversores. A freqüência máxima é

atingida quando os resistores variáveis estão desligados.

Ainda assim, a capacitância de dreno do NMOS continua

sendo carregada, limitando a freqüência de oscilação.

Técnicas de layout podem ser empregadas para

minimizar a área do dreno, reduzindo as capacitâncias

[10]. A Figura 3 mostra a saída simulada do VCO a 917

MHz.

Ao testar a resposta do VCO para as variações na

tecnologia [2] foi obtida uma variação de 0,2% na

freqüência absoluta para uma variação de 10% no valor

dos componentes críticos. Em termos absolutos, a

variação é aceitável. Entretanto, devido à dimensão dos

canais de comunicação, ela não é suficiente para garantir

o posicionamento dos canais na faixa especificada. As

simulações foram realizadas no Spectre e utilizam

modelos bsim para descrição dos transistores com os

parâmetros correspondentes ao arquivo de tecnologia do

fabricante.

O esquemático do detector de fase-freqüência é

mostrado na Figura 4 [6]. Esse é um circuito

freqüentemente

utilizado

pela

facilidade

de

implementação, por ser um circuito digital

implementável em qualquer biblioteca CMOS, e por

fornecer informações sobre as diferenças de fase e de

freqüência dos sinais de entrada. Essa topologia

estabiliza o loop com diferença de fase dos sinais de

entrada nula e realiza uma operação de amostragem, uma

vez que a comparação dos sinais é feita durante as

bordas de subida. Se a borda de subida na entrada Vref

ocorre antes da borda na entrada Fvco, a saída Up será

ativada e permanecerá assim enquanto não ocorrer a

borda de subida em Fvco. Nesse momento as duas saídas

ficam desativadas. A saída Up ativa significa que a saída

freqüência do VCO deve ser aumentada, de modo para

reduzir a diferença de fase entre ele e o sinal de

referência. Da mesma forma, se a saída Down estiver

ativa significa que o VCO está adiantado em relação ao

sinal de referência. A Figura 5 mostra a operação

simulada do circuito com Fref = 50 KHz e Fvco = 45

KHz.

3.3. Divisores de Freqüências

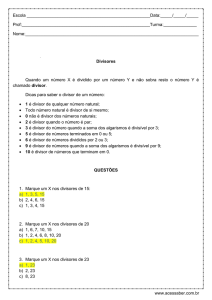

Foram implementados 3 tipos de divisores, como pode

ser visto na Figura 1. O divisor N é um prescaler de

módulo duplo. O divisor M é um contador de módulo

fixo e o divisor F é contador de módulo variável.

O prescaler é baseado na topologia apresentada em

[9]. Na etapa de teste, o módulo da divisão do prescaler

utilizado é de N/N+16. O prescaler é formado por um

divisor síncrono de módulo duplo, 5/6, e um divisor

assíncrono de módulo 16, como mostra a Figura 6.

Assim, o prescaler divide por 80 quando o módulo de N

for 5 ou por 96 quando o módulo de N for 6 (N+16).

3

Figura 6 – Prescaler de módulo N/N+16 formado por

um divisor síncrono (em cima) e um assíncrono (em

baixo)

Figura 5 – Simulação do PFD com Fref = 50 KHz e

Fvco = 45 KHz

Para sintetizar os canais de 50 KHz, o módulo da

divisão do prescaler deve ser de N/N+1. Para obter esse

módulo será utilizado o circuito da Figura 7 [9]. Nesse

circuito, a lógica combinacional mostrada entre os dois

divisores (síncrono e assíncrono) faz com que o divisor

síncrono divida por 6 (N+1) em apenas um dos dezesseis

ciclos do divisor assíncrono. Assim, o resultado da

divisão será 15 x 5 + 1 x 6 = 81.

O divisor síncrono é o único que opera em alta

freqüência, que é a freqüência gerada pelo VCO. A

topologia adotada para esse divisor utiliza quatro FlipFlops tipo D e duas portas NAND para fazerem a

seleção do módulo da divisão. Para a operação em alta

freqüência do divisor síncrono, o projeto dos Flip-Flops

foi realizado utilizando técnicas TSPC (True Single

Phase Clocking) [8], resultando no circuito da Figura 8.

Na Figura 9 pode ser visualizado o funcionamento

simulado do Flip-Flop tipo D operando a 900 MHz. Na

Figura 10 é mostrada a resposta simulada do divisor

síncrono, do sinal de controle do módulo da divisão e do

prescaler completo para uma entrada de 900 MHz.

Os divisores de freqüências M e F foram projetados

segundo a lógica de um contador síncrono progressivo

[4] utilizando 9 bits, Figura 11. Uma cadeia de flip-flops

tipo D somada à lógica de realimentação implementa

uma máquina de estados síncrona que funciona como um

contador. Por esses divisores operarem em freqüências

entre 9 a 12 MHz, na saída do prescaler, não foi

necessário utilizar técnica dinâmica para o projeto dos

Flip-Flops empregados aqui. Na configuração de

contador progressivo, m flip-flops implicam em módulo

da contagem igual a 2m. Para usar essa máquina com um

módulo cujo valor está compreendido entre 2 e 2m é

necessário à inserção de uma palavra externa, que faz

com que a contagem não reinicie do zero, mas de um

valor mais alto. A inserção

Figura 7 – Prescaler de módulo N/N+1

dessa palavra é feita impondo-se às entradas dos flipflops o valor desejado, através de uma lógica de

multiplexação responsável por ler a palavra externa. A

inserção pode ocorrer de duas formas: a cada overflow

dos divisores ou habilitando o sinal de Sel.

O circuito da Figura 11 foi utilizado em duas

configurações. Para formar o divisor de módulo fixo M,

as entradas de dados foram fixadas em nível lógico '1' ou

'0'. Para obter o divisor de módulo programável F, as

entradas de dados foram conectadas em um conversor

serial-paralelo para possibilitar o teste. O valor

determinado pelo conversor determinará o canal de

transmissão desejado. A Figura 12 mostra a

realimentação completa do PLL com os divisores N, M e

F, assim como o Flip-Flop RS (Figura 1). O sinal de

seleção de dados de ambos os contadores, M e F, está

conectado à saída do contador M. Quando a contagem de

M terminar significa que a divisão total terminou. Nesse

momento, os dois contadores devem ser reinicializados

para e o módulo da divisão o divisor de módulo duplo

deve ser colocado para N+1.

4

Figura 8 – Flip-Flop tipo D para operar em 900 MHz

utilizando técnica TSPC

Figura 10 – Resposta do prescaler da Figura 6

mostrando separadamente as respostas do divisor

síncrono com o módulo variando (em baixo), do sinal de

controle do módulo da divisão (no meio) e do prescaler

completo (em cima).

Figura 9 – Simulação do Flip-Flop tipo D a 909 MHz

3.4. Charge Pump

O charge pump converte a saída diferencial do PFD em

corrente para efetuar a carga ou descarga do filtro. O

circuito é composto por duas fontes de corrente

controladas por duas chaves. O inversor antes da chave

PMOS é necessário porque a saída do PFD é um pulso

positivo. A saída do PFD é obtida entre as chaves. A

capacidade de corrente é de 68 µA. O charge pump pode

ser visualizado na Figura 13, que mostra o todo o

sintetizador com exceção do filtro.

Figura 11 - Contador síncrono progressivo de 9 bits

3.5. Buffer

Um buffer foi implementado entre o VCO e o prescaler

para que a freqüência de oscilação do VCO não seja

afetada pela carga do prescaler. O buffer é uma cascata

de inversores de 5 estágios, sendo o primeiro estágio de

dimensões mínimas, projetado para atraso mínimo [1]. A

alteração de fase devido ao buffer é mínima não tendo

efeito na estabilidade do PLL.

5

Figura 12 – Realimentação do PLL formada pelo

prescaler, pelos divisores N, M e F e pelo Flip-Flop RS

(vide Figura 1).

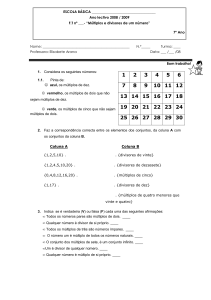

4. LAYOUT FINAL

A Figura 14 mostra o layout final do circuito.

Algumas estruturas isoladas para teste foram

incluídas no protótipo. Entre as estruturas que compõe o

PLL, foram enviados um Flip-Flop D projetado para alta

freqüência, o prescaler contendo os divisores síncronos e

assíncronos, o divisor F formado pelo contador de 9 bits

e o conversor serial-paralelo, o detector de fasefreqüência e o oscilador controlado por tensão. Além

dessas estruturas, ainda foram enviados capacitores de

óxido de porta em poço P e poço N e transistores

isolados. Os capacitores de óxido de porta possuem

capacitância por unidade de área de aproximadamente 5

vezes maior que a capacitância poly-poly na tecnologia

utilizada. A sua caracterização vai servir como referência

para sua utilização como capacitor para o filtro do loop,

o qual será integrado na versão final do sintetizador. Os

transistores isolados vão possibilitar a caracterização

desses componentes para que um modelo preciso possa

ser utilizado no projeto dos módulos de alta freqüência

do circuito, como o VCO.

5. CONCLUSÕES

Nesse trabalho foram apresentados os blocos do

oscilador controlado por tensão, do detector de fasefreqüência e dos divisores da realimentação que compõe

a topologia de PLL da Figura 1. O PLL foi integrado e

enviado para prototipagem. A utilização de um filtro

externo na fase de testes vai possibilitar testar e otimizar

Figura 13 – Topologia PLL do sintetizador de

freqüências incluindo o VCO, buffer, divisores de

realimentação, PFD e charge pump.

esse bloco quanto ao seu funcionamento e as suas

dimensões. Outros blocos de testes foram enviados

separadamente. Os trabalhos futuros incluem o teste do

circuito fabricado e sua análise com diferentes

topologias de filtro. Com os resultados, os blocos

projetados poderão ser otimizados resultando em um

sintetizador de freqüências totalmente integrado.

6. AGRADECIMENTO

Os autores agradecem à CAPES e ao CNPq pelo

apoio financeiro dado ao projeto.

7. REFERÊNCIAS

[1] Baker, R. J., H. W. Li, D. Boyce, CMOS Circuit Design,

Layout, and Simulation, IEEE Press Series on

Microelectronics Systems.

[2] ENG 182 Rev. 2 – 0.35 µm CMOS C35 Process

Parameters – AustriaMicroSystems.

[3] J. Craninckx, M. S.J. Steyaert, " A Fully Integrated CMOS

DCS-1800 Frequency Synthesizer," Journal of Solid-State

Circuits, IEEE, December 1998.

[4] P. R. O. Vogel, J. C. Costa, "Divisor de Freqüências de 11

bits com Tecnologia CMOS 0.35 µm," Graduating Project,

University of Brasilia, Brazil, July, 2003.

[5] Rohde, U. L., Digital PLL Frequency Synthesizers –

Theory and Design, Prentice-Hall, USA, 1983.

6

[6] R.R.P. Soares, J.C. Costa, "Frequency Synthesizer for a

System-on-Chip RF Transceiver," Student Forum 2003,

SBMicro, São Paulo, Brazil, September 8-11.

[7] ] R.R.P. Soares, J.C. Costa, "Sintetizador de Freqüências

915 MHz," Graduating Project, University of Brasilia, Brazil,

February, 2003.

[8] R. Rogenmoser, N. Felber, Q. Huang, W. Fichtner, "1.16

GHz Dual-Modulus 1.2 µm CMOS Prescaler," Custom

Integrated Circuits Conference, IEEE, 1993.

[9] R. Rogenmoser, Q. Huang, F. Piazza, "1.57 GHz

Asynchronous and 1.4 GHz Dual-Modulus 1.2 µm CMOS

Prescaler," Custom Integrated Circuits Conference, IEEE,

1994.

[10] Y. Savaria, D. Chtchvyrkov, J. F. Currie, "A Fast CMOS

Voltage-Controlled Ring Oscillator".

Figura 14 – Layout Final do Sintetizador de Freqüências

7