DEPARTAMENTO DE CIÊNCIA DA COMPUTAÇÃO

BACHARELADO EM INFORMÁTICA

SISTEMAS OPERACIONAIS I

10 SEM/03

Teste 1 - de Nivelamento

DURAÇÃO: 30 MINUTOS

Aluno: ________________________________________________ Escore: __________

Trata-se de uma avaliação que visa verificar seu conhecimento prévio sobre conceitos básicos e

arquitetura de computadores. Escolha a opção que melhor atenda a pergunta.

1. Os diferentes módulos que compõem um computador se comunicam entre si através de:

A) Portas digitais

B) Flip-Flops

C) Barramentos

D) Latches

2. A unidade da UCP responsável pela execução das operações lógicas e aritméticas é a:

A) Cache

B) UCC

C) UDD

D) ULA

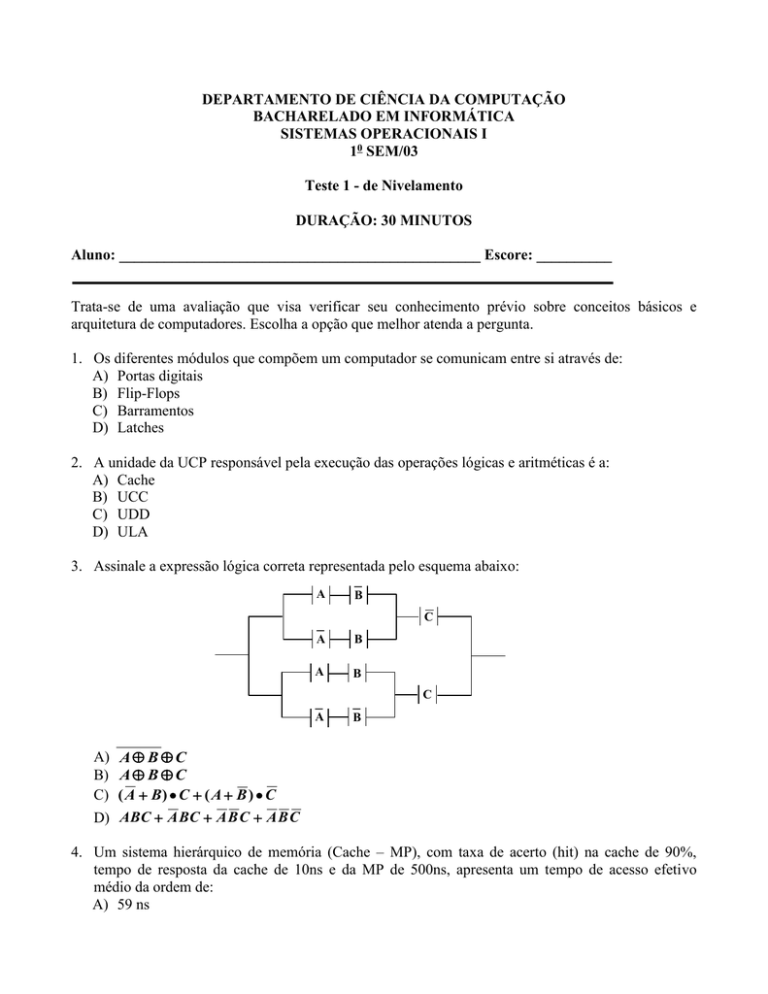

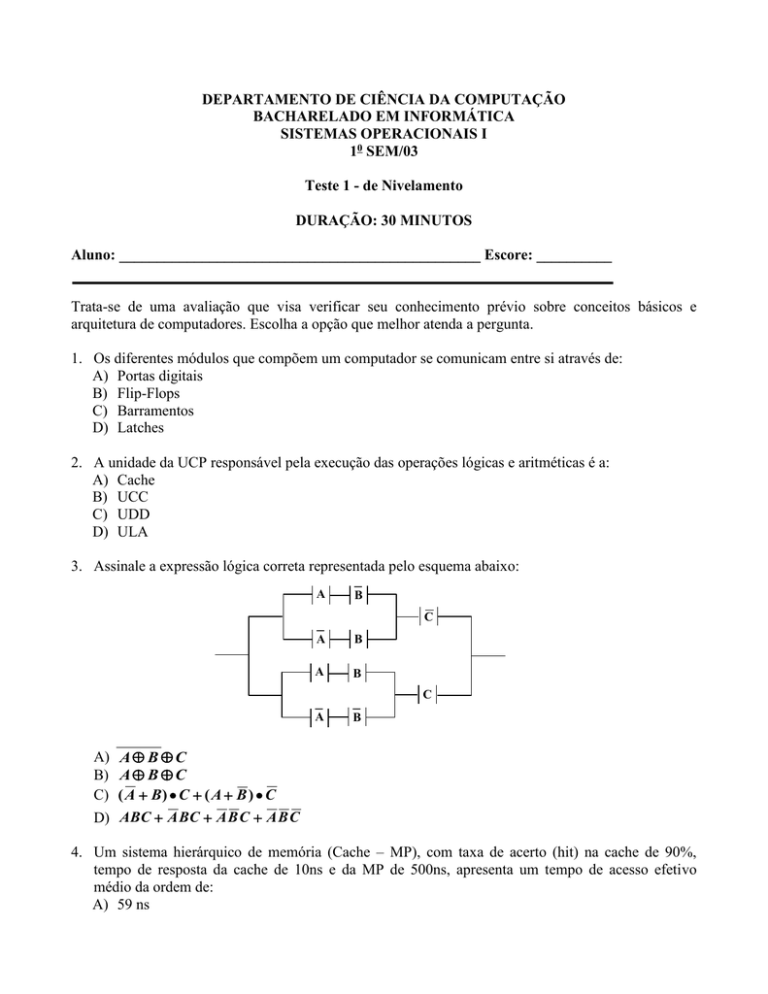

3. Assinale a expressão lógica correta representada pelo esquema abaixo:

_

A

B

C

_

A)

B)

C)

D)

A

B

A

B

_

_

A

B

C

A B C

A B C

( A B) C ( A B ) C

ABC A BC A B C A B C

4. Um sistema hierárquico de memória (Cache – MP), com taxa de acerto (hit) na cache de 90%,

tempo de resposta da cache de 10ns e da MP de 500ns, apresenta um tempo de acesso efetivo

médio da ordem de:

A) 59 ns

B) 60 ns

C) 460 ns

D) 51 ns

5. Uma máquina RISC dotada de um pipeline de 5 estágios, cada um com tempo de operação da

ordem de 100ns, apresentará teoricamente, sob condições ótimas, uma capacidade de processar:

A) 2 Mips

B) 100 Mips

C) 20 Mips

D) 10 Mips

6. Com relação à freqüência de clock de um microprocessador, assinale a afirmativa errada:

A) É a velocidade com que o microprocessador realiza suas atividades internas

B) É um oscilador externo ao microprocessador que gera pulsos a intervalos regulares

C) A cada pulso de clock, uma ou mais micro-operações podem ser realizadas

D) Não é uma medida segura para calcular o desempenho do microprocessador

7. Na construção de um programa para processamento paralelo, o programador deve tomar especial

cuidado com os erros que podem ser gerados a partir de instruções que:

A) Apresentem dependência de dados

B) Façam leitura e/ou escrita em disco

C) Realizem operações aritméticas e lógicas

D) Manipulem complexas estruturas de dados

8. O número “1001110011.00111” em binário, quando convertido para os sistemas octal e

hexadecimal resulta, respectivamente, nos seguintes valores:

A) 1163.13/8 e 273.31/16

B) 4711.13/8 e 9C3.31/16

C) 1163.16/8 e 273.38/16

D) 4711.16/8 e 9C3.38/16

9. Num computador, as informações e dados são armazenados na forma digital em diferentes tipos de

memória. Há memórias que são voláteis, onde a permanência do dado é temporária, e há memórias

persistentes. Um exemplo de memórias voláteis e não voláteis está na alternativa:

A) EPROM, Bios

|

CDROM, DVD

B) Registradores, DVD

|

Disquete, CDROM

C) Memória Principal, Cache |

Disco rígido, Disquete

D) Memória RAM, Cache

|

Disco rígido, Registradores

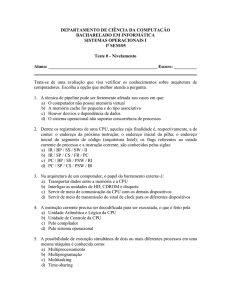

10. Observe o diagrama de blocos abaixo, representando o processo de tradução de um programa fonte.

(04)

Programa Fonte

em

Ling. Alto Nível

(01)

Módulo

Objeto

(02)

(03)

No processo de tradução representado acima, as etapas que estão numeradas representam,

respectivamente, as seguintes operações, funções ou estados:

A)

B)

C)

D)

Interpretação

Compilação

Interpretação

Compilação

|

|

|

|

Tradução

Link Edição

Link Edição

Montagem

|

|

|

|

Módulo Executável

Módulo Executável

Módulo de Máquina

Módulo Binário

| Sistema Operacional

| Biblioteca de funções

| Biblioteca do Sistema

| Corretor da Linguagem

11. A etapa de maior criatividade no desenvolvimento de um programa é a da:

A) Codificação e compilação

B) Concepção do Algoritmo

C) Execução e testes

D) Avaliação e Documentação

12. Dentre os registradores de uma CPU, aqueles cuja finalidade é, respectivamente, a de conter: o

endereço da próxima instrução; o endereço inicial da pilha; o endereço inicial do segmento de

código (arquitetura Intel); os flags referentes ao estado corrente do processo e a instrução corrente,

são conhecidos pelas siglas:

A) IR / BP / SS / SW / II

B) IR / SP / CS / FR / PC

C) PC / BP / SS / PSW / RI

D) PC / SP / CS / PSW / IR

13. A instrução corrente precisa ser decodificada para ser executada, ação feita:

A) pela Unidade Aritmética e Lógica da CPU

B) pela Unidade de Controle da CPU

C) pelo compilador

D) pelo sistema operacional

14. Na estratégia de hierarquia de memória, os objetivos buscados com a introdução das memórias

cache e virtual, são, respectivamente:

A) aumentar a confiabilidade / ampliar a portabilidade

B) melhorar o desempenho / aumentar a capacidade

C) reduzir o tamanho / melhorar o desempenho

D) aumentar a eficácia / melhorar a eficiência

15. Sabendo-se que em um certo computador os buffers MBR(RDM) e MAR(REM) possuem,

respectivamente, 64 e 32bits, e que o acesso a memória é feito apenas em nível de célula completa,

pode-se afirmar que:

A) a capacidade máxima de memória é 24GB

B) a capacidade máxima de memória é 32GB

C) o barramento permite transferir dados de 4 até 6 bytes

D) os registradores internos da UCP, menos o IR, são de 32bits