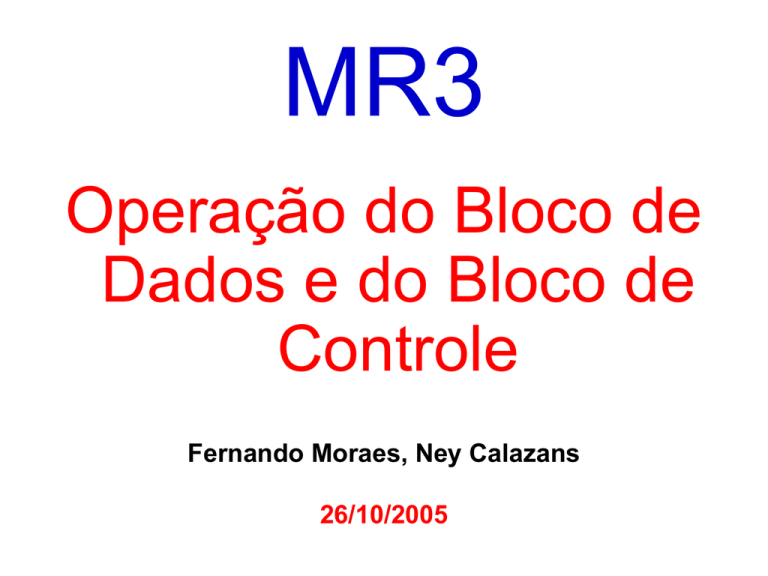

MR3

Operação do Bloco de

Dados e do Bloco de

Controle

Fernando Moraes, Ney Calazans

26/10/2005

Instruções Lógicas e Aritméticas

result

NPC

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

wpc

OP1

IR[20:16]

IR[25:21]

Memória de

Instruções

PC

RIN

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

•

•

•

•

•

•

ADDU

SUBU

AND

OR

XOR

NOR

Rd, Rs, Rt

Rd, Rs, Rt

Rd, Rs, Rt

Rd, Rs, Rt

Rd, Rs, Rt

Rd, Rs, Rt

“0000” &

IR[25:0] & “00”

EXT ZERO

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

Instruções de Deslocamento

result

NPC

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

IR[15:11]

IR[20:16]

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

wpc

OP1

IR[20:16]

IR[25:21]

Memória de

Instruções

PC

RIN

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

•

•

SLL

SRL

“0000” &

IR[25:0] & “00”

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

EXT ZERO

Rd, Rt, shamt

Rd, Rt, shamt

ULA desloca shamt bits

Notar: extensão de

sinal é inútil, mas

usar ela evita

entrada adicional

no mux

Notar: registrador interno

Rs é usado para conter

Rt, pois o interno Rt

compartilha entrada da

ALU com Imed

Instruções Lógicas e Aritméticas Imediatas e LUI

result

NPC

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

wpc

OP1

IR[20:16]

IR[25:21]

Memória de

Instruções

PC

RIN

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

•

•

•

•

•

ADDIU

ANDI

ORI

XORI

LUI

Rt, Rs, Imed16

Rt, Rs, Imed16

Rt, Rs, Imed16

Rt, Rs, Imed16

Rt, imed16

“0000” &

IR[25:0] & “00”

EXT ZERO

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

Não se usa Rs no LUI

SÓ ESTENDE SINAL NA INSTRUÇÃO

ADDIU, OUTRAS ESTENDEM ZERO

Instruções de Leitura da Memória: LBU/LW

result

NPC

RIN

Memória de

Instruções

wpc

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

IR[25:21]

PC

OP1

IR[20:16]

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

“0000” &

IR[25:0] & “00”

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

EXT ZERO

ce rw bw

•

•

LBU

LW

Rt, Imed16(Rs)

Rt, Imed16(Rs)

x“000000” &

data

Atenção: na instrução LBU,

gravar em MDR o byte LSB e

bytes em zero nos 3 MSBs

Mem. de

Dados

MDR

wmdr

Instruções de Escrita na Memória: SB/SW

result

NPC

RIN

Memória de

Instruções

wpc

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

IR[25:21]

PC

OP1

IR[20:16]

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

•

•

SB

SW

“0000” &

IR[25:0] & “00”

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

EXT ZERO

Rt, Imed16(Rs) (ativar bw)

Rt, Imed16(Rs)

Atenção: carga destes três

registradores é útil

Atenção: Write back

não existe nestas

instruções

Instruções de Comparação – SLT/SLTU

result

NPC

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

wpc

OP1

IR[20:16]

IR[25:21]

Memória de

Instruções

PC

RIN

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

•

•

“0000” &

IR[25:0] & “00”

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

EXT ZERO

SLT Rd, Rs, Rt

SLTU Rd, Rs, Rt

IGUAIS ÀS ARITMÉTICAS

Instruções de Comparação Imediatas - SLTI/SLTIU

result

NPC

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

wpc

OP1

IR[20:16]

IR[25:21]

Memória de

Instruções

PC

RIN

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

•

•

“0000” &

IR[25:0] & “00”

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

EXT ZERO

SLTI Rt, Rs, Imed16

SLTIU Rt, Rs, Imed16

CUIDAR: SLT ESTENDE SINAL, SLTIU NÃO

ESTENDE

Instruções de Salto Condicional

result

NPC

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

wpc

OP1

IR[20:16]

IR[25:21]

Memória de

Instruções

PC

RIN

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

Em função da

comparação Rs/Rt,

salta ou não

<< 2

IR[25:0]

IR[15:0]

•

•

•

•

BEQ

BGEZ

BLEZ

BNE

EXT SINAL

Rs, Rt, rótulo

Rs, rótulo

Rs, rótulo

Rs, Rt, rótulo

“0000” &

IR[25:0] & “00”

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

EXT ZERO

Terceiro ciclo: gera o endereço de salto; salta

(escreve no PC) dependendo da

comparação Rs/Rt

Instruções de Salto Incondicional J

result

NPC

IR[20:16]

IR[15:11]

IR[20:16]

Rs

AdRt

banco de

registradores

IR

CY1

AdRs Rd

AdRd

CY2

Rt

outalu

RALU

walu

OP2

Memória de

Dados

wpc

OP1

IR[20:16]

IR[25:21]

Memória de

Instruções

PC

RIN

‘

CY1

PC

dtPC

ce rw

NPC

Endereço

Mem. Dados

IncPC

ALU

+4

data

MDR

wmdr

CY2

instruction

IR[15:0]

EXT SINAL

<< 2

IR[25:0]

IR[15:0]

•

J

Imed26

“0000” &

IR[25:0] & “00”

ce/rw

cte_im

Rs

IMED

CY2

Rt

Rt

comp

I_address

salta

EXT ZERO

Cuidado! Para simplificar este bloco,

concatenação dos 4 bits superiores do PC

para gerar endereço de salto é feita na

ALU.

Exercício

JAL

Imed26

JALR Rd, Rs

JR

Rs

DIV

Lo

wreg

data

result

MULT

wpc

IR[20:16]

IR[25:21]

IR[20:16]

IR

CY1

“11111”

Rs

AdRt

banco de

registradores

IR[15:11]

IR[20:16]

CY2

Rt

AdRd

wreg

I_address

x“000000”

& data

OP1

AdRs Rd

outalu

RALU

walu

OP2

CY2

Memória

de Dados

PC

RIN

D_address

CY1

PC

dtPC

ce rw bw

NPC

ALU

IncPC

Hi

NPC

MDR

wmdr

instruction

IR[15:0]

EXT SINAL

ce/rw

cte_im

Rs

<< 2

IR[25:0]

“0000” &

IR[25:0] & “00”

EXT ZERO

IMED

CY2

Rt

comparador

+4

Memória de

Instruções

•

•

•

Rt

salta

Multiplicação e Divisão

Divisão:

• Usar div/mod

• Consome 3 ciclos de clock para

gravar no Lo e Hi

DIV

Lo

wreg

data

result

MULT

wpc

IR[20:16]

IR[25:21]

IR[20:16]

IR

CY1

“11111”

Rs

AdRt

banco de

registradores

IR[15:11]

IR[20:16]

CY2

Rt

AdRd

wreg

I_address

x“000000”

& data

OP1

AdRs Rd

outalu

RALU

walu

OP2

CY2

Memória

de Dados

PC

RIN

D_address

CY1

PC

dtPC

ce rw bw

NPC

ALU

IncPC

Hi

NPC

MDR

wmdr

instruction

IR[15:0]

EXT SINAL

ce/rw

cte_im

Rs

<< 2

IR[25:0]

“0000” &

IR[25:0] & “00”

EXT ZERO

IMED

CY2

Rt

comparador

+4

Memória de

Instruções

•

Rt

salta

Banco de Registradores

Rd

32

32 registradores de 32 bits

REG0

REG1

REG2

REG3

REG4

...

REG28

REG29

REG30

REG31

clock

reset

32

Rs

AdRs

32

Decodificador

5 32

enable

wreg

32

5

AdRd

AdRt

Rt

Reset=’1’

Reset=’1’

(todos os

registradores

são zerados)

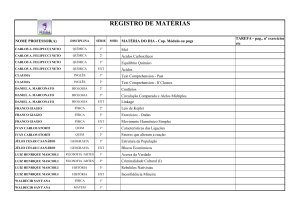

Bloco de Controle

Sidle

Reset=’0’

• Três primeiros ciclos

iguais para todas as

instruções

Sfetch

CY1

Sreg

CY2

Init_mul se

IR=MULTU

IR=MULTU e

End_mul=’0’

Salu

(IR=DIVU) ou (IR=MULTU e End_mul=’1’)

wAlu

wPC

Caso geral

IR=LBU/

LW

Swbk

wreg

wpc

Sld

ce

wmdr

IR=SB/

SW

Sst

rw0, ce, wpc

bw0 se IR=SB

IR =J/JAL/JALR/JR /BEQ/

BGEZ/BLEZ/BNE

Ssalta

wpc

wreg se

IR=JAL/JALR