WECIQ 2006 - Artigos

Uma Unidade Lógica e Aritmética Reversível

Amanda Leonel Nascimento1, Luis A. Brasil Kowada2, Wilson Rosa de Oliveira3

1

Departamento de Sistemas Computacionais, Escola Politécnica de Pernambuco

Universidade de Pernambuco (UPE) – Recife, PE

2

Programa de Engenharia de Sistemas e Computação

Universidade Federal do Rio de Janeiro (UFRJ) - Rio de Janeiro, RJ

3

Departamento de Estatística e Informática,

Universidade Federal Rural de Pernambuco (UFRPE) – Recife, PE

[email protected], [email protected], [email protected]

Abstract. Reversible logic is at the heart of a number of applications in

Unconventional Models of Computing such as Quantum Computing,

Nanotechnology and Optics Computing. The Arithmetic-Logic Unit (ALU)

represents the basis of the processor of any classic (conventional) computer. In this

paper it is proposed a basic reversible ALU (R-ALU) which can be executed in both

classical and quantum computers. The main modules of the reversible unit are

described followed by a discussion of the implications of some applications of

quantum computing in the R-ALU functioning.

Resumo. A lógica reversível tem se tornado a base para um número significativo

de aplicações em Modelos de Computação Não-Convencionais, tais como a

Computação Quântica, a Nanotecnologia e até mesmo a Computação Óptica. De

modo diferente, mas não menos importante, uma Unidade Lógica e Aritmética

(ULA) representa a base do processador de um computador. Neste artigo,

propomos uma ULA reversível (ULA-R) básica, que pode ser utilizada tanto para

construir computadores clássicos reversíveis quanto computadores quânticos.

Descrevemos os principais módulos da unidade reversível e discutimos as

implicações de algumas aplicações quânticas em seu funcionamento.

1. Introdução

A Computação Clássica convencional é expressa, essencialmente, em termos de passos

irreversíveis, ou seja, a partir do resultado de uma operação, não é possível obter os dados de

entrada. Isto acontece, por exemplo, com a operação erase, que apaga um bit de informação,

liberando energia em forma de calor. O circuito, além de aquecer, desperdiça energia

[Vignatti et al. 2004].

Recentemente, a Computação Reversível emergiu como uma alternativa promissora,

por garantir a implementação de circuitos de forma conservativa, isto é, sem perdas de

informação ou calor (na verdade, perdas ínfimas). Circuitos reversíveis tornaram-se motivo

de grande interesse, não apenas pela economia de energia. Com a miniaturização crescente

dos componentes lógicos e a duplicação da velocidade dos computadores aproximadamente a

cada dois anos, estimadas pela Lei de Moore [Nielsen and Chuang 2005], o aquecimento

tornou-se uma barreira para as novas tecnologias, tais como a Nanotecnologia [Vignatti et al.

2004].

149

Além de substituir os circuitos clássicos convencionais, otimizando o consumo de

energia, a principal motivação para a Computação Reversível é o fato de a Computação

Quântica ser inerentemente reversível. Um computador reversível pode seguir a arquitetura

de Von Newmann, contando com uma Unidade Lógica e Aritmética (ULA), uma Unidade de

Controle, registradores, além de outros dispositivos secundários. Mas a forma como estas

unidades são projetadas deve seguir o modelo reversível. Nas seções seguintes, propomos

uma ULA reversível (ULA-R). Inicialmente, apresentamos os modelos de algumas ULAs.

Em seguida, os módulos mais freqüentes, em uma ULA convencional, são descritos

reversivelmente, para a arquitetura apresentada.

2. Unidades Lógicas e Aritméticas

2.1. ULA Clássica (ULA-C)

Em geral, o circuito de uma ULA-C básica tem por entrada duas palavras binárias (conjunto

de bits) A e B de n bits cada, chamadas “operandos”, e um código F de seleção,

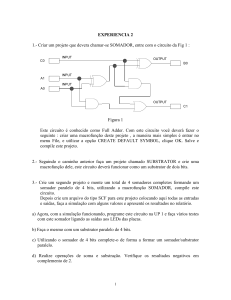

especificando a operação a ser gerada, conforme mostrado na figura 1(a). Sendo x o

tamanho dessa entrada binária F , a função aritmética ou lógica a ser executada é selecionada

entre um conjunto de 2 x possíveis funções implementadas na ULA. A saída mais simples é

composta por uma palavra S = f ( A, B ) , também de n bits, e por um sinal carry-out que é

ativado quando ocorre um “vai-um” no último bit do resultado da operação. Internamente, é

composta por módulos menores, que executam funções específicas.

2.2. ULA Quântica (ULA-Q)

Figura 1. (a) Símbolo padrão para ULA-C convencional na representação em

diagrama de blocos. Setas de espessuras diferentes são utilizadas de acordo

com a quantidade de bits dos dados, indicada pelo valor próximo a elas.

(b) Arquitetura de um computador quântico resistente a falhas, proposto em

[Oskin, Chong and Chuang 2002]. Os bancos de memórias quânticas dão

suporte à conversão eficiente de código. A ULA-Q executa todas as operações

quânticas, auxiliada pelo gerador de q-bit ancilla. O escalonador dinâmico

controla todo o processo.

Também em computadores quânticos, a ULA é a unidade mais importante. Em [Oskin,

Chong and Chuang 2002], os autores propõem uma arquitetura para computadores

quânticos tolerantes a falhas. No coração dessa arquitetura, se encontra a ULA-Q,

150

responsável por realizar operações quânticas de cálculos e correções de erro. Na figura

1(b), é mostrado o diagrama desta arquitetura.

2.3. ULA Reversível (ULA-R)

Semelhante a uma ULA Clássica, mas que pode operar reversivelmente. Propomos uma

Unidade Aritmética e Lógica Reversível básica para inteiros não-negativos. A

representação da ULA-R, tanto para o modelo clássico quanto para o quântico, é dada

na figura 2.

Assim como em [Vedral et al. 1996], as entradas são codificadas na forma

binária na base computacional dos bits selecionados, sendo chamadas de registro. Ou

ainda, quando necessária a representação decimal, utilizaremos a notação de Dirac

adotada por [Mermin 2002]: x n , em que x indicará o valor decimal; e n , o número

de bits do registro. Esta representação é utilizada habitualmente para bits quânticos

(q-bits), mas neste texto será utilizada também para representar bits reversíveis

clássicos, pois, a menos que se explicite o contrário, não há superposição de estados. A

decomposição binária de qualquer registro x n , neste trabalho, é dada por

xn−1 ⊗ xn− 2 … x1 ⊗ x0 , onde ⊗ representa o produto tensorial; e o valor

armazenado equivale a x = 2n−1 xn−1 + 2n− 2 xn− 2 + … + 20 x0 .

Figura 2. Representação em bloco da Unidade Lógica e Aritmética Reversível (ULA-R)

Na ULA-R, assim como na ULA-C, a função a ser gerada é selecionada a partir

de um código F de operações. A tabela 1 ilustra as operações que podem ser executadas

reversivelmente nesta ULA após sua implementação. Sempre é possível a

implementação no qual o resultado ocupa bits diferentes dos utilizados pelos operandos.

Mas é ideal utilizar o menor número de bits.

F0

F1

F2

F3

A

B

0

F0

F1

F2

F3

...

A

n

n

I

¬A

¬B

...

n

A=B

A>B B

S=f(A,B)

Figura 3. Combinação dos diferentes módulos no interior da ULA reversível. O

resultado está representado por uma seqüência de n bits, que, em algumas

operações, podem ocupar o lugar de um dos operandos.

151

Cada função é implementada através de um circuito básico conforme será

mostrado nas seções seguintes. Estes circuitos podem ser concatenados, sendo

controlados pelos bits que definem F , segundo demonstrado na figura 3. Assim,

somente um circuito é ativado por vez.

Tabela 1. Códigos

F de seleção em uma Unidade Lógica Aritmética e Reversível básica

CÓDIGO

SAÍDA

OPERAÇÃO

0000

I

Identidade das entradas

0001

¬A

Inverte A

0010

¬B

Nega B

0011

A∧ B

A AND B

0100

A∨ B

A OR B

0101

A⊕ B

A XOR B

0110

A+ B

A somado a B

0111

B− A

A subtraído de B

1000

A× B

A multiplicado por B

1001

A÷ B

A dividido por B

1010

Rol A

Deslocamento do resgistro A à esquerda

1011

Rol B

Deslocamento do resgistro B à esquerda

1100

Ror A

Deslocamento do resgistro A à direita

1101

Ror B

Deslocamento do resgistro B à direita

1110

A= B

Detector de igualdade entre A e B

1111

A > B, A ≠ B

Comparador entre A e B

3. Módulos Lógicos Básicos Reversíveis

3.1. NOT

A porta clássica NOT, que inverte o bit de entrada, já realiza uma operação unitária. A

generalização para o caso quântico tanto pode ser dada diretamente pelo operador

0 1 quanto através de portas reversíveis controladas que invertam o q-bit alvo. O

X=

1 0

diagrama correspondente a este módulo de n bits é dado na figura 4(a). Note que a

saída substitui o valor de entrada.

3.2. AND

O módulo AND é responsável por realizar a operação AND ( ∧ ) entre os dois operandos,

reversivelmente. Assim, as saídas deste componente assumem o estado 1 apenas

quando os q-bits de entrada também estiverem em 1 . Conforme a figura 4(b), é

possível observar a necessidade de um novo bit para cada operador.

152

3.3. OR

Este módulo efetua a operação OR ( ∨ ) entre os operandos. Podemos construir uma

porta reversível OR a partir da AND vista anteriormente. Seguindo a Lei de De Morgan,

basta aplicarmos o operador X às entradas ou utilizarmos uma porta Toffoli com

controles ativados em 0 e q-bit alvo no estado 1 . Assim como na porta AND, a

simulação de cada porta OR necessita de um novo bit, segundo descrito na figura 4(c).

3.4. XOR

O último módulo lógico básico desta ULA é talvez o mais simples de ser construído

reversivelmente. Pois a implementação da versão reversível da porta XOR, com CNOT,

dispensa q-bits extras. Desta maneira, o componente apenas realiza a operação

exclusive-OR, equivalente à soma módulo 2, entre o par de entrada. O resultado da

operação ocupa um dos bits de entrada na figura 4(d).

Figura 4. Circuitos reversíveis para operações lógicas com operandos de n bits.

(a) Inversor (b) AND (c) OR (d) XOR

4. Módulos Aritméticos Reversíveis

Os módulos reversíveis apresentados nesta seção tratam-se de componentes derivados

dos circuitos propostos por [Vedral et al. 1996] e dos algoritmos aritméticos reversíveis

descritos em [Kowada 2006].

4.1. Somador

Um somador completo clássico (full adder) é um componente que apresenta 3 entradas:

o par a e b a ser somado e a terceira, adicional, chamada de carry-in ( ci ) ou “vem-um”;

e 2 saídas: a soma módulo 2 dos bits de entrada e o carry-out ( co ) ou “vai-um”.

A versão reversível de um somador completo pode ser obtida utilizando-se

apenas 4 portas, conforme o circuito apresentado na figura 5(a). O resultado da

operação substitui um dos operandos. A tabela 2 descreve os passos da evolução deste

módulo.

Assim como no modelo clássico, a expansão deste módulo também pode ser

realizada em série ou cascata, para adição entre operadores de tamanho n . O primeiro

carry-in é inicializado em 0 , e o carry-out da última soma corresponde ao sn do

resultado Soma = sn sn−1 … s0 .

153

Tabela 2. Passos da evolução do circuito somador reversível

P0

P1

P2

P3

P4

ci

ci

ci

ci

ci

a

a

a

a

a

b

b

a⊕b

a⊕b

a ⊕ b ⊕ ci

0

a∧b

a∧b

( a ∧ b ) ⊕ ( ci ∧ ( a ⊕ b ))

( a ∧ b ) ⊕ ( a ∧ c i ) ⊕ ( b ∧ ci )

4.2. Subtrator

O circuito clássico para subtração trata-se de um componente um tanto mais complicado

que o somador (detalhes em [Uyemura 2002]). Em contrapartida, o modelo reversível

de um subtrator é mais simples, basta executarmos o somador de modo reverso.

Compare as figuras 5(a) do somador e 5(b) do subtrator reversíveis.

Este módulo apresenta uma entrada e uma saída adicionais, chamadas borrow,

que assumem o estado 1 quando a subtração realizada equivale a 0 − 1 . (Confira a

evolução para esses valores usando a tabela 3)

Também é possível a expansão em série com subtratores reversíveis para

palavras de tamanho n . O último borrow representa sn - o bit mais significativo do

resultado Subtração = sn sn−1 … s0 , e seu estado em 1 indica resultado negativo da

operação. Neste caso, a saída da subtração equivale a 2n +1 − ( A − B ) [Kowada 2006].

Tabela 3. Passos da evolução do circuito subtrator reversível

P0

P1

P2

P3

P4

ci

ci

ci

ci

ci

a

a

a

a

a

b

ci ⊕ b

ci ⊕ b

a ⊕ ci ⊕ b

a ⊕ b ⊕ ci

0

0

ci ∧ ( ci ⊕ b )

( ci ∧ ci ) ⊕ ( b ∧ ci )

ci ⊕ ( b ∧ ci )

Figura 5. (a) Somador Completo (b) Subtrator reversível

4.3. Multiplicador

Existem poucos algoritmos eficientes, clássicos ou reversíveis, como o Karatsuba

[Kowada et al 2006] e o de Booth [Vargas 2004]. Para o circuito multiplicador desta

ULA-R, utilizamos o algoritmo padrão para multiplicação reversível, descrito em

154

[Kowada 2006]. É possível construí-lo a partir de somadores controlados, que realizam

a soma se o estado do controle for 1 , ou retornam o segundo operando caso contrário

(confira a figura 6).

Figura 6. Esquema em blocos do circuito MULT1 apresentado em [Kowada 2006],

executando a . b , sendo

b = bn-1 … b0 . Algumas linhas de entrada de cada

somador são agrupadas em uma única linha de saída.

Iniciamos a primeira soma controlada com os estados 20. a e 0 . Se b0 = 1 ,

a operação é realizada, e o resultado, 20. a - equivalente a a multiplicado por b0 será o segundo operando do próximo somador. Quando bi = 0 , a multiplicação

prossegue com o resultado anterior ao somador controlado por bi , uma vez que o

segundo operando é simplesmente repassado quando o controle não é ativado.

4.4. Divisor

Também aqui utilizamos o algoritmo para divisão reversível descrito em [Kowada

2006], uma das únicas literaturas a tratar do modelo reversível desta operação.

Basicamente, a idéia deste circuito divisor de a m por b n é fazer determinadas

subtrações sucessivas (confira a figura 7).

Figura 7. Circuito divisor reversível de a por b . O registrador quântico do

quociente é obtido pelo produto tensorial

x m − n ⊗ x m − n − 1 ⊗ … ⊗ x0 . E a

saída inferior equivale ao resto da divisão [Kowada 2006].

155

Iniciamos subtraindo 2m − n . b de a . É aplicado um CNOT com controle ativado

pelo estado 0 no carry-out da operação. Desta forma, quando co = 0 (isto é,

operando inferior maior ou igual ao seguinte), o q-bit mais significativo do quociente

passa para o estado 1 e a subtração é mantida. O resultado dessa operação segue no

lugar do operando inferior da próxima. De outro modo, quando co = 1 (isto é,

operando inferior menor que o superior), o q-bit seguinte do quociente mantém-se no

estado 0 , e a subtração é desfeita pelo somador com controle ativado pelo estado 0 .

O resultado prossegue até o final da divisão, quando o último estado do registro do

quociente é gerado e, enfim: Y = a − b (2m − n xm − n + 2m − n−1 xm − n−1 + … + 2 x1 + x0 ) .

5. Módulos Lógicos Reversíveis

5.1. Detector de Igualdade

A versão clássica deste módulo trata-se de um componente responsável por detectar, bit

a bit, a igualdade entre duas palavras de n bits cada. Utiliza-se a função exclusive-NOR

1 se ai = bi

0 se ai ≠ bi

(XNOR) como função de equivalência, uma vez que: ai ⊕ bi =

O módulo reversível pode ser construído com portas CNOTs seguidas por uma

porta Toffoli generalizada, ativada nos estados 0 , segundo a figura 8a. A evolução do

módulo é dada na tabela 8b ao lado.

P0

a0

a0

b0

a0 ⊕ b0

an−1

an−1

bn−1

an−1 ⊕ bn −1

a0 ⊕ b0 ∧ … ∧ an−1 ⊕ bn −1

0

(a)

P1

(

)

(

)

(b)

Figura 8. (a) Módulo detector de igualdade reversível. (b) Evolução do circuito.

5.2. Comparador

Semelhante ao módulo anterior, o comparador é um sistema combinacional que indica a

relação entre as magnitudes das palavras de entrada. Propomos a implementação de um

comparador reversível que revela se A > B . E acrescentamos uma última porta, para

indicar se A ≠ B , conforme a figura 9. Pois, segundo o subtrator B − A , quando A > B ,

o estado do último borrow mede 1 . Assim, utilizaremos o módulo da subtração para

auxiliar esta operação.

156

Figura 9. Rede de comparadores reversíveis. Se todas as subtrações

correspondentes resultarem no estado

0 , as duas palavras não são diferentes.

5.3. Rotate Left Logical ( ROL)

Os dois últimos módulos apresentados executam o deslocamento de bits em um registro

clássico, para campos adjacentes. Quando a operação deve ocorrer da direita para a

esquerda, o componente a ser ativado é o Rotate Left Logical. Propomos utilizar um

conjunto de CNOTs que simule o operador SWAP. Assim, o módulo ROL pode ser

implementado com o trio controlado conforme a ordem descrita na figura 10(a).

5.4. Rotate Right Logical (ROR)

No Rotate Right Logical clássico, uma posição de bit recebe o conteúdo do seu vizinho

imediatamente à esquerda, efetuando o deslocamento dos dados para a direita. Um ROR

também pode ser implementado com o trio SWAP, entretanto, em ordem inversa,

apresentada na figura 10(b).

Figura 10. Deslocadores de registro: (a) Rotate Left Logical (b) Rotate Right Logical

157

6. Aplicações Quânticas

Até agora, tratamos apenas reversivelmente da ULA proposta, isto é, ainda não foram

exploradas propriedades inerentes à Computação Quântica, tais como superposição de

estados ou processamento paralelo.

Em [Milosav 2005], é demonstrada uma maneira típica de operar um somador

quântico, explorando a capacidade de um computador quântico permanecer

simultaneamente em estados distintos superpostos. Entretanto, o autor apresenta um

circuito que, erroneamente, gera o estado equivalente a (a ∧ b) ⊕ (a ∧ b ) ⊕ (b ∧ ci )

para a saída carry-out, comprometendo a operação. Obviamente, utilizamos aqui o

somador desta ULA-R (confira a operação corrigida na figura 11). E, preparando-se

com uma transformação Walsh-Hadamard (mais detalhes em [Nielsen and Chuang

2005]) os q-bits das n entradas a serem somadas, o somador quântico é capaz de

realizar a soma de todos os 2n estados superpostos possíveis.

Figura 11. Somador quântico completo operando sobre a superposição dos 4

estados possíveis nas entradas a serem adicionadas. Ψ é o estado do registro

AB ; e Φ , o estado dos 4 possíveis resultados [Milosav 2005].

Se, entretanto, aplicamos o paralelismo quântico a uma das entradas de um

multiplicador reversível, podemos obter, executando apenas uma única vez a ULA-R,

todos os múltiplos desejados da entrada não superposta inicialmente. O registrador

quântico resultante da multiplicação contém todos os múltiplos de A n na forma

A.x

n+ m

, sendo x

bits assim como B

m

m

, isto é, qualquer número que possa ser representado por m q-

.

Essas aplicações sugerem um possível ganho exponencial de velocidade de

processamento da ULA-R proposta sobre uma ULA-C. Contudo, de acordo com os

princípios de medição na Mecânica Quântica, ao medirmos uma saída superposta, todo

o paralelismo é desfeito, e apenas um dos resultados será obtido ao final, perdendo-se os

demais. E, tratando-se de uma transformação Hadamard, as probabilidades dos

resultados são iguais entre si, possibilitando a saída de qualquer um desses na medição.

Para que o paralelismo quântico tenha uma utilidade imediata em uma ULA-R,

necessitamos da aplicação de algoritmos quânticos apropriados para a extração dos

resultados desejados no processamento maciço quântico. Alguns poucos circuitos

158

aritméticos eficientes, como em [Draper 2000] e [Nguyen 2001], têm sido obtidos com

sucesso quanto às melhorias resultantes de aplicações quânticas, em geral, graças à

Transformada de Fourier Quântica.

7. Conclusões

A Computação Reversível tornou-se indispensável para muitos dos modelos de

computação em desenvolvimento, como a Computação Quântica. Apresentamos uma

ULA reversível básica, semelhante às clássicas, que opera de modo reversível. Contudo,

nem sempre a conversão direta pode produzir um menor circuito ou mais eficiente.

A partir dos módulos reversíveis apresentados, é possível construir uma ULA

que execute em um computador quântico. Porém, dado o estado atual das pesquisas em

Computação Quântica, nos encontramos um tanto distantes da implementação de uma

ULA inerentemente quântica, como Chuang idealizou em [Oskin, Chong and Chuang

2002], realizando até mesmo a correção de erros em um processador quântico. Uma

ULA-R é certamente mais um passo até essa realização.

Referências

Draper, T.G. (2000). Addition on a Quantum Computer. ArXiv:quant-ph/ 0008033.

Kowada, L. A. B. (2006). Construção de Algoritmos Reversíveis e Quânticos. Tese de

Doutorado – COPPE / UFRJ.

Kowada, L. A. B.; Portugal, R. Figueiredo and C. M. H. de (2006). Reversible

Karatsuba. Journal of Universal Computer Science.vol 12, n. 5 pg 499-511.

Mermin, N.D. (2002). From Cbits to Qbits: Teaching Computer Scientists Quantum

Mechanics. ArXiv:quant-ph/ 0207118.

Milosav, M.U. (2005). Quantum Circuits Engineering: Efficient Simulation and

Reconfigurable Quantum Hardware. Ph.D. Thesis. Universitatea “Politehnica” Din

Timiçoara, România.

Nielsen, M. A. and Chuang, I. L. (2005). Computação Quântica e Informação Quântica.

Bookman.

Nguyen, A. Q. (2001). Optimal Reversible Quantum Circuit for Multiplication. Tech

Reports/2004010, v.2.

Oskin, M.; Chong, F. T. and Chuang, I. L. (2002). A Practical Architecture for Reliable

Quantum Computers. IEEE Computer, Jan.2002. pg 79-87

Thapliyal, H and Srinivas, M. B. (2006). Novel Reversible Multiplier Architecture

Using Reversible TSG Gate. Center for VLSI and Embedded Technologies.

Uyemura, J. P. (2002). Sistemas Digitais – Uma Abordagem Integrada. Thomson

Learning.

Vargas, F. L. (2004). Engenharia de Computadores I. DEE, PUCRS.

Vedral, V.; Barenco, A. and Ekert, A. (1996). Quantum Networks for Elementary

Arithmetic Operations. Physical Review A, v.54, n.1.

159

Vignatti, A. L.; Netto Summa, F. and Bittencourt, L. F. (2004). Uma Introdução à

Computação Quântica. Departamento de Informática. UFPR.

160