UNIVERSIDADE FEDERAL DE PERNAMBUCO

DEPARTAMENTO DE ELETRÔNICA E SISTEMAS

1o semestre de 2008

04/abr/2008

ES271 Técnicas Digitais

Prof. João Paulo Cerquinho Cajueiro

Aluno:

1o Exercı́cio Escolar

1. Projete um circuito utilizando transistores MOS canal n e p que realize a

função ou exclusivo de duas entradas utilizando o menor número possı́vel de

transistores. O circuito não deve consumir potência estática (ou seja, para

as entradas estáticas em nı́veis 0 ou 1 válidos, não há corrente no circuito).

Considere que 0 lógico é uma tensı̈¿ 12 o entre 0V e 0,5V e 1 lógico é uma

tensão entre 4,5V e 5V.

2. Em geral, por questões de fabricação, os circuitos TTL conseguem ter maior

corrente na saı́da quando a mesma é 0 lógico do que quando é 1 lógico. Por

essa razão muitos circuitos para acender leds (diodos emissores de luz) são

montados de forma que o led acenda em zero, não em 1.

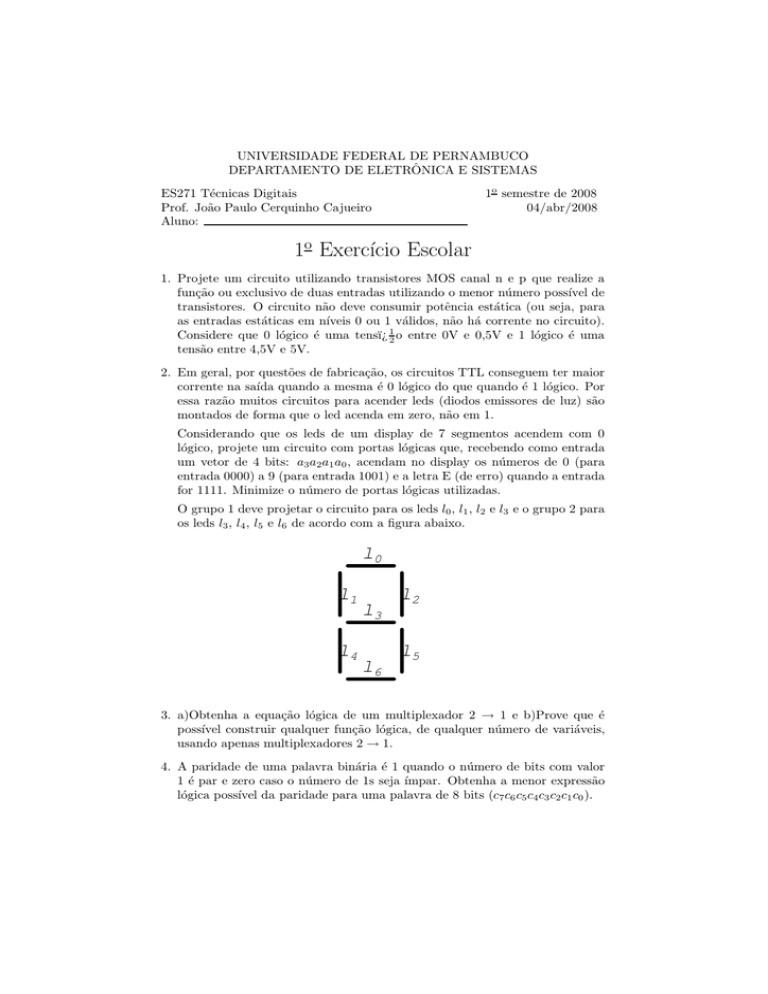

Considerando que os leds de um display de 7 segmentos acendem com 0

lógico, projete um circuito com portas lógicas que, recebendo como entrada

um vetor de 4 bits: a3 a2 a1 a0 , acendam no display os números de 0 (para

entrada 0000) a 9 (para entrada 1001) e a letra E (de erro) quando a entrada

for 1111. Minimize o número de portas lógicas utilizadas.

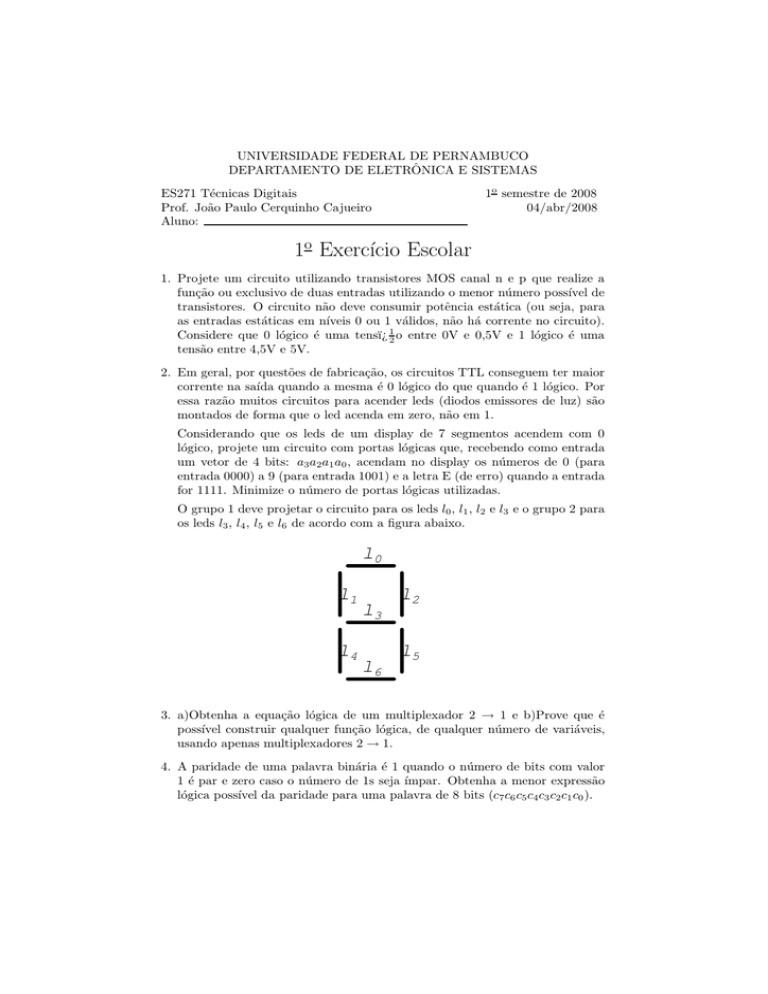

O grupo 1 deve projetar o circuito para os leds l0 , l1 , l2 e l3 e o grupo 2 para

os leds l3 , l4 , l5 e l6 de acordo com a figura abaixo.

l0

l2

l1

l3

l5

l4

l6

3. a)Obtenha a equação lógica de um multiplexador 2 → 1 e b)Prove que é

possı́vel construir qualquer função lógica, de qualquer número de variáveis,

usando apenas multiplexadores 2 → 1.

4. A paridade de uma palavra binária é 1 quando o número de bits com valor

1 é par e zero caso o número de 1s seja ı́mpar. Obtenha a menor expressão

lógica possı́vel da paridade para uma palavra de 8 bits (c7 c6 c5 c4 c3 c2 c1 c0 ).

UNIVERSIDADE FEDERAL DE PERNAMBUCO

DEPARTAMENTO DE ELETRÔNICA E SISTEMAS

ES271 Técnicas Digitais

Prof. João Paulo Cerquinho Cajueiro

Aluno:

2o semestre de 2008

10/set/2008

1o Exercı́cio Escolar

1. Uma função é auto-dual se ela for igual ao seu dual (ou seja, se após trocar

toda soma por multiplicação e vice-versa e todo 0 por 1 e vice-versa se chega à

mesma função). Mostre que, para qualquer função f (com dual fd ) e qualquer

variável A, a função g = A · f + A · fd é auto-dual.

2. A função voto majoritário de n variáveis M (x1 , x2 , ..., xn ) é 1 sempre que a

maioria das variáveis é 1 e zero caso contrário. Implemente a função voto

majoritário de 3 variáveis em lógica MOS complementar utilizando o menor

número de transistores possı́vel.

3. Implemente a função voto majoritário de 4 variáveis utilizando o menor

número de multiplexadores 2 para 1 possı́vel.

4. Para representar números de 0 a 9 a notação mais comum é a BCD, onde 4

bits b3 b2 b1 b0 tem peso 8 (b3 ), 4 (b2 ), 2 (b1 ) e 1 (b0 ) e os sı́mbolos de 1010 a

1111 não são válidos. Existem, porém, outras notações, como a 4221, onde

ba tem peso 4, bb e bc têm, ambos, peso 2 e bd tem peso 1; nesta notação

todos os sı́mbolos são válidos.

a) Obtenha as equações minimizadas na forma soma de produtos dos bits

b3 , b2 , b1 , b0 em função de ba , bb , bc , bd . Ex.: b0 = bd

b) Obtenha as equações minimizadas na forma produto de somas dos bits

ba , bb , bc , bd em função de b3 , b2 , b1 , b0 . Ex.: bd = b0

UNIVERSIDADE FEDERAL DE PERNAMBUCO

DEPARTAMENTO DE ELETRÔNICA E SISTEMAS

1o semestre de 2009

03/abr/2009

ES271 Técnicas Digitais

Prof. João Paulo Cerquinho Cajueiro

Aluno:

1o Exercı́cio Escolar

1. Dada a tabela abaixo, obtenha as equações de s2 , s1 e s0 em função de

a1 , a0 , b1 e b0 na forma minimizada de produto de somas.

a1

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

a0

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

b1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

b0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

s2

0

0

0

0

0

0

0

1

0

0

1

1

0

1

1

1

s1

0

0

1

1

0

1

1

0

1

1

0

0

1

0

0

1

s0

0

1

0

1

1

0

1

0

0

1

0

1

1

0

1

0

2. Implemente s2 e s1 com o menor número de transistores MOS possı́vel.

3. A função voto majoritário de n entradas é 1 se mais do que n/2 entradas

for 1 e 0 caso contrário. Prove que é possı́vel implementar qualquer função

lógica usando apenas a função voto majoritário de 3 entradas e inversores.

4. Obtenha as equações minimizadas na forma soma de produtos para d3 ,

d2 , d1 e d0 de acordo com a tabela abaixo.

Índice

0

1

2

3

4

5

6

7

8

9

Entrada

c4 c3 c2 c1 c0

00011

00101

00110

01001

01010

01100

10001

10010

10100

11000

outros

Saı́da

d3 d2 d1 d0

0000

0001

0010

0110

0100

0101

0110

0111

1000

1001

xxxx