CIRCUITOS COMBINATÓRIOS BÁSICOS

T.1 - INTRODUÇÃO

A velocidade de um sistema digital

velocidade com que operam as portas.

depende

da

A velocidade de uma porta depende do atraso de

propagação tpd(propagation-delay time).

As portas electrónicas têm tempos de atraso da

ordem dos nanossegundos (10-9).

1

Cronologia

Data

Componente

até 1955

1955-1965

desde 1965

válvula

transistor

circuito integrado

Observações

grandes dimensões e consumo

encapsulamento individual

encapsulamento de transistores

e resistências

Nomenclatura

SSI - Integração em pequena escala (até 12 portas)

MSI - Integração em escala média (12 a 99 portas)

LSI - Integração em larga escala (100 a 1000

portas)

VLSI - Integração em muito larga escala (1000 a

1.000.000 portas)

ULSI - Integração em ultra larga escala (mais de

1.000.000 portas)

2

Circuitos combinatórios - são circuitos cujas

saídas dependem apenas das entradas actuais, não

tendo relação com a história passada do sistema.

T.2 - FAMÍLIAS DE CIRCUITOS LÓGICOS

As famílias de circuitos

distinguem-se por:

lógicos

integrados

tipo de semicondutor utilizado;

forma como os semicondutores são ligados.

3

Família CMOS

Utiliza transistores CMOS (Complementary MetalOxide Semiconductor). É utilizada em SSI, MSI,

LSI, VLSI e ULSI.

Tem um consumo muito baixo, mas tem tempos de

propagação elevados.

4

Família ECL (Emitter-Coupled Logic)

Utiliza transistores bipolares que têm tempos de

propagação mais baixos que os CMOS. É usada em SSI

e MSI.

É bastante rápida, mas tem consumos mais elevados

que a família CMOS.

É de difícil utilização devido à sua rapidez.

5

Família TTL (Transistor-Transistor Logic)

Utiliza transistores bipolares. É a família mais

usada para SSI e MSI.

Tem duas séries:

54 - para fins militares e

74 - para fins industriais.

6

BICMOS (BIPOLAR + CMOS)

É uma evolução com integração

transistores bipolares e CMOS.

das

famílias

de

Tem um baixo consumo e um tempo de resposta baixo.

No entanto, ocupa uma área elevada, pelo que não é

utilizado em circuitos integrados com grande nível

de integração como os microporcessadores.

7

T.3 - SÉRIE TTL

Pode baixar-se o atraso de propagação tpd de uma

porta lógica à custa de um maior consumo de

energia, isto é, utilizando transistores que

consumam mais potência.

A série TTL utiliza transistores bipolares normais

- mais lentos, e transistores do tipo Schottky mais rápidos, em diversas gamas de potência.

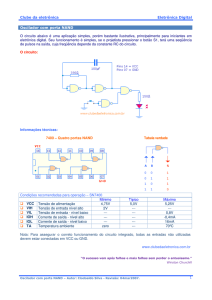

Características típicas da família 54/74 SSI

Série

54LS/74LS

54L/74L

54S/74S

54/74

54H/74H

Tipo

de

transistor

e

potência

Schottky, baixa potência

Comum, baixa potência

Schottky, potência normal

Comum, potência normal

Comum, alta potência

Atraso

propagação, ns

9,5

33

3

10

6

de

Dissipação

potência, mW

2

1

19

10

22

de

Produto

velocidadepotência, pJ

19

33

57

100

132

8

Capacidade de saída (fan-out)

O fan-out mede a capacidade que a saída de uma

porta tem de accionar entradas de outras portas.

Cada porta tem uma corrente máxima de saída. Por

outro lado, cada porta necessita de uma corrente

mínima de entrada para ser accionada. O fan-out

dá-nos a indicação de quantas entradas podem ser

accionadas por uma única saída.

Na família TTL, entre portas da mesma série, o

fan-out é 10 para portas das séries standard e de

alta potência, e 20 para as séries de baixa

potência.

Entre séries de famílias diferentes é necessário

garantir que as correntes de entrada não superam a

corrente de saída.

9

Margem de ruído

A tensão de alimentação para circuitos da família

TTL é 5 V. Isto significa que todas as tensões

estão no intervalo de 0 a 5 V.

Uma saída que esteja no nível lógico 0 está a

drenar corrente das portas às quais está ligada,

aumentando a sua tensão de saída (> 0 V).

Uma saída que esteja no nível lógico 1 está a

fornecer corrente às portas a que está ligada,

baixando deste modo a sua tensão de saída (< 5 V).

De qualquer modo o fabricante garante que a tensão

baixa nunca sobe acima dos 0,4 V e que a tensão

alta nunca desce abaixo dos 2,4 V.

10

Por outro lado uma tensão menor ou igual a 0,8 V é

sempre interpretada como um 0 lógico e uma tensão

superior a 2 V é sempre interpretada como um nível

lógico 1.

Definem-se VOH, VOL, VIH e VIL

VOH - tensão mínima de saída que

para o nível alto

VOL - tensão máxima de saída que

para o nível baixo

VIH - tensão mínima que a porta

nível alto

VIL - tensão máxima que a porta

nível baixo

a porta fornece

a porta fornece

reconhece como

reconhece como

11

Na figura seguinte mostra-se

tensões para a família 54/74.

V (saída)

o

valor

destas

V (entrada)

VCC

VCC=5,0V

Saída

alta

Entrada

alta

1

VOH=2,4V

VIH=2,0V

VIL=0,8V

VOL=0,4V

<0,2V

Saída

baixa

0

Entrada

baixa

Fig 80

12

Gráfico de entrada-saída de uma porta TTL para o

pior caso

VO,V

2,4

1

0,4V

0

0,4

0,8

1,4

2,0

2,4

VI,V

Fig 81

13

A margem de ruído para o nível 0 é 0=VILVOL=0,4V. Esta margem garante que uma saída 0 é

sempre

reconhecida

desde

que

o

ruído

não

ultrapasse 0=0,4V.

De forma idêntica, a margem de ruído para o nível

1 é 1=VIH-VOH=0,4V e garante que uma saída 1 é

sempre

reconhecida

desde

que

o

ruído

não

ultrapasse 1=0,4V.

14

T.4 - FAMÍLIA CMOS

A tensão de alimentação para circuitos da família

CMOS pode variar no intervalo de 5 a 15 V.

A corrente de entrada requerida por uma porta é da

ordem de 1pA enquanto que a corrente de saída é da

ordem de 1 mA, dando origem a um fan-out enorme.

Para as mesmas condições de carga e tensão de

alimentação que as portas TTL, uma porta CMOS tem

um atraso de propagação da ordem de 50 a 100 ns.

As margens de ruído para uma alimentação de 5 V

são de cerca de 1 V e aumentam para tensões de

alimentação maiores.

15

O

consumo

de

potência

numa

porta

CMOS

é

praticamente nulo quando a saída se mantém fixa.

No entanto se a saída varia com uma frequência de

105 Hz (para uma carga típica de 50 pF) a potência

dissipada é da ordem de 0,2 mW.

TTL e CMOS no mesmo circuito

Quando uma porta TTL acciona portas CMOS, não

existem problemas de fan-out, mas o nível de saída

VOH não é suficientemente alto para a porta CMOS.

Quando uma porta CMOS acciona portas TTL, os

níveis de saída são adequados, mas a corrente de

saída fornecida pela porta CMOS pode não ser

suficiente.

Neste

caso

interpõem-se

portas

especiais denominadas buffers.

16

As séries CMOS mais utilizadas são a 4000, a

54HC/74HC e a 54HCT/74HCT. Estas duas mais rápidas

que a primeira, e a última com níveis TTL.

17

T.5 - FAMÍLIA ECL

A família ECL opera com uma tensão de alimentação

negativa de -5,2 V. Os níveis lógicos são portanto

negativos, tendo os valores de -0,75 V e -1,6V.

O fan-out é da ordem de 25, e as margens de ruído

da ordem de 0,3 V.

O atraso de propagação é da ordem de 2 ns, e a

dissipação da ordem de 25 mW por porta.

Existem ainda as séries ECL II e ECL III com

atrasos da ordem de 4 ns e 1 ns, respectivamente.

18

T.6 - INTERRUPTOR LÓGICO

O transistor funciona como interruptor lógico,

conduzindo ou não, por acção de uma tensão de

entrada.

5 V

5 V

R

R

V

H

ou

V

O

R

V

L

S

V

H

ou

Interruptor

lógico

V

L

0 V

A

V

O

0 V

S=A

Fig 82

19

Quando a tensão de entrada for VL, o transistor

não conduz, pelo que a saída é VO=VCC.

Quando a tensão de entrada for VH, o transistor

conduz, pelo que a saída é VO=0 V.

20

O circuito de 2 interruptores da figura seguinte

representa uma porta NOR com equação S = A + B .

5 V

R

S

A

B

A

B

S

0

0

1

0

1

0

1

0

0

1

1

0

A

S

B

Fig 83

21

wired AND

O circuito da figura seguinte representa também

uma porta NOR com equação S = A + B.

Sem a ligação entre as duas saídas, os

circuitos individuais teriam à saída, A e B.

dois

A ligação a tracejado, na prática, adicionou um

circuito AND, pois S = A . B A + B .

Esta ligação tem o nome de wired-AND, e apenas

pode ser feita utilizando circuitos com open

collector (colector aberto).

22

Se houver muitas portas e todas as chaves

estiverem

ligadas

excepto

uma,

a

corrente

originada pela pequena resistência equivalente

queima o transistor que está a conduzir.

Em

circuitos

que

utilizem

portas

com

open

collector a resistência (única) é dimensionada à

medida.

23

5 V

R

S

wired AND

A

A

S=A.B

0 V

B

S=A.B

5 V

R

S

B

0 V

Fig 84

24

T.7 - SAÍDA TOTEM-POLE

Sob um ponto de vista, o interruptor lógico é a

configuração ideal para a saída de uma porta TTL.

Quando a saída está no nível baixo a porta deve

consumir a corrente do circuito accionado.

Efectivamente, quando a saída está a 0, o

interruptor está fechado e a corrente escoa-se

para a massa.

Quando a saída está no nível alto, a porta deve

fornecer corrente ao circuito accionado.

Efectivamente quando a saída está a 1, o

interruptor está aberto e a corrente flui através

da resistência.

25

Vcc

Vcc

R

R

Consome

corrente

Vcc

Fornece

corrente

R

C

Fig 85

26

Contudo o interruptor lógico tem capacidades

parasitas, que diminuem a velocidade da porta.

Estas

capacidades

não

causam

problemas

na

transição da saída de 1 para 0, pois o condensador

descarrega rapidamente quando o interruptor fecha.

Os problemas aparecem na transição da saída de 0

para 1, pois a saída só atinge o valor alto depois

do condensador carregar, e este carrega lentamente

devido à resistência.

27

Para

aumentar

a

velocidade

de

carga

do

condensador, a resistência pode ser substituída

por um segundo interruptor.

Esta nova configuração tem o nome de saída totem-pole.

Quando A tem o nível baixo, I1 está aberto e I2

fechado, estando a saída no nível alto.

Quando A tem o nível alto, I1 está fechado e I2

aberto, estando a saída no nível baixo.

28

Vcc

I2

S=A

A

I1

Fig 86

29

T.8 - SAÍDA TRI-STATE

A configuração com saída totem-pole pode

modificada, obtendo-se o circuito seguinte.

ser

Vcc

I2

S=A

A

I1

enable

Fig 87

30

Quando a linha de controle (enable) estiver a 1, o

circuito funciona exactamente como a configuração

totem-pole, ou seja, a entrada A é negada à saída.

Quando a linha de controle estiver a 0, os 2

interruptores ficam abertos, e a saída fica

totalmente desligada do circuito (estado de alta-impedância).

Desta forma a saída S pode tomar 3 estados: os 2

estados lógicos 0 e 1 (quando enable=1), e o

estado de alta-impedância (quando enable=0).

31

Saídas de 3 estados

enable

enable

enable

Fig 88

32

T.9 - EXEMPLOS DE PORTAS EM CIRCUITOS INTEGRADOS

Porta NOR tripla de 3 entradas ('27) e porta NAND

de 13 entradas ('133)

14

13

12

11

10

9

8

V

CC

16

15

14

13

12

11

10

V

CC

GND

1

9

2

3

4

5

6

7

GND

1

2

3

4

5

6

7

8

Fig 89

33

Porta NAND quad de 2 entradas ('00) e buffer quad

com saída tri-state (3 estados) activada a 0

('125)

14

13

12

11

10

9

8

V

CC

14

13

12

11

10

9

V

CC

GND

1

8

2

3

4

5

6

7

GND

1

2

3

4

5

6

7

Fig 90

34

Porta XOR quad ('136) (os asteriscos indicam

saídas com open collector) e porta AOI (AND-ORINVERT) dupla de 2 e 3 entradas ('51).

14

13

12

11

10

9

8

14

V

CC

13

12

11

10

9

V

CC

*

*

*

*

GND

1

8

2

3

4

5

6

7

GND

1

2

3

4

5

6

7

Fig 91

35

O apóstrofo antes do número do dispositivo

representa a família e a série. Por exemplo, a

porta 74LS02 é representada por '02.

Os termos duplo, triplo, quad e hex indicam que o

circuito integrado contém 2, 3, 4 ou 6 unidades

idênticas independentes, respectivamente.

Alguns circuitos integrados SSI

Número do circuito

'00

'02

'03

'04

'05

'08

Descrição

NAND quad de 2 entradas

NOR quad de 2 entradas

NAND quad de 2 entradas open collector

Inversor hex

Inversor hex open collector

AND quad de 2 entradas

36

'09

'20

'21

'27

'30

'32

'37

'38

'51

'126

'136

AND quad de 2 entradas open collector

NAND duplo de 4 entradas

AND duplo de 4 entradas

NOR triplo de 3 entradas

NAND de 8 entradas

OR quad de 2 entradas

Buffer NAND quad de 2 entradas

Buffer NAND quad de 2 entradas - o. c.

AOI duplo de 2 e 3 entradas

Buffer quad com saída tri-state

XOR quad de 2 entradas open collector

37

Os buffers são portas que podem drenar mais

corrente do que as portas normais e são usados

quando é necessário um fan-out superior ao normal.

A maioria dos circuitos SSI têm 14 pinos, mas

algumas têm 16 pinos.

Dois pinos são usados para alimentação: VCC e GND.

38

T.10 - SINAIS DE CONTROLE

Uma entrada de uma porta pode ser considerada como

uma linha de controle.

E

E

A

B

C

S

A

B

C

S

Fig 92

Na porta NAND da figura, a entrada E (enable)

funciona como linha de controle e as entradas A, B

e C funcionam como linhas de dados.

Quando E=1, a porta funciona como um NAND de 3

entradas.

Quando E=0, a porta tem sempre saída 1, ou seja, é

independente da variação das entradas A, B e C.

39

Na porta NOR da figura, a entrada E (enable)

funciona também como linha de controle e as

entradas A, B e C como linhas de dados.

Quando E=0, a porta funciona como um NOR de 3

entradas.

Quando E=1, a porta tem sempre saída 0, ou seja, é

independente da variação das entradas A, B e C.

No caso da porta NAND a linha enable é activa a 1.

No caso da porta NOR a linha enable é activa a 0.

Quando se trata de circuitos MSI e LSI, não é

possível nem necessário mostrar todas as portas

incluídas no circuito.

40

Neste

caso

utilizam-se

representar os circuitos.

rectângulos

para

Para indicar que uma linha de controle é activa a

0 coloca-se o símbolo de inversão no ponto em que

a linha de controle entra no rectângulo.

41

EN

EN

S

S

A

B

C

A

B

C

EN

EN

S

A

B

C

S

A

B

C

Fig 93

42

O primeiro circuito tem a linha EN (enable) activa

a 1.

O segundo circuito tem a linha EN activa a 0. Dá a

ideia (errada) de que existe um inversor entre a

linha de controle e o circuito.

O terceiro circuito é idêntico ao segundo mas

utiliza uma simbologia mais recente. Deste modo já

não persiste a ideia de que existe um inversor à

entrada do circuito.

O quarto circuito tem a linha EN activa a 0.

Difere dos outros circuitos na saída que é agora

activa a 0.

43

As terminologias EN e EN têm uma limitação. Se no

diagrama de um circuito lógico aparecer uma linha

EN , e se esta linha for aplicada a um circuito

desconhecido, não é possível saber se EN é uma

linha de controle activa a 0 ou a negação de uma

linha de controle activa a 1.

nível ALTO (H)

nível BAIXO (L)

t1

t2

t3

tempo

Fig 94

44

Se o sinal EN tiver a forma da figura acima, será

impossível saber se o circuito é accionado no

intervalo t1 a t2 ou no intervalo t2 a t3.

Para

contornar

terminologia

esta

limitação

utiliza-se

a

EN-H para substituir EN

EN-L para substituir EN

EN-H é um sinal activo e tem o valor 1 quando

estiver a 1 (high).

EN-L é um sinal activo e tem o valor 1 quando

estiver a 0 (low).

45

Se o sinal de controle disponível for EN-H e a

entrada do circuito precisar de um sinal de

controle activo a 0 (símbolo inversor ou meia-flecha) é necessário interpor um inversor para

inverter os níveis de tensão.

Tem-se:

EN-H = EN -L = EN - L

EN-L = EN -H = EN - H

46

T.11 - DESCODIFICADORES E CODIFICADORES

T.11.1 - Descodificador

Um descodificador é um circuito com n entradas e

2n saídas. Para cada combinação das entradas,

apenas uma saída está activa.

47

A1 A0

O0

O1

O2

A1 A0

O0

0

0

1

0

1

1

0

1

1

O1

O2

O3

1

1

1

O3

Fig 95

Um descodificador com 2 entradas tem 4 saídas.

48

Para

a

combinação

O1=O2=O3=0.

Para a combinação

O0=O2=O3=0, etc.

A1=A0=0,

A1=0

e

tem-se

A0=1,

tem-se

O0=1

O1=1

e

e

Nem sempre é necessário apresentar as 2n saídas do

descodificador.

No caso de um descodificador de BCD (Binary Coded

Decimal) para decimal, há 4 entradas mas apenas 10

saídas são relevantes, pois as combinações de 10 a

15 nunca são apresentadas à entrada.

49

Descodificador de 3 entradas por 8 saídas ('138)

A

A

2

O

7

A

1

O

6

E

0

O

5

O

4

1

O

3

E E

2 3

O

2

O

1

O

0

Fig 96

50

O descodificador '138 é fabricado num CI com 16

pinos, sendo a massa o pino 8 e VCC o pino 16.

Utiliza portas NAND em vez de portas AND pelo que

as saídas são activas a 0.

Cada porta NAND tem 4 entradas, sendo uma das

entradas de controle (enable). A entrada de

controle tem a função E1.E2.E3. Estas linhas de

controle podem ser utilizadas para permitir o

funcionamento do descodificador para uma linha de

controle a 1, a 0 ou para uma combinação

específica dos sinais de controle.

51

Símbolo lógico do descodificador '138

E

A

O

A

0

0

O

1

A

1

O

2

1

E E

2 3

EN

2

O

3

O

4

O

5

O

6

O

7

Fig 97

52

Simbolismo funcional para o '138

1

2

3

X/Y

1

2

4

0

1

2

3

4

4

5

6

&

5

EN

6

7

15

14

13

12

11

10

9

7

Fig 98

53

No simbolismo funcional, os pinos de entrada estão

à esquerda e os de saída estão à direita. Os

números na extremidade dos pinos são os números

dos pinos.

A indicação X/Y mostra que o circuito é um

descodificador.

As entradas de endereço são os pinos 1, 2 e 3 que

têm os pesos 1, 2 e 4, como indicado.

A soma dos pinos de entrada activos determina a

saída que é activada. As saídas são activas a 0.

O rectângulo marcado com & e a indicação EN

mostram que as entradas 4, 5 e 6 são operadas por

uma porta AND (&) de forma a obter-se a linha

enable.

54

Descodificador duplo de 2 entradas para 4 saídas,

com unidades independentes ('139)

2

3

1

2

X/Y

0

1

2

1

14

13

EN

3

X/Y

1

2

0

1

4

5

6

7

12

11

10

2

15

EN

3

9

Fig 99

55

Descodificador duplo de 2 entradas para 4 saídas,

com entradas compartilhadas ('155)

13

3

Entradas partilhadas

pelas 2 unidades

abaixo

X/Y

1

2

0

1

2

1

&

2

EN

3

0

1

14

15

&

2

EN

3

7

6

5

4

9

10

11

12

Fig 100

56

T.11.2 - Codificador

Um codificador executa a função inversa à do

descodificador.

As entradas de um codificador têm a característica

de, em cada instante, apenas uma estar activa.

A cada linha de entrada corresponde uma palavra de

código nas linhas de saída.

Tabela de verdade de um codificador possível de 4

entradas

I3 I2 I1 I0 A7 A6 A5 A4 A3 A2 A1 A0

1

1

0

1

1

0

0

1

1

1

1

1

0

1

0

1

0

1

1

0

1

1

1

1

0

1

0

1

1

1

0

0

1

1

0

1

57

Circuito

correspondente

I3 I2 I1 I0

A0

A1

A2

A3

A4

A5

A6

A7

Fig 101

58

Codificador de 8 entradas para 3 saídas

I7 I6 I5 I4 I3 I2 I1 I0

EN

A0

A1

A2

Fig 102

59

T.12 - CONVERSORES

Um conversor é um circuito utilizado para fazer a

tradução entre 2 códigos.

Pode ser construído ligando um descodificador e um

codificador em cascata.

Uma palavra de código à entrada do descodificador

é representada por uma linha à saída deste.

Esta linha é codificada no circuito codificador

dando origem à nova palavra de código.

60

Z

0

Z

1

A

0

A

1

Codificador

Descodificador

A

m-1

B

0

B

1

Z

n-1

B

k-1

Fig 103

Um exemplo interessante de conversor de código é o

tradutor de BCD para display de 7 segmentos.

61

Display de 7 segmentos (exemplos)

a

b

c

d

e

f

g

a

a

f

g

e

d

b

b

c

c

g

a

b

b

c

c

d

Fig 104

O display tem 7 linhas, correspondendo cada uma a

um segmento.

Cada segmento é um LED (díodo emissor de luz).

O conversor de código terá 4 linhas de entrada e 7

de saída.

62

Para a combinação de entrada A3A2A1A0=0000,

deverá activar os segmentos a, b, c, d, e e f.

Para a combinação de entrada

deverá activar os segmentos b e c.

A3A2A1A0=0001,

Para a combinação de entrada A3A2A1A0=0010,

deverá activar os segmentos a, b, d, e e g.

Etc.

O conversor "BCD - display de 7 segmentos" é

normalmente denominado apenas por descodificador.

Existe em CI na família TTL com as designações

'46, '47, '48 e '49, com saídas em open collector

ou não.

63

T.13 - MULTIPLEXERS E DEMULTIPLEXERS

T.13.1 - Multiplexer

Um multiplexer executa a função indicada na figura

abaixo.

A partir de uma entrada de controle, o comutador

lógico selecciona apenas uma entrada para ser

ligada à saída.

Comutador lógico

Fig 105

64

Implementação de um multiplexer com portas

S1 S0

I0

I1

Z

I2

I3

Fig 106

65

Neste multiplexer, uma das quatro entradas é

seleccionada, e ligada à saída, a partir de duas

entradas de controle.

Para 2n entradas

controle.

são

necessárias

n

linhas

de

As linhas de selecção determinam qual das portas

AND é seleccionada.

Caso A1=A0=0, a porta seleccionada é a primeira,

logo a entrada I0 é colocada à saída do AND.

As outras portas AND têm sempre saída 0, pelo que

a porta OR, ou seja a saída do multiplexer,

reflecte apenas o valor da entrada I0.

66

Caso A1=0 e A0=1, a porta seleccionada é a

segunda, logo a entrada I1 é colocada à saída do

AND.

As outras portas AND têm sempre saída 0, pelo que

a porta OR, ou seja a saída do multiplexer,

reflecte apenas o valor da entrada I1.

Etc.

67

O multiplexer é uma estrutura AND-OR a 2 níveis,

logo pode ser usado como gerador de funções.

Cada uma das entradas corresponde a um termo

mínimo. A entrada I0 corresponde ao termo m0. A

entrada I1 corresponde ao termo m1. Etc.

As variáveis da função são as linhas de selecção

do multiplexer.

68

Exemplo

Para gerar a função Z=S 1+S1S 0 expande-se Z em

termos mínimos Z = S 1(S0+S 0)+S1S 0 = S 1S0+S 1S 0+S1S 0 =

m1+m0+m2

Basta então colocar as entradas I1=I0=I2=1 e I3=0

para se obter a função pretendida.

69

Multiplexer

de 8

entradas

('251)

S

2

S

1

S

0

I

7

I

6

I

5

I

4

W=Y

I

I

3

Y

2

I

1

I

0

G

Fig 107

70

Símbolo lógico do multiplexer tipo '151

11

10

9

S

S

S

7

4

G

I

3

0

I

2

1

I

1

2

I

15 14 13 12

3

I

4

I I

I

5

6

7

0

1

2

W

Y

6

5

Fig 108

71

Símbolo funcional do multiplexer '251

7

11

10

9

4

3

2

1

15

14

13

12

MUX

EN

0

1

2

0

1

2

3

4

5

6

7

0

G7

5

6

Fig 109

72

Os CI's '151 e '251 são multiplexers de 8 entradas

para 1 saída, diferenciando-se pelo facto do '251

possuir saídas tri-state.

Ambos possuem uma linha de enable activa a 0, e 2

linhas à saída sendo uma o complemento da outra.

No símbolo funcional, a palavra MUX identifica o

multiplexer.

O pino 7 é a entrada de enable.

Os triângulos nas saídas (pinos 5 e 6) indicam que

estas são do tipo tri-state.

As entradas de selecção (pinos 9, 10 e 11) têm os

pesos 20, 21 e 22.

73

O símbolo 0 indica que as entradas de selecção

7

podem seleccionar, consoante o seu valor, as

entradas de dados numeradas de 0 a 7.

O símbolo G indica que entre as entradas de dados

e as entradas de selecção existe uma dependência

do tipo AND.

74

Multiplexer

quádruplo de 2 para

1 ('157)

15

1

2

3

5

6

11

10

14

13

MUX

EN

0

0

G1

0

1

4

0

1

7

0

1

9

0

1

12

Fig 110

O CI '157 contém 4 multiplexers de 2 entradas para

1 saída. Tem uma única entrada de selecção e

apenas uma linha de enable para os 4 multiplexers.

75

T.13.2 - Demultiplexer

O

demultiplexer

tem

a

função

inversa

multiplexer, como mostra a figura abaixo.

do

Comutador lógico

Fig 111

Num demultiplexer, a entrada pode ser ligada a

qualquer das saídas, dependendo apenas das linhas

de selecção que fazem o papel de comutador lógico.

76

Estrutura lógica de um multiplexer de 1 entrada

para 4 saídas

S1 S0

00

O0

01

O1

10

O2

11

O3

I

Fig 112

77

T.14 - SISTEMAS DE MULTIPLEXAGEM

Os

multiplexers

são

muito

utilizados

em

telecomunicações, para transmitir numa única linha

a informação proveniente de várias linhas de

dados.

78

Sistema

(TDM)

de

multiplexagem

I

0

I

1

por

divisão

tempo

O

0

O

1

D

Multiplexer

do

Demultiplexer

I

n-1

O

n-1

Selecção

Ck

Selecção

Fig 113

Apenas é necessária uma linha de dados para

transmitir a informação correspondente às n linhas

de entrada. A linha Ck sincroniza as entradas de

selecção.

79